This file provides firmware functions to manage the following functionalities of the Window watchdog (WWDG) peripheral: More...

Go to the source code of this file.

Macros | |

| #define | BIT_MASK ((uint8_t)0x7F) |

| #define | CFR_W_MASK ((uint32_t)0xFFFFFF80) |

| #define | CFR_WDGTB_MASK ((uint32_t)0xFFFFFE7F) |

Functions | |

| void | WWDG_ClearFlag (void) |

| Clears Early Wakeup interrupt flag. More... | |

| void | WWDG_DeInit (void) |

| Deinitializes the WWDG peripheral registers to their default reset values. More... | |

| void | WWDG_Enable (uint8_t Counter) |

| Enables WWDG and load the counter value. More... | |

| void | WWDG_EnableIT (void) |

| Enables the WWDG Early Wakeup interrupt(EWI). More... | |

| FlagStatus | WWDG_GetFlagStatus (void) |

| Checks whether the Early Wakeup interrupt flag is set or not. More... | |

| void | WWDG_SetCounter (uint8_t Counter) |

| Sets the WWDG counter value. More... | |

| void | WWDG_SetPrescaler (uint32_t WWDG_Prescaler) |

| Sets the WWDG Prescaler. More... | |

| void | WWDG_SetWindowValue (uint8_t WindowValue) |

| Sets the WWDG window value. More... | |

Detailed Description

This file provides firmware functions to manage the following functionalities of the Window watchdog (WWDG) peripheral:

- Version

- V1.1.1

- Date

- 04-April-2014

- Prescaler, Refresh window and Counter configuration

- WWDG activation

- Interrupts and flags management

*

==============================================================================

##### WWDG features #####

==============================================================================

[..] Once enabled the WWDG generates a system reset on expiry of a programmed

time period, unless the program refreshes the counter (downcounter)

before to reach 0x3F value (i.e. a reset is generated when the counter

value rolls over from 0x40 to 0x3F).

[..] An MCU reset is also generated if the counter value is refreshed

before the counter has reached the refresh window value. This

implies that the counter must be refreshed in a limited window.

[..] Once enabled the WWDG cannot be disabled except by a system reset.

[..] WWDGRST flag in RCC_CSR register can be used to inform when a WWDG

reset occurs.

[..] The WWDG counter input clock is derived from the APB clock divided

by a programmable prescaler.

[..] WWDG counter clock = PCLK1 / Prescaler.

[..] WWDG timeout = (WWDG counter clock) * (counter value).

[..] Min-max timeout value @36MHz (PCLK1): ~114us / ~58.3ms.

##### How to use this driver #####

==============================================================================

[..]

(#) Enable WWDG clock using RCC_APB1PeriphClockCmd(RCC_APB1Periph_WWDG, ENABLE)

function.

(#) Configure the WWDG prescaler using WWDG_SetPrescaler() function.

(#) Configure the WWDG refresh window using WWDG_SetWindowValue() function.

(#) Set the WWDG counter value and start it using WWDG_Enable() function.

When the WWDG is enabled the counter value should be configured to

a value greater than 0x40 to prevent generating an immediate reset.

(#) Optionally you can enable the Early wakeup interrupt which is

generated when the counter reach 0x40.

Once enabled this interrupt cannot be disabled except by a system reset.

(#) Then the application program must refresh the WWDG counter at regular

intervals during normal operation to prevent an MCU reset, using

WWDG_SetCounter() function. This operation must occur only when

the counter value is lower than the refresh window value,

programmed using WWDG_SetWindowValue(). - Attention

© COPYRIGHT 2014 STMicroelectronics

Licensed under MCD-ST Liberty SW License Agreement V2, (the "License"); You may not use this file except in compliance with the License. You may obtain a copy of the License at:

http://www.st.com/software_license_agreement_liberty_v2

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

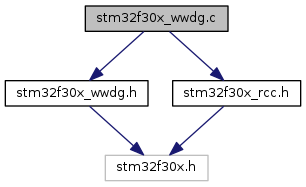

Definition in file stm32f30x_wwdg.c.