Modules | |

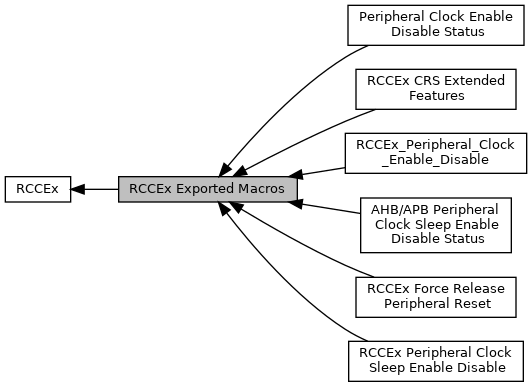

| RCCEx_Peripheral_Clock_Enable_Disable | |

| Enables or disables the AHB/APB peripheral clock. | |

| Peripheral Clock Enable Disable Status | |

| Get the enable or disable status of the AHB/APB peripheral clock. | |

| RCCEx Force Release Peripheral Reset | |

| Forces or releases AHB/APB peripheral reset. | |

| RCCEx Peripheral Clock Sleep Enable Disable | |

| Enables or disables the AHB/APB peripheral clock during Low Power (Sleep) mode. | |

| AHB/APB Peripheral Clock Sleep Enable Disable Status | |

| Get the enable or disable status of the AHB/APB peripheral clock during Low Power (Sleep) mode. | |

| RCCEx CRS Extended Features | |

Macros | |

| #define | __HAL_RCC_ADC_CONFIG(__ADCCLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_ADCSEL, (uint32_t)(__ADCCLKSource__)) |

| Macro to configure the ADC clock. More... | |

| #define | __HAL_RCC_ADC_CONFIG(__ADCCLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_ADCSEL, (uint32_t)(__ADCCLKSource__)) |

| Macro to configure the ADC clock. More... | |

| #define | __HAL_RCC_CEC_CONFIG(__CEC_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_CECSEL, (uint32_t)(__CEC_CLKSOURCE__)) |

| Macro to configure the CEC clock (CECCLK). More... | |

| #define | __HAL_RCC_CEC_CONFIG(__CECCLKSource__) MODIFY_REG(RCC->D2CCIP2R, RCC_CDCCIP2R_CECSEL, (uint32_t)(__CECCLKSource__)) |

| macro to configure the CEC clock (CECCLK). More... | |

| #define | __HAL_RCC_CEC_CONFIG(__CECCLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_CECSEL, (uint32_t)(__CECCLKSource__)) |

| macro to configure the CEC clock (CECCLK). More... | |

| #define | __HAL_RCC_CLK48_CONFIG(__CLK48_SOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_CK48MSEL, (uint32_t)(__CLK48_SOURCE__)) |

| Macro to configure the CLK48 source (CLK48CLK). More... | |

| #define | __HAL_RCC_CLKP_CONFIG(__CLKPSource__) MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_CKPERSEL, (uint32_t)(__CLKPSource__)) |

| Macro to configure the CLKP : Oscillator clock for peripheral. More... | |

| #define | __HAL_RCC_CLKP_CONFIG(__CLKPSource__) MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_CKPERSEL, (uint32_t)(__CLKPSource__)) |

| Macro to configure the CLKP : Oscillator clock for peripheral. More... | |

| #define | __HAL_RCC_CRS_CLEAR_FLAG(__FLAG__) |

| #define | __HAL_RCC_CRS_CLEAR_FLAG(__FLAG__) |

| #define | __HAL_RCC_CRS_CLEAR_IT(__INTERRUPT__) |

| #define | __HAL_RCC_CRS_CLEAR_IT(__INTERRUPT__) |

| #define | __HAL_RCC_CRS_DISABLE_IT(__INTERRUPT__) CLEAR_BIT(CRS->CR, (__INTERRUPT__)) |

| Disable the specified CRS interrupts. More... | |

| #define | __HAL_RCC_CRS_DISABLE_IT(__INTERRUPT__) CLEAR_BIT(CRS->CR, (__INTERRUPT__)) |

| Disable the specified CRS interrupts. More... | |

| #define | __HAL_RCC_CRS_ENABLE_IT(__INTERRUPT__) SET_BIT(CRS->CR, (__INTERRUPT__)) |

| Enable the specified CRS interrupts. More... | |

| #define | __HAL_RCC_CRS_ENABLE_IT(__INTERRUPT__) SET_BIT(CRS->CR, (__INTERRUPT__)) |

| Enable the specified CRS interrupts. More... | |

| #define | __HAL_RCC_CRS_GET_FLAG(__FLAG__) (READ_BIT(CRS->ISR, (__FLAG__)) == (__FLAG__)) |

| Check whether the specified CRS flag is set or not. More... | |

| #define | __HAL_RCC_CRS_GET_FLAG(__FLAG__) (READ_BIT(CRS->ISR, (__FLAG__)) == (__FLAG__)) |

| Check whether the specified CRS flag is set or not. More... | |

| #define | __HAL_RCC_CRS_GET_IT_SOURCE(__INTERRUPT__) ((READ_BIT(CRS->CR, (__INTERRUPT__)) != 0U) ? SET : RESET) |

| Check whether the CRS interrupt has occurred or not. More... | |

| #define | __HAL_RCC_CRS_GET_IT_SOURCE(__INTERRUPT__) ((READ_BIT(CRS->CR, (__INTERRUPT__)) != 0U) ? SET : RESET) |

| Check whether the CRS interrupt has occurred or not. More... | |

| #define | __HAL_RCC_DFSDM1_CONFIG(__DFSDM1CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL, (uint32_t)(__DFSDM1CLKSource__)) |

| Macro to configure the DFSDM1 clock. More... | |

| #define | __HAL_RCC_DFSDM1_CONFIG(__DFSDM1CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL, (uint32_t)(__DFSDM1CLKSource__)) |

| Macro to configure the DFSDM1 clock. More... | |

| #define | __HAL_RCC_FMC_CONFIG(__FMCCLKSource__) MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_FMCSEL, (uint32_t)(__FMCCLKSource__)) |

| macro to configure the FMC clock source. More... | |

| #define | __HAL_RCC_FMC_CONFIG(__FMCCLKSource__) MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_FMCSEL, (uint32_t)(__FMCCLKSource__)) |

| macro to configure the FMC clock source. More... | |

| #define | __HAL_RCC_GET_ADC_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_ADCSEL))) |

| Macro to get the ADC clock source. More... | |

| #define | __HAL_RCC_GET_ADC_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_ADCSEL))) |

| Macro to get the ADC clock source. More... | |

| #define | __HAL_RCC_GET_CEC_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_CECSEL))) |

| macro to get the CEC clock source. More... | |

| #define | __HAL_RCC_GET_CEC_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_CECSEL))) |

| macro to get the CEC clock source. More... | |

| #define | __HAL_RCC_GET_CEC_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_CECSEL))) |

| macro to get the CEC clock source. More... | |

| #define | __HAL_RCC_GET_CLK48_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_CK48MSEL))) |

| macro to get the CLK48 source. More... | |

| #define | __HAL_RCC_GET_CLKP_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIPR, RCC_CDCCIPR_CKPERSEL))) |

| Macro to get the Oscillator clock for peripheral source. More... | |

| #define | __HAL_RCC_GET_CLKP_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIPR, RCC_CDCCIPR_CKPERSEL))) |

| Macro to get the Oscillator clock for peripheral source. More... | |

| #define | __HAL_RCC_GET_DFSDM1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL))) |

| Macro to get the DFSDM1 clock source. More... | |

| #define | __HAL_RCC_GET_DFSDM1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL))) |

| Macro to get the DFSDM1 clock source. More... | |

| #define | __HAL_RCC_GET_FMC_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIPR, RCC_CDCCIPR_FMCSEL))) |

| macro to get the FMC clock source. More... | |

| #define | __HAL_RCC_GET_FMC_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIPR, RCC_CDCCIPR_FMCSEL))) |

| macro to get the FMC clock source. More... | |

| #define | __HAL_RCC_GET_I2C1235_SOURCE() ((uint32_t)(READ_BIT(RCC->D2CCIP2R, RCC_D2CCIP2R_I2C1235SEL))) |

| macro to get the I2C1/2/3/5* clock source. More... | |

| #define | __HAL_RCC_GET_I2C1235_SOURCE() ((uint32_t)(READ_BIT(RCC->D2CCIP2R, RCC_D2CCIP2R_I2C1235SEL))) |

| macro to get the I2C1/2/3/5* clock source. More... | |

| #define | __HAL_RCC_GET_I2C123_SOURCE __HAL_RCC_GET_I2C1235_SOURCE |

| #define | __HAL_RCC_GET_I2C123_SOURCE __HAL_RCC_GET_I2C1235_SOURCE |

| #define | __HAL_RCC_GET_I2C1_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C1SEL))) |

| Macro to get the I2C1 clock source. More... | |

| #define | __HAL_RCC_GET_I2C1_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

| macro to get the I2C1 clock source. More... | |

| #define | __HAL_RCC_GET_I2C1_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

| macro to get the I2C1 clock source. More... | |

| #define | __HAL_RCC_GET_I2C2_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C2SEL))) |

| Macro to get the I2C2 clock source. More... | |

| #define | __HAL_RCC_GET_I2C2_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

| macro to get the I2C2 clock source. More... | |

| #define | __HAL_RCC_GET_I2C2_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

| macro to get the I2C2 clock source. More... | |

| #define | __HAL_RCC_GET_I2C3_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C3SEL))) |

| macro to get the I2C3 clock source. More... | |

| #define | __HAL_RCC_GET_I2C3_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

| macro to get the I2C3 clock source. More... | |

| #define | __HAL_RCC_GET_I2C3_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

| macro to get the I2C3 clock source. More... | |

| #define | __HAL_RCC_GET_I2C4_SOURCE() ((uint32_t)(READ_BIT(RCC->D3CCIPR, RCC_D3CCIPR_I2C4SEL))) |

| macro to get the I2C4 clock source. More... | |

| #define | __HAL_RCC_GET_I2C4_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_I2C4SEL))) |

| macro to get the I2C4 clock source. More... | |

| #define | __HAL_RCC_GET_I2C4_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C4SEL))) |

| macro to get the I2C4 clock source. More... | |

| #define | __HAL_RCC_GET_I2SCLKSOURCE() (READ_BIT(RCC->CFGR, RCC_CFGR_I2SSRC)) |

| Macro to Get I2S clock source selection. More... | |

| #define | __HAL_RCC_GET_LPTIM1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_LPTIM1SEL))) |

| macro to get the LPTIM1 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_LPTIM1SEL))) |

| macro to get the LPTIM1 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM1_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_LPTIM1SEL))) |

| macro to get the LPTIM1 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM2_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM2SEL))) |

| macro to get the LPTIM2 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM2_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM2SEL))) |

| macro to get the LPTIM2 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM345_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM3SEL))) |

| macro to get the LPTIM3/4/5 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM345_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM3SEL))) |

| macro to get the LPTIM3/4/5 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM3_SOURCE __HAL_RCC_GET_LPTIM345_SOURCE |

| macro to get the LPTIM3 clock source. More... | |

| #define | __HAL_RCC_GET_LPTIM3_SOURCE __HAL_RCC_GET_LPTIM345_SOURCE |

| macro to get the LPTIM3 clock source. More... | |

| #define | __HAL_RCC_GET_LPUART1_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_LPUART1SEL))) |

| macro to get the LPUART1 clock source. More... | |

| #define | __HAL_RCC_GET_LPUART1_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_LPUART1SEL))) |

| macro to get the LPUART1 clock source. More... | |

| #define | __HAL_RCC_GET_RNG_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_RNGSEL))) |

| macro to get the RNG clock source. More... | |

| #define | __HAL_RCC_GET_RNG_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_RNGSEL))) |

| macro to get the RNG clock source. More... | |

| #define | __HAL_RCC_GET_SAI1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SAI1SEL))) |

| Macro to get the SAI1 clock source. More... | |

| #define | __HAL_RCC_GET_SAI1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SAI1SEL))) |

| Macro to get the SAI1 clock source. More... | |

| #define | __HAL_RCC_GET_SAI1_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR1, RCC_DCKCFGR1_SAI1SEL))) |

| Macro to get the SAI1 clock source. More... | |

| #define | __HAL_RCC_GET_SAI2_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR1, RCC_DCKCFGR1_SAI2SEL))) |

| Macro to get the SAI2 clock source. More... | |

| #define | __HAL_RCC_GET_SDMMC1_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_SDMMC1SEL))) |

| macro to get the SDMMC1 clock source. More... | |

| #define | __HAL_RCC_GET_SDMMC_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIPR, RCC_CDCCIPR_SDMMCSEL))) |

| Macro to get the SDMMC clock. More... | |

| #define | __HAL_RCC_GET_SDMMC_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIPR, RCC_CDCCIPR_SDMMCSEL))) |

| Macro to get the SDMMC clock. More... | |

| #define | __HAL_RCC_GET_SPDIFRX_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SPDIFSEL))) |

| Macro to get the SPDIFRX clock source. More... | |

| #define | __HAL_RCC_GET_SPDIFRX_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SPDIFSEL))) |

| Macro to get the SPDIFRX clock source. More... | |

| #define | __HAL_RCC_GET_SPI123_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI123SEL))) |

| Macro to get the SPI1/2/3 clock source. More... | |

| #define | __HAL_RCC_GET_SPI123_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI123SEL))) |

| Macro to get the SPI1/2/3 clock source. More... | |

| #define | __HAL_RCC_GET_SPI1_SOURCE __HAL_RCC_GET_SPI123_SOURCE |

| Macro to get the SPI1 clock source. More... | |

| #define | __HAL_RCC_GET_SPI1_SOURCE __HAL_RCC_GET_SPI123_SOURCE |

| Macro to get the SPI1 clock source. More... | |

| #define | __HAL_RCC_GET_SPI2_SOURCE __HAL_RCC_GET_SPI123_SOURCE |

| Macro to get the SPI2 clock source. More... | |

| #define | __HAL_RCC_GET_SPI2_SOURCE __HAL_RCC_GET_SPI123_SOURCE |

| Macro to get the SPI2 clock source. More... | |

| #define | __HAL_RCC_GET_SPI3_SOURCE __HAL_RCC_GET_SPI123_SOURCE |

| Macro to get the SPI3 clock source. More... | |

| #define | __HAL_RCC_GET_SPI3_SOURCE __HAL_RCC_GET_SPI123_SOURCE |

| Macro to get the SPI3 clock source. More... | |

| #define | __HAL_RCC_GET_SPI45_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI45SEL))) |

| Macro to get the SPI4/5 clock source. More... | |

| #define | __HAL_RCC_GET_SPI45_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI45SEL))) |

| Macro to get the SPI4/5 clock source. More... | |

| #define | __HAL_RCC_GET_SPI4_SOURCE __HAL_RCC_GET_SPI45_SOURCE |

| Macro to get the SPI4 clock source. More... | |

| #define | __HAL_RCC_GET_SPI4_SOURCE __HAL_RCC_GET_SPI45_SOURCE |

| Macro to get the SPI4 clock source. More... | |

| #define | __HAL_RCC_GET_SPI5_SOURCE __HAL_RCC_GET_SPI45_SOURCE |

| Macro to get the SPI5 clock source. More... | |

| #define | __HAL_RCC_GET_SPI5_SOURCE __HAL_RCC_GET_SPI45_SOURCE |

| Macro to get the SPI5 clock source. More... | |

| #define | __HAL_RCC_GET_SPI6_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_SPI6SEL))) |

| Macro to get the SPI6 clock source. More... | |

| #define | __HAL_RCC_GET_SPI6_SOURCE() ((uint32_t)(READ_BIT(RCC->SRDCCIPR, RCC_SRDCCIPR_SPI6SEL))) |

| Macro to get the SPI6 clock source. More... | |

| #define | __HAL_RCC_GET_SWPMI1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SWPSEL))) |

| Macro to get the SWPMI1 clock source. More... | |

| #define | __HAL_RCC_GET_SWPMI1_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_SWPSEL))) |

| Macro to get the SWPMI1 clock source. More... | |

| #define | __HAL_RCC_GET_UART4_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_UART4SEL))) |

| macro to get the UART4 clock source. More... | |

| #define | __HAL_RCC_GET_UART4_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART4 clock source. More... | |

| #define | __HAL_RCC_GET_UART4_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART4 clock source. More... | |

| #define | __HAL_RCC_GET_UART5_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_UART5SEL))) |

| macro to get the UART5 clock source. More... | |

| #define | __HAL_RCC_GET_UART5_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART5 clock source. More... | |

| #define | __HAL_RCC_GET_UART5_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART5 clock source. More... | |

| #define | __HAL_RCC_GET_UART7_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_UART7SEL))) |

| macro to get the UART7 clock source. More... | |

| #define | __HAL_RCC_GET_UART7_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART7 clock source. More... | |

| #define | __HAL_RCC_GET_UART7_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART7 clock source. More... | |

| #define | __HAL_RCC_GET_UART8_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_UART8SEL))) |

| macro to get the UART8 clock source. More... | |

| #define | __HAL_RCC_GET_UART8_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART8 clock source. More... | |

| #define | __HAL_RCC_GET_UART8_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the UART8 clock source. More... | |

| #define | __HAL_RCC_GET_USART16910_SOURCE() ((uint32_t)(READ_BIT(RCC->D2CCIP2R, RCC_D2CCIP2R_USART16910SEL))) |

| macro to get the USART1/6/9* /10* clock source. More... | |

| #define | __HAL_RCC_GET_USART16910_SOURCE() ((uint32_t)(READ_BIT(RCC->D2CCIP2R, RCC_D2CCIP2R_USART16910SEL))) |

| macro to get the USART1/6/9* /10* clock source. More... | |

| #define | __HAL_RCC_GET_USART16_SOURCE __HAL_RCC_GET_USART16910_SOURCE |

| #define | __HAL_RCC_GET_USART16_SOURCE __HAL_RCC_GET_USART16910_SOURCE |

| #define | __HAL_RCC_GET_USART1_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_USART1SEL))) |

| macro to get the USART1 clock source. More... | |

| #define | __HAL_RCC_GET_USART1_SOURCE __HAL_RCC_GET_USART16_SOURCE |

| macro to get the USART1 clock source. More... | |

| #define | __HAL_RCC_GET_USART1_SOURCE __HAL_RCC_GET_USART16_SOURCE |

| macro to get the USART1 clock source. More... | |

| #define | __HAL_RCC_GET_USART234578_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_USART234578SEL))) |

| macro to get the USART2/3/4/5/7/8 clock source. More... | |

| #define | __HAL_RCC_GET_USART234578_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_USART234578SEL))) |

| macro to get the USART2/3/4/5/7/8 clock source. More... | |

| #define | __HAL_RCC_GET_USART2_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_USART2SEL))) |

| macro to get the USART2 clock source. More... | |

| #define | __HAL_RCC_GET_USART2_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the USART2 clock source. More... | |

| #define | __HAL_RCC_GET_USART2_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the USART2 clock source. More... | |

| #define | __HAL_RCC_GET_USART3_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_USART3SEL))) |

| macro to get the USART3 clock source. More... | |

| #define | __HAL_RCC_GET_USART3_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the USART3 clock source. More... | |

| #define | __HAL_RCC_GET_USART3_SOURCE __HAL_RCC_GET_USART234578_SOURCE |

| macro to get the USART3 clock source. More... | |

| #define | __HAL_RCC_GET_USART6_SOURCE() ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_USART6SEL))) |

| macro to get the USART6 clock source. More... | |

| #define | __HAL_RCC_GET_USART6_SOURCE __HAL_RCC_GET_USART16_SOURCE |

| macro to get the USART6 clock source. More... | |

| #define | __HAL_RCC_GET_USART6_SOURCE __HAL_RCC_GET_USART16_SOURCE |

| macro to get the USART6 clock source. More... | |

| #define | __HAL_RCC_GET_USB_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_USBSEL))) |

| Macro to get the USB clock source. More... | |

| #define | __HAL_RCC_GET_USB_SOURCE() ((uint32_t)(READ_BIT(RCC->CDCCIP2R, RCC_CDCCIP2R_USBSEL))) |

| Macro to get the USB clock source. More... | |

| #define | __HAL_RCC_I2C1235_CONFIG(__I2C1235CLKSource__) MODIFY_REG(RCC->D2CCIP2R, RCC_D2CCIP2R_I2C1235SEL, (uint32_t)(__I2C1235CLKSource__)) |

| macro to configure the I2C1/2/3/5* clock (I2C123CLK). More... | |

| #define | __HAL_RCC_I2C1235_CONFIG(__I2C1235CLKSource__) MODIFY_REG(RCC->D2CCIP2R, RCC_D2CCIP2R_I2C1235SEL, (uint32_t)(__I2C1235CLKSource__)) |

| macro to configure the I2C1/2/3/5* clock (I2C123CLK). More... | |

| #define | __HAL_RCC_I2C123_CONFIG __HAL_RCC_I2C1235_CONFIG |

| #define | __HAL_RCC_I2C123_CONFIG __HAL_RCC_I2C1235_CONFIG |

| #define | __HAL_RCC_I2C1_CONFIG(__I2C1_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C1SEL, (uint32_t)(__I2C1_CLKSOURCE__)) |

| Macro to configure the I2C1 clock (I2C1CLK). More... | |

| #define | __HAL_RCC_I2C1_CONFIG __HAL_RCC_I2C123_CONFIG |

| macro to configure the I2C1 clock (I2C1CLK). More... | |

| #define | __HAL_RCC_I2C1_CONFIG __HAL_RCC_I2C123_CONFIG |

| macro to configure the I2C1 clock (I2C1CLK). More... | |

| #define | __HAL_RCC_I2C2_CONFIG(__I2C2_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C2SEL, (uint32_t)(__I2C2_CLKSOURCE__)) |

| Macro to configure the I2C2 clock (I2C2CLK). More... | |

| #define | __HAL_RCC_I2C2_CONFIG __HAL_RCC_I2C123_CONFIG |

| macro to configure the I2C2 clock (I2C2CLK). More... | |

| #define | __HAL_RCC_I2C2_CONFIG __HAL_RCC_I2C123_CONFIG |

| macro to configure the I2C2 clock (I2C2CLK). More... | |

| #define | __HAL_RCC_I2C3_CONFIG(__I2C3_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C3SEL, (uint32_t)(__I2C3_CLKSOURCE__)) |

| Macro to configure the I2C3 clock (I2C3CLK). More... | |

| #define | __HAL_RCC_I2C3_CONFIG __HAL_RCC_I2C123_CONFIG |

| macro to configure the I2C3 clock (I2C3CLK). More... | |

| #define | __HAL_RCC_I2C3_CONFIG __HAL_RCC_I2C123_CONFIG |

| macro to configure the I2C3 clock (I2C3CLK). More... | |

| #define | __HAL_RCC_I2C4_CONFIG(__I2C4_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C4SEL, (uint32_t)(__I2C4_CLKSOURCE__)) |

| Macro to configure the I2C4 clock (I2C4CLK). More... | |

| #define | __HAL_RCC_I2C4_CONFIG(__I2C4CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_I2C4SEL, (uint32_t)(__I2C4CLKSource__)) |

| macro to configure the I2C4 clock (I2C4CLK). More... | |

| #define | __HAL_RCC_I2C4_CONFIG(__I2C4CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_I2C4SEL, (uint32_t)(__I2C4CLKSource__)) |

| macro to configure the I2C4 clock (I2C4CLK). More... | |

| #define | __HAL_RCC_LPTIM1_CONFIG(__LPTIM1_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_LPTIM1SEL, (uint32_t)(__LPTIM1_CLKSOURCE__)) |

| Macro to configure the LPTIM1 clock (LPTIM1CLK). More... | |

| #define | __HAL_RCC_LPTIM1_CONFIG(__LPTIM1CLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_LPTIM1SEL, (uint32_t)(__LPTIM1CLKSource__)) |

| macro to configure the LPTIM1 clock source. More... | |

| #define | __HAL_RCC_LPTIM1_CONFIG(__LPTIM1CLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_LPTIM1SEL, (uint32_t)(__LPTIM1CLKSource__)) |

| macro to configure the LPTIM1 clock source. More... | |

| #define | __HAL_RCC_LPTIM2_CONFIG(__LPTIM2CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM2SEL, (uint32_t)(__LPTIM2CLKSource__)) |

| macro to configure the LPTIM2 clock source. More... | |

| #define | __HAL_RCC_LPTIM2_CONFIG(__LPTIM2CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM2SEL, (uint32_t)(__LPTIM2CLKSource__)) |

| macro to configure the LPTIM2 clock source. More... | |

| #define | __HAL_RCC_LPTIM345_CONFIG(__LPTIM345CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM3SEL, (uint32_t)(__LPTIM345CLKSource__)) |

| macro to configure the LPTIM3/4/5 clock source. More... | |

| #define | __HAL_RCC_LPTIM345_CONFIG(__LPTIM345CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_LPTIM3SEL, (uint32_t)(__LPTIM345CLKSource__)) |

| macro to configure the LPTIM3/4/5 clock source. More... | |

| #define | __HAL_RCC_LPTIM3_CONFIG __HAL_RCC_LPTIM345_CONFIG |

| macro to configure the LPTIM3 clock source. More... | |

| #define | __HAL_RCC_LPTIM3_CONFIG __HAL_RCC_LPTIM345_CONFIG |

| macro to configure the LPTIM3 clock source. More... | |

| #define | __HAL_RCC_LPUART1_CONFIG(__LPUART1CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_LPUART1SEL, (uint32_t)(__LPUART1CLKSource__)) |

| macro to configure the LPUART1 clock (LPUART1CLK). More... | |

| #define | __HAL_RCC_LPUART1_CONFIG(__LPUART1CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_LPUART1SEL, (uint32_t)(__LPUART1CLKSource__)) |

| macro to configure the LPUART1 clock (LPUART1CLK). More... | |

| #define | __HAL_RCC_LSECSS_EXTI_CLEAR_FLAG() WRITE_REG(EXTI->PR1, RCC_EXTI_LINE_LSECSS) |

| Clear the RCC LSE CSS EXTI flag. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_CLEAR_FLAG() WRITE_REG(EXTI->PR1, RCC_EXTI_LINE_LSECSS) |

| Clear the RCC LSE CSS EXTI flag. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_EVENT() CLEAR_BIT(EXTI->EMR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Event Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_EVENT() CLEAR_BIT(EXTI->EMR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Event Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_FALLING_EDGE() CLEAR_BIT(EXTI->FTSR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Extended Interrupt Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_FALLING_EDGE() CLEAR_BIT(EXTI->FTSR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Extended Interrupt Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_IT() CLEAR_BIT(EXTI->IMR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Extended Interrupt Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_IT() CLEAR_BIT(EXTI->IMR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Extended Interrupt Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_RISING_EDGE() CLEAR_BIT(EXTI->RTSR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Extended Interrupt Rising Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_RISING_EDGE() CLEAR_BIT(EXTI->RTSR1, RCC_EXTI_LINE_LSECSS) |

| Disable the RCC LSE CSS Extended Interrupt Rising Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_RISING_FALLING_EDGE() |

| Disable the RCC LSE CSS Extended Interrupt Rising & Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_DISABLE_RISING_FALLING_EDGE() |

| Disable the RCC LSE CSS Extended Interrupt Rising & Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_EVENT() SET_BIT(EXTI->EMR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Event Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_EVENT() SET_BIT(EXTI->EMR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Event Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_FALLING_EDGE() SET_BIT(EXTI->FTSR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Extended Interrupt Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_FALLING_EDGE() SET_BIT(EXTI->FTSR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Extended Interrupt Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_IT() SET_BIT(EXTI->IMR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Extended Interrupt Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_IT() SET_BIT(EXTI->IMR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Extended Interrupt Line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_RISING_EDGE() SET_BIT(EXTI->RTSR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Extended Interrupt Rising Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_RISING_EDGE() SET_BIT(EXTI->RTSR1, RCC_EXTI_LINE_LSECSS) |

| Enable the RCC LSE CSS Extended Interrupt Rising Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_RISING_FALLING_EDGE() |

| Enable the RCC LSE CSS Extended Interrupt Rising & Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_ENABLE_RISING_FALLING_EDGE() |

| Enable the RCC LSE CSS Extended Interrupt Rising & Falling Trigger. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_GENERATE_SWIT() SET_BIT(EXTI->SWIER1, RCC_EXTI_LINE_LSECSS) |

| Generate a Software interrupt on the RCC LSE CSS EXTI line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_GENERATE_SWIT() SET_BIT(EXTI->SWIER1, RCC_EXTI_LINE_LSECSS) |

| Generate a Software interrupt on the RCC LSE CSS EXTI line. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_GET_FLAG() (READ_BIT(EXTI->PR1, RCC_EXTI_LINE_LSECSS) == RCC_EXTI_LINE_LSECSS) |

| Check whether the specified RCC LSE CSS EXTI interrupt flag is set or not. More... | |

| #define | __HAL_RCC_LSECSS_EXTI_GET_FLAG() (READ_BIT(EXTI->PR1, RCC_EXTI_LINE_LSECSS) == RCC_EXTI_LINE_LSECSS) |

| Check whether the specified RCC LSE CSS EXTI interrupt flag is set or not. More... | |

| #define | __HAL_RCC_PLL2_CONFIG(__PLL2M__, __PLL2N__, __PLL2P__, __PLL2Q__, __PLL2R__) |

| Macro to configures the PLL2 multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL2_CONFIG(__PLL2M__, __PLL2N__, __PLL2P__, __PLL2Q__, __PLL2R__) |

| Macro to configures the PLL2 multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL2_DISABLE() CLEAR_BIT(RCC->CR, RCC_CR_PLL2ON) |

| #define | __HAL_RCC_PLL2_DISABLE() CLEAR_BIT(RCC->CR, RCC_CR_PLL2ON) |

| #define | __HAL_RCC_PLL2_ENABLE() SET_BIT(RCC->CR, RCC_CR_PLL2ON) |

| Macros to enable or disable PLL2. More... | |

| #define | __HAL_RCC_PLL2_ENABLE() SET_BIT(RCC->CR, RCC_CR_PLL2ON) |

| Macros to enable or disable PLL2. More... | |

| #define | __HAL_RCC_PLL2_VCIRANGE(__RCC_PLL2VCIRange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL2RGE, (__RCC_PLL2VCIRange__)) |

| Macro to select the PLL2 reference frequency range. More... | |

| #define | __HAL_RCC_PLL2_VCIRANGE(__RCC_PLL2VCIRange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL2RGE, (__RCC_PLL2VCIRange__)) |

| Macro to select the PLL2 reference frequency range. More... | |

| #define | __HAL_RCC_PLL2_VCORANGE(__RCC_PLL2VCORange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL2VCOSEL, (__RCC_PLL2VCORange__)) |

| Macro to select the PLL2 reference frequency range. More... | |

| #define | __HAL_RCC_PLL2_VCORANGE(__RCC_PLL2VCORange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL2VCOSEL, (__RCC_PLL2VCORange__)) |

| Macro to select the PLL2 reference frequency range. More... | |

| #define | __HAL_RCC_PLL2CLKOUT_DISABLE(__RCC_PLL2ClockOut__) CLEAR_BIT(RCC->PLLCFGR, (__RCC_PLL2ClockOut__)) |

| #define | __HAL_RCC_PLL2CLKOUT_DISABLE(__RCC_PLL2ClockOut__) CLEAR_BIT(RCC->PLLCFGR, (__RCC_PLL2ClockOut__)) |

| #define | __HAL_RCC_PLL2CLKOUT_ENABLE(__RCC_PLL2ClockOut__) SET_BIT(RCC->PLLCFGR, (__RCC_PLL2ClockOut__)) |

| Enables or disables each clock output (PLL2_P_CLK, PLL2_Q_CLK, PLL2_R_CLK) More... | |

| #define | __HAL_RCC_PLL2CLKOUT_ENABLE(__RCC_PLL2ClockOut__) SET_BIT(RCC->PLLCFGR, (__RCC_PLL2ClockOut__)) |

| Enables or disables each clock output (PLL2_P_CLK, PLL2_Q_CLK, PLL2_R_CLK) More... | |

| #define | __HAL_RCC_PLL2FRACN_CONFIG(__RCC_PLL2FRACN__) MODIFY_REG(RCC->PLL2FRACR, RCC_PLL2FRACR_FRACN2,((uint32_t)(__RCC_PLL2FRACN__) << RCC_PLL2FRACR_FRACN2_Pos)) |

| Macro to configures PLL2 clock Fractional Part Of The Multiplication Factor. More... | |

| #define | __HAL_RCC_PLL2FRACN_CONFIG(__RCC_PLL2FRACN__) MODIFY_REG(RCC->PLL2FRACR, RCC_PLL2FRACR_FRACN2,((uint32_t)(__RCC_PLL2FRACN__) << RCC_PLL2FRACR_FRACN2_Pos)) |

| Macro to configures PLL2 clock Fractional Part Of The Multiplication Factor. More... | |

| #define | __HAL_RCC_PLL2FRACN_DISABLE() CLEAR_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL2FRACEN) |

| #define | __HAL_RCC_PLL2FRACN_DISABLE() CLEAR_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL2FRACEN) |

| #define | __HAL_RCC_PLL2FRACN_ENABLE() SET_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL2FRACEN) |

| Enables or disables Fractional Part Of The Multiplication Factor of PLL2 VCO. More... | |

| #define | __HAL_RCC_PLL2FRACN_ENABLE() SET_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL2FRACEN) |

| Enables or disables Fractional Part Of The Multiplication Factor of PLL2 VCO. More... | |

| #define | __HAL_RCC_PLL3_CONFIG(__PLL3M__, __PLL3N__, __PLL3P__, __PLL3Q__, __PLL3R__) |

| Macro to configures the PLL3 multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL3_CONFIG(__PLL3M__, __PLL3N__, __PLL3P__, __PLL3Q__, __PLL3R__) |

| Macro to configures the PLL3 multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL3_DISABLE() CLEAR_BIT(RCC->CR, RCC_CR_PLL3ON) |

| #define | __HAL_RCC_PLL3_DISABLE() CLEAR_BIT(RCC->CR, RCC_CR_PLL3ON) |

| #define | __HAL_RCC_PLL3_ENABLE() SET_BIT(RCC->CR, RCC_CR_PLL3ON) |

| Macros to enable or disable the main PLL3. More... | |

| #define | __HAL_RCC_PLL3_ENABLE() SET_BIT(RCC->CR, RCC_CR_PLL3ON) |

| Macros to enable or disable the main PLL3. More... | |

| #define | __HAL_RCC_PLL3_VCIRANGE(__RCC_PLL3VCIRange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL3RGE, (__RCC_PLL3VCIRange__)) |

| Macro to select the PLL3 reference frequency range. More... | |

| #define | __HAL_RCC_PLL3_VCIRANGE(__RCC_PLL3VCIRange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL3RGE, (__RCC_PLL3VCIRange__)) |

| Macro to select the PLL3 reference frequency range. More... | |

| #define | __HAL_RCC_PLL3_VCORANGE(__RCC_PLL3VCORange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL3VCOSEL, (__RCC_PLL3VCORange__)) |

| Macro to select the PLL3 reference frequency range. More... | |

| #define | __HAL_RCC_PLL3_VCORANGE(__RCC_PLL3VCORange__) MODIFY_REG(RCC->PLLCFGR, RCC_PLLCFGR_PLL3VCOSEL, (__RCC_PLL3VCORange__)) |

| Macro to select the PLL3 reference frequency range. More... | |

| #define | __HAL_RCC_PLL3CLKOUT_DISABLE(__RCC_PLL3ClockOut__) CLEAR_BIT(RCC->PLLCFGR, (__RCC_PLL3ClockOut__)) |

| #define | __HAL_RCC_PLL3CLKOUT_DISABLE(__RCC_PLL3ClockOut__) CLEAR_BIT(RCC->PLLCFGR, (__RCC_PLL3ClockOut__)) |

| #define | __HAL_RCC_PLL3CLKOUT_ENABLE(__RCC_PLL3ClockOut__) SET_BIT(RCC->PLLCFGR, (__RCC_PLL3ClockOut__)) |

| Enables or disables each clock output (PLL3_P_CLK, PLL3_Q_CLK, PLL3_R_CLK) More... | |

| #define | __HAL_RCC_PLL3CLKOUT_ENABLE(__RCC_PLL3ClockOut__) SET_BIT(RCC->PLLCFGR, (__RCC_PLL3ClockOut__)) |

| Enables or disables each clock output (PLL3_P_CLK, PLL3_Q_CLK, PLL3_R_CLK) More... | |

| #define | __HAL_RCC_PLL3FRACN_CONFIG(__RCC_PLL3FRACN__) MODIFY_REG(RCC->PLL3FRACR, RCC_PLL3FRACR_FRACN3, (uint32_t)(__RCC_PLL3FRACN__) << RCC_PLL3FRACR_FRACN3_Pos) |

| Macro to configures PLL3 clock Fractional Part of The Multiplication Factor. More... | |

| #define | __HAL_RCC_PLL3FRACN_CONFIG(__RCC_PLL3FRACN__) MODIFY_REG(RCC->PLL3FRACR, RCC_PLL3FRACR_FRACN3, (uint32_t)(__RCC_PLL3FRACN__) << RCC_PLL3FRACR_FRACN3_Pos) |

| Macro to configures PLL3 clock Fractional Part of The Multiplication Factor. More... | |

| #define | __HAL_RCC_PLL3FRACN_DISABLE() CLEAR_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL3FRACEN) |

| #define | __HAL_RCC_PLL3FRACN_DISABLE() CLEAR_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL3FRACEN) |

| #define | __HAL_RCC_PLL3FRACN_ENABLE() SET_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL3FRACEN) |

| Enables or disables Fractional Part Of The Multiplication Factor of PLL3 VCO. More... | |

| #define | __HAL_RCC_PLL3FRACN_ENABLE() SET_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLL3FRACEN) |

| Enables or disables Fractional Part Of The Multiplication Factor of PLL3 VCO. More... | |

| #define | __HAL_RCC_PLL_CONFIG(__RCC_PLLSource__, __PLLM__, __PLLN__, __PLLP__, __PLLQ__) |

| Macro to configure the main PLL clock source, multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL_CONFIG(__RCC_PLLSource__, __PLLM__, __PLLN__, __PLLP__, __PLLQ__) |

| Macro to configure the main PLL clock source, multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL_CONFIG(__RCC_PLLSource__, __PLLM__, __PLLN__, __PLLP__, __PLLQ__) |

| Macro to configure the main PLL clock source, multiplication and division factors. More... | |

| #define | __HAL_RCC_PLL_CONFIG(__RCC_PLLSource__, __PLLM__, __PLLN__, __PLLP__, __PLLQ__) |

| Macro to configure the main PLL clock source, multiplication and division factors. More... | |

| #define | __HAL_RCC_PLLI2S_CONFIG(__PLLI2SN__, __PLLI2SP__, __PLLI2SQ__, __PLLI2SR__) |

| Macro to configure the PLLI2S clock multiplication and division factors. More... | |

| #define | __HAL_RCC_PLLI2S_CONFIG(__PLLI2SN__, __PLLI2SR__) |

| Macro to configure the PLLI2S clock multiplication and division factors . More... | |

| #define | __HAL_RCC_PLLI2S_CONFIG(__PLLI2SN__, __PLLI2SR__) |

| Macro to configure the PLLI2S clock multiplication and division factors . More... | |

| #define | __HAL_RCC_PLLI2S_CONFIG(__PLLI2SN__, __PLLI2SR__) |

| Macro to configure the PLLI2S clock multiplication and division factors . More... | |

| #define | __HAL_RCC_PLLI2S_PLLSAICLKDIVQ_CONFIG(__PLLI2SDivQ__) (MODIFY_REG(RCC->DCKCFGR1, RCC_DCKCFGR1_PLLI2SDIVQ, (__PLLI2SDivQ__)-1)) |

| Macro to configure the SAI clock Divider coming from PLLI2S. More... | |

| #define | __HAL_RCC_PLLSAI_CLEAR_IT() (RCC->CIR |= (RCC_CIR_PLLSAIRDYF)) |

| Clear the PLLSAI RDY interrupt pending bits. More... | |

| #define | __HAL_RCC_PLLSAI_CONFIG(__PLLSAIN__, __PLLSAIP__, __PLLSAIQ__, __PLLSAIR__) |

| Macro to configure the PLLSAI clock multiplication and division factors. More... | |

| #define | __HAL_RCC_PLLSAI_DISABLE() (RCC->CR &= ~(RCC_CR_PLLSAION)) |

| #define | __HAL_RCC_PLLSAI_DISABLE_IT() (RCC->CIR &= ~(RCC_CIR_PLLSAIRDYIE)) |

| Disable PLLSAI_RDY interrupt. More... | |

| #define | __HAL_RCC_PLLSAI_ENABLE() (RCC->CR |= (RCC_CR_PLLSAION)) |

| Macros to Enable or Disable the PLLISAI. More... | |

| #define | __HAL_RCC_PLLSAI_ENABLE_IT() (RCC->CIR |= (RCC_CIR_PLLSAIRDYIE)) |

| Enable PLLSAI_RDY interrupt. More... | |

| #define | __HAL_RCC_PLLSAI_GET_FLAG() ((RCC->CR & (RCC_CR_PLLSAIRDY)) == (RCC_CR_PLLSAIRDY)) |

| Check PLLSAI RDY flag is set or not. More... | |

| #define | __HAL_RCC_PLLSAI_GET_IT() ((RCC->CIR & (RCC_CIR_PLLSAIRDYIE)) == (RCC_CIR_PLLSAIRDYIE)) |

| Check the PLLSAI RDY interrupt has occurred or not. More... | |

| #define | __HAL_RCC_PLLSAI_PLLSAICLKDIVQ_CONFIG(__PLLSAIDivQ__) (MODIFY_REG(RCC->DCKCFGR1, RCC_DCKCFGR1_PLLSAIDIVQ, ((__PLLSAIDivQ__)-1)<<8)) |

| Macro to configure the SAI clock Divider coming from PLLSAI. More... | |

| #define | __HAL_RCC_RNG_CONFIG(__RNGCLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_RNGSEL, (uint32_t)(__RNGCLKSource__)) |

| macro to configure the RNG clock (RNGCLK). More... | |

| #define | __HAL_RCC_RNG_CONFIG(__RNGCLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_RNGSEL, (uint32_t)(__RNGCLKSource__)) |

| macro to configure the RNG clock (RNGCLK). More... | |

| #define | __HAL_RCC_SAI1_CONFIG(__RCC_SAI1CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SAI1SEL, (__RCC_SAI1CLKSource__)) |

| Macro to Configure the SAI1 clock source. More... | |

| #define | __HAL_RCC_SAI1_CONFIG(__RCC_SAI1CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SAI1SEL, (__RCC_SAI1CLKSource__)) |

| Macro to Configure the SAI1 clock source. More... | |

| #define | __HAL_RCC_SAI1_CONFIG(__SOURCE__) MODIFY_REG(RCC->DCKCFGR1, RCC_DCKCFGR1_SAI1SEL, (uint32_t)(__SOURCE__)) |

| Macro to configure SAI1 clock source selection. More... | |

| #define | __HAL_RCC_SAI2_CONFIG(__SOURCE__) MODIFY_REG(RCC->DCKCFGR1, RCC_DCKCFGR1_SAI2SEL, (uint32_t)(__SOURCE__)) |

| Macro to configure SAI2 clock source selection. More... | |

| #define | __HAL_RCC_SDMMC1_CONFIG(__SDMMC1_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_SDMMC1SEL, (uint32_t)(__SDMMC1_CLKSOURCE__)) |

| Macro to configure the SDMMC1 clock (SDMMC1CLK). More... | |

| #define | __HAL_RCC_SDMMC_CONFIG(__SDMMCCLKSource__) MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_SDMMCSEL, (uint32_t)(__SDMMCCLKSource__)) |

| Macro to configure the SDMMC clock. More... | |

| #define | __HAL_RCC_SDMMC_CONFIG(__SDMMCCLKSource__) MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_SDMMCSEL, (uint32_t)(__SDMMCCLKSource__)) |

| Macro to configure the SDMMC clock. More... | |

| #define | __HAL_RCC_SPDIFRX_CONFIG(__RCC_SPDIFCLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SPDIFSEL, (__RCC_SPDIFCLKSource__)) |

| Macro to Configure the SPDIFRX clock source. More... | |

| #define | __HAL_RCC_SPDIFRX_CONFIG(__RCC_SPDIFCLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SPDIFSEL, (__RCC_SPDIFCLKSource__)) |

| Macro to Configure the SPDIFRX clock source. More... | |

| #define | __HAL_RCC_SPI123_CONFIG(__RCC_SPI123CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI123SEL, (__RCC_SPI123CLKSource__)) |

| Macro to Configure the SPI1/2/3 clock source. More... | |

| #define | __HAL_RCC_SPI123_CONFIG(__RCC_SPI123CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI123SEL, (__RCC_SPI123CLKSource__)) |

| Macro to Configure the SPI1/2/3 clock source. More... | |

| #define | __HAL_RCC_SPI1_CONFIG __HAL_RCC_SPI123_CONFIG |

| Macro to Configure the SPI1 clock source. More... | |

| #define | __HAL_RCC_SPI1_CONFIG __HAL_RCC_SPI123_CONFIG |

| Macro to Configure the SPI1 clock source. More... | |

| #define | __HAL_RCC_SPI2_CONFIG __HAL_RCC_SPI123_CONFIG |

| Macro to Configure the SPI2 clock source. More... | |

| #define | __HAL_RCC_SPI2_CONFIG __HAL_RCC_SPI123_CONFIG |

| Macro to Configure the SPI2 clock source. More... | |

| #define | __HAL_RCC_SPI3_CONFIG __HAL_RCC_SPI123_CONFIG |

| Macro to Configure the SPI3 clock source. More... | |

| #define | __HAL_RCC_SPI3_CONFIG __HAL_RCC_SPI123_CONFIG |

| Macro to Configure the SPI3 clock source. More... | |

| #define | __HAL_RCC_SPI45_CONFIG(__RCC_SPI45CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI45SEL, (__RCC_SPI45CLKSource__)) |

| Macro to Configure the SPI4/5 clock source. More... | |

| #define | __HAL_RCC_SPI45_CONFIG(__RCC_SPI45CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SPI45SEL, (__RCC_SPI45CLKSource__)) |

| Macro to Configure the SPI4/5 clock source. More... | |

| #define | __HAL_RCC_SPI4_CONFIG __HAL_RCC_SPI45_CONFIG |

| Macro to Configure the SPI4 clock source. More... | |

| #define | __HAL_RCC_SPI4_CONFIG __HAL_RCC_SPI45_CONFIG |

| Macro to Configure the SPI4 clock source. More... | |

| #define | __HAL_RCC_SPI5_CONFIG __HAL_RCC_SPI45_CONFIG |

| Macro to Configure the SPI5 clock source. More... | |

| #define | __HAL_RCC_SPI5_CONFIG __HAL_RCC_SPI45_CONFIG |

| Macro to Configure the SPI5 clock source. More... | |

| #define | __HAL_RCC_SPI6_CONFIG(__RCC_SPI6CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_SPI6SEL, (__RCC_SPI6CLKSource__)) |

| Macro to Configure the SPI6 clock source. More... | |

| #define | __HAL_RCC_SPI6_CONFIG(__RCC_SPI6CLKSource__) MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_SPI6SEL, (__RCC_SPI6CLKSource__)) |

| Macro to Configure the SPI6 clock source. More... | |

| #define | __HAL_RCC_SWPMI1_CONFIG(__SWPMI1CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SWPSEL, (uint32_t)(__SWPMI1CLKSource__)) |

| Macro to configure the SWPMI1 clock. More... | |

| #define | __HAL_RCC_SWPMI1_CONFIG(__SWPMI1CLKSource__) MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_SWPSEL, (uint32_t)(__SWPMI1CLKSource__)) |

| Macro to configure the SWPMI1 clock. More... | |

| #define | __HAL_RCC_TIMCLKPRESCALER(__PRESC__) |

| Macro to configure the Timers clocks prescalers. More... | |

| #define | __HAL_RCC_TIMCLKPRESCALER(__PRESC__) |

| Macro to configure the Timers clocks prescalers. More... | |

| #define | __HAL_RCC_TIMCLKPRESCALER(__PRESC__) |

| Macro to configure the Timers clocks prescalers. More... | |

| #define | __HAL_RCC_UART4_CONFIG(__UART4_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_UART4SEL, (uint32_t)(__UART4_CLKSOURCE__)) |

| Macro to configure the UART4 clock (UART4CLK). More... | |

| #define | __HAL_RCC_UART4_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART4 clock (UART4CLK). More... | |

| #define | __HAL_RCC_UART4_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART4 clock (UART4CLK). More... | |

| #define | __HAL_RCC_UART5_CONFIG(__UART5_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_UART5SEL, (uint32_t)(__UART5_CLKSOURCE__)) |

| Macro to configure the UART5 clock (UART5CLK). More... | |

| #define | __HAL_RCC_UART5_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART5 clock (UART5CLK). More... | |

| #define | __HAL_RCC_UART5_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART5 clock (UART5CLK). More... | |

| #define | __HAL_RCC_UART7_CONFIG(__UART7_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_UART7SEL, (uint32_t)(__UART7_CLKSOURCE__)) |

| Macro to configure the UART7 clock (UART7CLK). More... | |

| #define | __HAL_RCC_UART7_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART5 clock (UART7CLK). More... | |

| #define | __HAL_RCC_UART7_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART5 clock (UART7CLK). More... | |

| #define | __HAL_RCC_UART8_CONFIG(__UART8_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_UART8SEL, (uint32_t)(__UART8_CLKSOURCE__)) |

| Macro to configure the UART8 clock (UART8CLK). More... | |

| #define | __HAL_RCC_UART8_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART8 clock (UART8CLK). More... | |

| #define | __HAL_RCC_UART8_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the UART8 clock (UART8CLK). More... | |

| #define | __HAL_RCC_USART16910_CONFIG(__USART16910CLKSource__) MODIFY_REG(RCC->D2CCIP2R, RCC_D2CCIP2R_USART16910SEL, (uint32_t)(__USART16910CLKSource__)) |

| macro to configure the USART1/6/9* /10* clock (USART16CLK). More... | |

| #define | __HAL_RCC_USART16910_CONFIG(__USART16910CLKSource__) MODIFY_REG(RCC->D2CCIP2R, RCC_D2CCIP2R_USART16910SEL, (uint32_t)(__USART16910CLKSource__)) |

| macro to configure the USART1/6/9* /10* clock (USART16CLK). More... | |

| #define | __HAL_RCC_USART16_CONFIG __HAL_RCC_USART16910_CONFIG |

| #define | __HAL_RCC_USART16_CONFIG __HAL_RCC_USART16910_CONFIG |

| #define | __HAL_RCC_USART1_CONFIG(__USART1_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_USART1SEL, (uint32_t)(__USART1_CLKSOURCE__)) |

| Macro to configure the USART1 clock (USART1CLK). More... | |

| #define | __HAL_RCC_USART1_CONFIG __HAL_RCC_USART16_CONFIG |

| macro to configure the USART1 clock (USART1CLK). More... | |

| #define | __HAL_RCC_USART1_CONFIG __HAL_RCC_USART16_CONFIG |

| macro to configure the USART1 clock (USART1CLK). More... | |

| #define | __HAL_RCC_USART234578_CONFIG(__USART234578CLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_USART234578SEL, (uint32_t)(__USART234578CLKSource__)) |

| macro to configure the USART234578 clock (USART234578CLK). More... | |

| #define | __HAL_RCC_USART234578_CONFIG(__USART234578CLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_USART234578SEL, (uint32_t)(__USART234578CLKSource__)) |

| macro to configure the USART234578 clock (USART234578CLK). More... | |

| #define | __HAL_RCC_USART2_CONFIG(__USART2_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_USART2SEL, (uint32_t)(__USART2_CLKSOURCE__)) |

| Macro to configure the USART2 clock (USART2CLK). More... | |

| #define | __HAL_RCC_USART2_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the USART2 clock (USART2CLK). More... | |

| #define | __HAL_RCC_USART2_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the USART2 clock (USART2CLK). More... | |

| #define | __HAL_RCC_USART3_CONFIG(__USART3_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_USART3SEL, (uint32_t)(__USART3_CLKSOURCE__)) |

| Macro to configure the USART3 clock (USART3CLK). More... | |

| #define | __HAL_RCC_USART3_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the USART3 clock (USART3CLK). More... | |

| #define | __HAL_RCC_USART3_CONFIG __HAL_RCC_USART234578_CONFIG |

| macro to configure the USART3 clock (USART3CLK). More... | |

| #define | __HAL_RCC_USART6_CONFIG(__USART6_CLKSOURCE__) MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_USART6SEL, (uint32_t)(__USART6_CLKSOURCE__)) |

| Macro to configure the USART6 clock (USART6CLK). More... | |

| #define | __HAL_RCC_USART6_CONFIG __HAL_RCC_USART16_CONFIG |

| macro to configure the USART6 clock (USART6CLK). More... | |

| #define | __HAL_RCC_USART6_CONFIG __HAL_RCC_USART16_CONFIG |

| macro to configure the USART6 clock (USART6CLK). More... | |

| #define | __HAL_RCC_USB_CONFIG(__USBCLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_USBSEL, (uint32_t)(__USBCLKSource__)) |

| Macro to configure the USB clock (USBCLK). More... | |

| #define | __HAL_RCC_USB_CONFIG(__USBCLKSource__) MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_USBSEL, (uint32_t)(__USBCLKSource__)) |

| Macro to configure the USB clock (USBCLK). More... | |

| #define | RCC_CRS_FLAG_ERROR_MASK ((uint32_t)(RCC_CRS_FLAG_TRIMOVF | RCC_CRS_FLAG_SYNCERR | RCC_CRS_FLAG_SYNCMISS)) |

| Clear the CRS specified FLAG. More... | |

| #define | RCC_CRS_FLAG_ERROR_MASK ((uint32_t)(RCC_CRS_FLAG_TRIMOVF | RCC_CRS_FLAG_SYNCERR | RCC_CRS_FLAG_SYNCMISS)) |

| Clear the CRS specified FLAG. More... | |

| #define | RCC_CRS_IT_ERROR_MASK ((uint32_t)(RCC_CRS_IT_TRIMOVF | RCC_CRS_IT_SYNCERR | RCC_CRS_IT_SYNCMISS)) |

| Clear the CRS interrupt pending bits. More... | |

| #define | RCC_CRS_IT_ERROR_MASK ((uint32_t)(RCC_CRS_IT_TRIMOVF | RCC_CRS_IT_SYNCERR | RCC_CRS_IT_SYNCMISS)) |

| Clear the CRS interrupt pending bits. More... | |

Detailed Description

Macro Definition Documentation

◆ __HAL_RCC_ADC_CONFIG [1/2]

| #define __HAL_RCC_ADC_CONFIG | ( | __ADCCLKSource__ | ) | MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_ADCSEL, (uint32_t)(__ADCCLKSource__)) |

Macro to configure the ADC clock.

- Parameters

-

<strong>ADCCLKSource</strong> specifies the ADC digital interface clock source. This parameter can be one of the following values: - RCC_ADCCLKSOURCE_PLL2: PLL2_P Clock selected as ADC clock

- RCC_ADCCLKSOURCE_PLL3: PLL3_R Clock selected as ADC clock

- RCC_ADCCLKSOURCE_CLKP: CLKP Clock selected as ADC clock

Definition at line 3112 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_ADC_CONFIG [2/2]

| #define __HAL_RCC_ADC_CONFIG | ( | __ADCCLKSource__ | ) | MODIFY_REG(RCC->SRDCCIPR, RCC_SRDCCIPR_ADCSEL, (uint32_t)(__ADCCLKSource__)) |

Macro to configure the ADC clock.

- Parameters

-

<strong>ADCCLKSource</strong> specifies the ADC digital interface clock source. This parameter can be one of the following values: - RCC_ADCCLKSOURCE_PLL2: PLL2_P Clock selected as ADC clock

- RCC_ADCCLKSOURCE_PLL3: PLL3_R Clock selected as ADC clock

- RCC_ADCCLKSOURCE_CLKP: CLKP Clock selected as ADC clock

Definition at line 3116 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CEC_CONFIG [1/3]

| #define __HAL_RCC_CEC_CONFIG | ( | __CEC_CLKSOURCE__ | ) | MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_CECSEL, (uint32_t)(__CEC_CLKSOURCE__)) |

Macro to configure the CEC clock (CECCLK).

- Parameters

-

<strong>CEC_CLKSOURCE</strong> specifies the CEC clock source. This parameter can be one of the following values: - RCC_CECCLKSOURCE_LSE: LSE selected as CEC clock

- RCC_CECCLKSOURCE_HSI: HSI divided by 488 selected as CEC clock

Definition at line 3087 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CEC_CONFIG [2/3]

| #define __HAL_RCC_CEC_CONFIG | ( | __CECCLKSource__ | ) | MODIFY_REG(RCC->D2CCIP2R, RCC_CDCCIP2R_CECSEL, (uint32_t)(__CECCLKSource__)) |

macro to configure the CEC clock (CECCLK).

- Parameters

-

<strong>CECCLKSource</strong> specifies the CEC clock source. This parameter can be one of the following values: - RCC_CECCLKSOURCE_LSE: LSE selected as CEC clock

- RCC_CECCLKSOURCE_LSI: LSI selected as CEC clock

- RCC_CECCLKSOURCE_CSI: CSI Clock selected as CEC clock

Definition at line 3208 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CEC_CONFIG [3/3]

| #define __HAL_RCC_CEC_CONFIG | ( | __CECCLKSource__ | ) | MODIFY_REG(RCC->CDCCIP2R, RCC_CDCCIP2R_CECSEL, (uint32_t)(__CECCLKSource__)) |

macro to configure the CEC clock (CECCLK).

- Parameters

-

<strong>CECCLKSource</strong> specifies the CEC clock source. This parameter can be one of the following values: - RCC_CECCLKSOURCE_LSE: LSE selected as CEC clock

- RCC_CECCLKSOURCE_LSI: LSI selected as CEC clock

- RCC_CECCLKSOURCE_CSI: CSI Clock selected as CEC clock

Definition at line 3212 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CLK48_CONFIG

| #define __HAL_RCC_CLK48_CONFIG | ( | __CLK48_SOURCE__ | ) | MODIFY_REG(RCC->DCKCFGR2, RCC_DCKCFGR2_CK48MSEL, (uint32_t)(__CLK48_SOURCE__)) |

Macro to configure the CLK48 source (CLK48CLK).

- Parameters

-

<strong>CLK48_SOURCE</strong> specifies the CLK48 clock source. This parameter can be one of the following values: - RCC_CLK48SOURCE_PLL: PLL selected as CLK48 source

- RCC_CLK48SOURCE_PLLSAIP: PLLSAIP selected as CLK48 source

Definition at line 3104 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CLKP_CONFIG [1/2]

| #define __HAL_RCC_CLKP_CONFIG | ( | __CLKPSource__ | ) | MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_CKPERSEL, (uint32_t)(__CLKPSource__)) |

Macro to configure the CLKP : Oscillator clock for peripheral.

- Parameters

-

<strong>CLKPSource</strong> specifies Oscillator clock for peripheral This parameter can be one of the following values: - RCC_CLKPSOURCE_HSI: HSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_CSI: CSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_HSE: HSE selected Oscillator clock for peripheral

Definition at line 3235 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CLKP_CONFIG [2/2]

| #define __HAL_RCC_CLKP_CONFIG | ( | __CLKPSource__ | ) | MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_CKPERSEL, (uint32_t)(__CLKPSource__)) |

Macro to configure the CLKP : Oscillator clock for peripheral.

- Parameters

-

<strong>CLKPSource</strong> specifies Oscillator clock for peripheral This parameter can be one of the following values: - RCC_CLKPSOURCE_HSI: HSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_CSI: CSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_HSE: HSE selected Oscillator clock for peripheral

Definition at line 3239 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_CLEAR_FLAG [1/2]

| #define __HAL_RCC_CRS_CLEAR_FLAG | ( | __FLAG__ | ) |

Definition at line 3821 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_CLEAR_FLAG [2/2]

| #define __HAL_RCC_CRS_CLEAR_FLAG | ( | __FLAG__ | ) |

Definition at line 3825 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_CLEAR_IT [1/2]

| #define __HAL_RCC_CRS_CLEAR_IT | ( | __INTERRUPT__ | ) |

Definition at line 3777 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_CLEAR_IT [2/2]

| #define __HAL_RCC_CRS_CLEAR_IT | ( | __INTERRUPT__ | ) |

Definition at line 3781 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_DISABLE_IT [1/2]

Disable the specified CRS interrupts.

- Parameters

-

<strong>INTERRUPT</strong> specifies the CRS interrupt sources to be disabled. This parameter can be any combination of the following values: - RCC_CRS_IT_SYNCOK SYNC event OK interrupt

- RCC_CRS_IT_SYNCWARN SYNC warning interrupt

- RCC_CRS_IT_ERR Synchronization or trimming error interrupt

- RCC_CRS_IT_ESYNC Expected SYNC interrupt

- Return values

-

None

Definition at line 3750 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_DISABLE_IT [2/2]

Disable the specified CRS interrupts.

- Parameters

-

<strong>INTERRUPT</strong> specifies the CRS interrupt sources to be disabled. This parameter can be any combination of the following values: - RCC_CRS_IT_SYNCOK SYNC event OK interrupt

- RCC_CRS_IT_SYNCWARN SYNC warning interrupt

- RCC_CRS_IT_ERR Synchronization or trimming error interrupt

- RCC_CRS_IT_ESYNC Expected SYNC interrupt

- Return values

-

None

Definition at line 3754 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_ENABLE_IT [1/2]

Enable the specified CRS interrupts.

- Parameters

-

<strong>INTERRUPT</strong> specifies the CRS interrupt sources to be enabled. This parameter can be any combination of the following values: - RCC_CRS_IT_SYNCOK SYNC event OK interrupt

- RCC_CRS_IT_SYNCWARN SYNC warning interrupt

- RCC_CRS_IT_ERR Synchronization or trimming error interrupt

- RCC_CRS_IT_ESYNC Expected SYNC interrupt

- Return values

-

None

Definition at line 3738 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_ENABLE_IT [2/2]

Enable the specified CRS interrupts.

- Parameters

-

<strong>INTERRUPT</strong> specifies the CRS interrupt sources to be enabled. This parameter can be any combination of the following values: - RCC_CRS_IT_SYNCOK SYNC event OK interrupt

- RCC_CRS_IT_SYNCWARN SYNC warning interrupt

- RCC_CRS_IT_ERR Synchronization or trimming error interrupt

- RCC_CRS_IT_ESYNC Expected SYNC interrupt

- Return values

-

None

Definition at line 3742 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_GET_FLAG [1/2]

Check whether the specified CRS flag is set or not.

- Parameters

-

<strong>FLAG</strong> specifies the flag to check. This parameter can be one of the following values: - RCC_CRS_FLAG_SYNCOK SYNC event OK

- RCC_CRS_FLAG_SYNCWARN SYNC warning

- RCC_CRS_FLAG_ERR Error

- RCC_CRS_FLAG_ESYNC Expected SYNC

- RCC_CRS_FLAG_TRIMOVF Trimming overflow or underflow

- RCC_CRS_FLAG_SYNCERR SYNC error

- RCC_CRS_FLAG_SYNCMISS SYNC missed

- Return values

-

The new state of FLAG (TRUE or FALSE).

Definition at line 3801 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_GET_FLAG [2/2]

Check whether the specified CRS flag is set or not.

- Parameters

-

<strong>FLAG</strong> specifies the flag to check. This parameter can be one of the following values: - RCC_CRS_FLAG_SYNCOK SYNC event OK

- RCC_CRS_FLAG_SYNCWARN SYNC warning

- RCC_CRS_FLAG_ERR Error

- RCC_CRS_FLAG_ESYNC Expected SYNC

- RCC_CRS_FLAG_TRIMOVF Trimming overflow or underflow

- RCC_CRS_FLAG_SYNCERR SYNC error

- RCC_CRS_FLAG_SYNCMISS SYNC missed

- Return values

-

The new state of FLAG (TRUE or FALSE).

Definition at line 3805 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_GET_IT_SOURCE [1/2]

| #define __HAL_RCC_CRS_GET_IT_SOURCE | ( | __INTERRUPT__ | ) | ((READ_BIT(CRS->CR, (__INTERRUPT__)) != 0U) ? SET : RESET) |

Check whether the CRS interrupt has occurred or not.

- Parameters

-

<strong>INTERRUPT</strong> specifies the CRS interrupt source to check. This parameter can be one of the following values: - RCC_CRS_IT_SYNCOK SYNC event OK interrupt

- RCC_CRS_IT_SYNCWARN SYNC warning interrupt

- RCC_CRS_IT_ERR Synchronization or trimming error interrupt

- RCC_CRS_IT_ESYNC Expected SYNC interrupt

- Return values

-

The new state of INTERRUPT (SET or RESET).

Definition at line 3761 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_CRS_GET_IT_SOURCE [2/2]

| #define __HAL_RCC_CRS_GET_IT_SOURCE | ( | __INTERRUPT__ | ) | ((READ_BIT(CRS->CR, (__INTERRUPT__)) != 0U) ? SET : RESET) |

Check whether the CRS interrupt has occurred or not.

- Parameters

-

<strong>INTERRUPT</strong> specifies the CRS interrupt source to check. This parameter can be one of the following values: - RCC_CRS_IT_SYNCOK SYNC event OK interrupt

- RCC_CRS_IT_SYNCWARN SYNC warning interrupt

- RCC_CRS_IT_ERR Synchronization or trimming error interrupt

- RCC_CRS_IT_ESYNC Expected SYNC interrupt

- Return values

-

The new state of INTERRUPT (SET or RESET).

Definition at line 3765 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_DFSDM1_CONFIG [1/2]

| #define __HAL_RCC_DFSDM1_CONFIG | ( | __DFSDM1CLKSource__ | ) | MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL, (uint32_t)(__DFSDM1CLKSource__)) |

Macro to configure the DFSDM1 clock.

- Parameters

-

<strong>DFSDM1CLKSource</strong> specifies the DFSDM1 clock source. This parameter can be one of the following values: - RCC_DFSDM1CLKSOURCE_D2PCLK: D2PCLK Clock selected as DFSDM1 clock

- RCC_DFSDM1CLKSOURCE_SYS: System Clock selected as DFSDM1 clock

Definition at line 3163 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_DFSDM1_CONFIG [2/2]

| #define __HAL_RCC_DFSDM1_CONFIG | ( | __DFSDM1CLKSource__ | ) | MODIFY_REG(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL, (uint32_t)(__DFSDM1CLKSource__)) |

Macro to configure the DFSDM1 clock.

- Parameters

-

<strong>DFSDM1CLKSource</strong> specifies the DFSDM1 clock source. This parameter can be one of the following values: - RCC_DFSDM1CLKSOURCE_D2PCLK: D2PCLK Clock selected as DFSDM1 clock

- RCC_DFSDM1CLKSOURCE_SYS: System Clock selected as DFSDM1 clock

Definition at line 3167 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_FMC_CONFIG [1/2]

| #define __HAL_RCC_FMC_CONFIG | ( | __FMCCLKSource__ | ) | MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_FMCSEL, (uint32_t)(__FMCCLKSource__)) |

macro to configure the FMC clock source.

- Parameters

-

<strong>FMCCLKSource</strong> specifies the FMC clock source. - RCC_RCC_FMCCLKSOURCE_D1HCLK: Domain1 HCLK Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL : PLL1_Q Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL2 : PLL2_R Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_CLKP CLKP selected as FMC clock

Definition at line 3057 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_FMC_CONFIG [2/2]

| #define __HAL_RCC_FMC_CONFIG | ( | __FMCCLKSource__ | ) | MODIFY_REG(RCC->CDCCIPR, RCC_CDCCIPR_FMCSEL, (uint32_t)(__FMCCLKSource__)) |

macro to configure the FMC clock source.

- Parameters

-

<strong>FMCCLKSource</strong> specifies the FMC clock source. - RCC_RCC_FMCCLKSOURCE_D1HCLK: Domain1 HCLK Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL : PLL1_Q Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL2 : PLL2_R Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_CLKP CLKP selected as FMC clock

Definition at line 3061 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_ADC_SOURCE [1/2]

Macro to get the ADC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_ADCCLKSOURCE_PLL2: PLL2_P Clock selected as ADC clock

- RCC_ADCCLKSOURCE_PLL3: PLL3_R Clock selected as ADC clock

- RCC_ADCCLKSOURCE_CLKP: CLKP Clock selected as ADC clock

Definition at line 3125 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_ADC_SOURCE [2/2]

Macro to get the ADC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_ADCCLKSOURCE_PLL2: PLL2_P Clock selected as ADC clock

- RCC_ADCCLKSOURCE_PLL3: PLL3_R Clock selected as ADC clock

- RCC_ADCCLKSOURCE_CLKP: CLKP Clock selected as ADC clock

Definition at line 3129 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_CEC_SOURCE [1/3]

| #define __HAL_RCC_GET_CEC_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_CECSEL))) |

macro to get the CEC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_CECCLKSOURCE_LSE: LSE selected as CEC clock

- RCC_CECCLKSOURCE_HSI: HSI selected as CEC clock

Definition at line 3095 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_CEC_SOURCE [2/3]

macro to get the CEC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_CECCLKSOURCE_LSE: LSE selected as CEC clock

- RCC_CECCLKSOURCE_LSI: LSI selected as CEC clock

- RCC_CECCLKSOURCE_CSI: CSI Clock selected as CEC clock

Definition at line 3221 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_CEC_SOURCE [3/3]

macro to get the CEC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_CECCLKSOURCE_LSE: LSE selected as CEC clock

- RCC_CECCLKSOURCE_LSI: LSI selected as CEC clock

- RCC_CECCLKSOURCE_CSI: CSI Clock selected as CEC clock

Definition at line 3225 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_CLK48_SOURCE

| #define __HAL_RCC_GET_CLK48_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_CK48MSEL))) |

macro to get the CLK48 source.

- Return values

-

The clock source can be one of the following values: - RCC_CLK48SOURCE_PLL: PLL used as CLK48 source

- RCC_CLK48SOURCE_PLLSAIP: PLLSAIP used as CLK48 source

Definition at line 3112 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_CLKP_SOURCE [1/2]

Macro to get the Oscillator clock for peripheral source.

- Return values

-

The clock source can be one of the following values: - RCC_CLKPSOURCE_HSI: HSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_CSI: CSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_HSE: HSE selected Oscillator clock for peripheral

Definition at line 3248 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_CLKP_SOURCE [2/2]

Macro to get the Oscillator clock for peripheral source.

- Return values

-

The clock source can be one of the following values: - RCC_CLKPSOURCE_HSI: HSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_CSI: CSI selected Oscillator clock for peripheral

- RCC_CLKPSOURCE_HSE: HSE selected Oscillator clock for peripheral

Definition at line 3252 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_DFSDM1_SOURCE [1/2]

| #define __HAL_RCC_GET_DFSDM1_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL))) |

Macro to get the DFSDM1 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_DFSDM1CLKSOURCE_D2PCLK: D2PCLK Clock selected as DFSDM1 clock

- RCC_DFSDM1CLKSOURCE_SYS: System Clock selected as DFSDM1 clock

Definition at line 3175 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_DFSDM1_SOURCE [2/2]

| #define __HAL_RCC_GET_DFSDM1_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->CDCCIP1R, RCC_CDCCIP1R_DFSDM1SEL))) |

Macro to get the DFSDM1 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_DFSDM1CLKSOURCE_D2PCLK: D2PCLK Clock selected as DFSDM1 clock

- RCC_DFSDM1CLKSOURCE_SYS: System Clock selected as DFSDM1 clock

Definition at line 3179 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_FMC_SOURCE [1/2]

macro to get the FMC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_RCC_FMCCLKSOURCE_D1HCLK: Domain1 HCLK Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL : PLL1_Q Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL2 : PLL2_R Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_CLKP CLKP selected as FMC clock

Definition at line 3071 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_FMC_SOURCE [2/2]

macro to get the FMC clock source.

- Return values

-

The clock source can be one of the following values: - RCC_RCC_FMCCLKSOURCE_D1HCLK: Domain1 HCLK Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL : PLL1_Q Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_PLL2 : PLL2_R Clock selected as FMC clock

- RCC_RCC_FMCCLKSOURCE_CLKP CLKP selected as FMC clock

Definition at line 3075 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C1235_SOURCE [1/2]

| #define __HAL_RCC_GET_I2C1235_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->D2CCIP2R, RCC_D2CCIP2R_I2C1235SEL))) |

macro to get the I2C1/2/3/5* clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C123CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C1/2/3/5* clock

- RCC_I2C123CLKSOURCE_PLL3: PLL3 selected as I2C1/2/3/5* clock

- RCC_I2C123CLKSOURCE_HSI: HSI selected as I2C1/2/3/5* clock

- RCC_I2C123CLKSOURCE_CSI: CSI selected as I2C1/2/3/5* clock

Definition at line 2293 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C1235_SOURCE [2/2]

| #define __HAL_RCC_GET_I2C1235_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->D2CCIP2R, RCC_D2CCIP2R_I2C1235SEL))) |

macro to get the I2C1/2/3/5* clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C123CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C1/2/3/5* clock

- RCC_I2C123CLKSOURCE_PLL3: PLL3 selected as I2C1/2/3/5* clock

- RCC_I2C123CLKSOURCE_HSI: HSI selected as I2C1/2/3/5* clock

- RCC_I2C123CLKSOURCE_CSI: CSI selected as I2C1/2/3/5* clock

Definition at line 2293 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C123_SOURCE [1/2]

| #define __HAL_RCC_GET_I2C123_SOURCE __HAL_RCC_GET_I2C1235_SOURCE |

Definition at line 2295 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C123_SOURCE [2/2]

| #define __HAL_RCC_GET_I2C123_SOURCE __HAL_RCC_GET_I2C1235_SOURCE |

Definition at line 2295 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C1_SOURCE [1/3]

| #define __HAL_RCC_GET_I2C1_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C1SEL))) |

Macro to get the I2C1 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C1CLKSOURCE_PCLK1: PCLK1 selected as I2C1 clock

- RCC_I2C1CLKSOURCE_HSI: HSI selected as I2C1 clock

- RCC_I2C1CLKSOURCE_SYSCLK: System Clock selected as I2C1 clock

Definition at line 2832 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C1_SOURCE [2/3]

| #define __HAL_RCC_GET_I2C1_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

macro to get the I2C1 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C1CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C1 clock

- RCC_I2C1CLKSOURCE_PLL3: PLL3 selected as I2C1 clock

- RCC_I2C1CLKSOURCE_HSI: HSI selected as I2C1 clock

- RCC_I2C1CLKSOURCE_CSI: CSI selected as I2C1 clock

Definition at line 2323 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C1_SOURCE [3/3]

| #define __HAL_RCC_GET_I2C1_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

macro to get the I2C1 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C1CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C1 clock

- RCC_I2C1CLKSOURCE_PLL3: PLL3 selected as I2C1 clock

- RCC_I2C1CLKSOURCE_HSI: HSI selected as I2C1 clock

- RCC_I2C1CLKSOURCE_CSI: CSI selected as I2C1 clock

Definition at line 2323 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C2_SOURCE [1/3]

| #define __HAL_RCC_GET_I2C2_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C2SEL))) |

Macro to get the I2C2 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C2CLKSOURCE_PCLK1: PCLK1 selected as I2C2 clock

- RCC_I2C2CLKSOURCE_HSI: HSI selected as I2C2 clock

- RCC_I2C2CLKSOURCE_SYSCLK: System Clock selected as I2C2 clock

Definition at line 2851 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C2_SOURCE [2/3]

| #define __HAL_RCC_GET_I2C2_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

macro to get the I2C2 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C2CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C2 clock

- RCC_I2C2CLKSOURCE_PLL3: PLL3 selected as I2C2 clock

- RCC_I2C2CLKSOURCE_HSI: HSI selected as I2C2 clock

- RCC_I2C2CLKSOURCE_CSI: CSI selected as I2C2 clock

Definition at line 2351 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C2_SOURCE [3/3]

| #define __HAL_RCC_GET_I2C2_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

macro to get the I2C2 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C2CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C2 clock

- RCC_I2C2CLKSOURCE_PLL3: PLL3 selected as I2C2 clock

- RCC_I2C2CLKSOURCE_HSI: HSI selected as I2C2 clock

- RCC_I2C2CLKSOURCE_CSI: CSI selected as I2C2 clock

Definition at line 2351 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C3_SOURCE [1/3]

| #define __HAL_RCC_GET_I2C3_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->DCKCFGR2, RCC_DCKCFGR2_I2C3SEL))) |

macro to get the I2C3 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C3CLKSOURCE_PCLK1: PCLK1 selected as I2C3 clock

- RCC_I2C3CLKSOURCE_HSI: HSI selected as I2C3 clock

- RCC_I2C3CLKSOURCE_SYSCLK: System Clock selected as I2C3 clock

Definition at line 2870 of file stm32f7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C3_SOURCE [2/3]

| #define __HAL_RCC_GET_I2C3_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

macro to get the I2C3 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C3CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C3 clock

- RCC_I2C3CLKSOURCE_PLL3: PLL3 selected as I2C3 clock

- RCC_I2C3CLKSOURCE_HSI: HSI selected as I2C3 clock

- RCC_I2C3CLKSOURCE_CSI: CSI selected as I2C3 clock

Definition at line 2379 of file stm32h735/stm32h735g-dk/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C3_SOURCE [3/3]

| #define __HAL_RCC_GET_I2C3_SOURCE __HAL_RCC_GET_I2C123_SOURCE |

macro to get the I2C3 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C3CLKSOURCE_D2PCLK1: D2PCLK1 selected as I2C3 clock

- RCC_I2C3CLKSOURCE_PLL3: PLL3 selected as I2C3 clock

- RCC_I2C3CLKSOURCE_HSI: HSI selected as I2C3 clock

- RCC_I2C3CLKSOURCE_CSI: CSI selected as I2C3 clock

Definition at line 2379 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C4_SOURCE [1/3]

| #define __HAL_RCC_GET_I2C4_SOURCE | ( | ) | ((uint32_t)(READ_BIT(RCC->D3CCIPR, RCC_D3CCIPR_I2C4SEL))) |

macro to get the I2C4 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C4CLKSOURCE_D3PCLK1: D3PCLK1 selected as I2C4 clock

- RCC_I2C4CLKSOURCE_PLL3: PLL3 selected as I2C4 clock

- RCC_I2C4CLKSOURCE_HSI: HSI selected as I2C4 clock

- RCC_I2C4CLKSOURCE_CSI: CSI selected as I2C4 clock

Definition at line 2406 of file stm32h747/stm32h747i-disco/CM7/Drivers/STM32H7xx_HAL_Driver/Inc/stm32h7xx_hal_rcc_ex.h.

◆ __HAL_RCC_GET_I2C4_SOURCE [2/3]

macro to get the I2C4 clock source.

- Return values

-

The clock source can be one of the following values: - RCC_I2C4CLKSOURCE_D3PCLK1: D3PCLK1 selected as I2C4 clock

- RCC_I2C4CLKSOURCE_PLL3: PLL3 selected as I2C4 clock

- RCC_I2C4CLKSOURCE_HSI: HSI selected as I2C4 clock

- RCC_I2C4CLKSOURCE_CSI: CSI selected as I2C4 clock