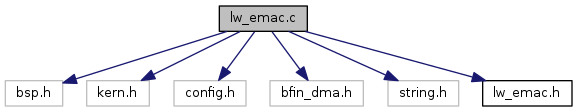

#include <bsp.h>

#include <kern.h>

#include <config.h>

#include <bfin_dma.h>

#include <string.h>

#include "lw_emac.h"

Go to the source code of this file.

|

| static ethernet_data_t rxBuffer[ETH_RX_BUF_SIZE] | __attribute__ ((section(".dma"))) |

| |

| int | bfin_EMAC_init (uint8_t *ethAddr) |

| |

| int | bfin_EMAC_recv (uint8_t *packet, size_t size) |

| |

| int | bfin_EMAC_send (void *packet, int length) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, opmode)==0x0) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, staadd)==0x14) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, wkup_ctl)==0x2c) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, wkup_ffcrc1)==0x4c) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, sysctl)==0x60) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, rx_stat)==0x68) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, mmc_ctl)==0x80) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, mmc_tirqe)==0x90) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, mmc_rxc_ok)==0x100) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, mmc_rxc_dmaovf)==0x110) |

| |

| | COMPILETIME_ASSERT (offsetof(bfin_emac_regs_t, mmc_rxc_ge1024)==0x15c) |

| |

| | COMPILETIME_ASSERT (sizeof(ethernet_data_t)==0x618) |

| |

| static uint8_t | lw_emac_init_registers (uint8_t *ethAddr) |

| |

| static uint32_t | lw_emac_read_phy_reg (uint8_t phy_addr, uint8_t reg_addr) |

| |

| static void | lw_emac_set_mac_addr (uint8_t *ethAddr) |

| |

| static void | lw_emac_write_phy_reg (uint8_t phy_addr, uint8_t reg_addr, uint32_t data) |

| |

| #define ETH_FRAME_SIZE 0x614 |

| #define ETH_RX_BUF_SIZE 2 |

| #define ETH_TX_BUF_SIZE 1 |

| #define MII_ANAR_100_FD BIT (8) /* Can do 100BASE-TX full duplex */ |

| #define MII_ANAR_10_FD BIT (6) /* Can do 10BASE-T full duplex */ |

| #define MII_BMCR 0x00 /* Basic Mode Control Register */ |

| #define MII_BMCR_ANEG_EN BIT (12) |

| #define MII_BMCR_ANEG_RST BIT (9) |

| #define MII_BMCR_RST BIT (15) |

| #define MII_BMSR 0x01 /* Basic Mode Status Register */ |

| #define MII_BMSR_ANEGACK BIT (5) |

| #define MII_BMSR_LINK BIT (2) |

| #define MII_LPAR 0x05 /* Auto-Negotiation Link Partner Ability Register */ |

| #define MII_PHYIDR1 0x02 /* PHY Identifier Register 1 */ |

| #define MII_PHYIDR2 0x03 /* PHY Identifier Register 2 */ |

| #define PHY_MDC_Hz 2500000 |

| int bfin_EMAC_init |

( |

uint8_t * |

ethAddr | ) |

|

| int bfin_EMAC_recv |

( |

uint8_t * |

packet, |

|

|

size_t |

size |

|

) |

| |

| int bfin_EMAC_send |

( |

void * |

packet, |

|

|

int |

length |

|

) |

| |

| static void lw_emac_set_mac_addr |

( |

uint8_t * |

ethAddr | ) |

|

|

static |