Defines |

| #define | CHIP_FLASH_IAP_ADDRESS (IROM_ADDR + 8) |

| #define | RAMFUNC __attribute__ ((section(".ramfunc"))) |

| #define | SAM3XA |

|

| #define | EFC_FCMD_GETD 0x00 |

| | Get Flash Descriptor.

|

| #define | EFC_FCMD_WP 0x01 |

| | Write page.

|

| #define | EFC_FCMD_WPL 0x02 |

| | Write page and lock.

|

| #define | EFC_FCMD_EWP 0x03 |

| | Erase page and write page.

|

| #define | EFC_FCMD_EWPL 0x04 |

| | Erase page and write page then lock.

|

| #define | EFC_FCMD_EA 0x05 |

| | Erase all.

|

| #define | EFC_FCMD_SLB 0x08 |

| | Set Lock Bit.

|

| #define | EFC_FCMD_CLB 0x09 |

| | Clear Lock Bit.

|

| #define | EFC_FCMD_GLB 0x0A |

| | Get Lock Bit.

|

| #define | EFC_FCMD_SGPB 0x0B |

| | Set GPNVM Bit.

|

| #define | EFC_FCMD_CGPB 0x0C |

| | Clear GPNVM Bit.

|

| #define | EFC_FCMD_GGPB 0x0D |

| | Get GPNVM Bit.

|

| #define | EFC_FCMD_STUI 0x0E |

| | Start unique ID.

|

| #define | EFC_FCMD_SPUI 0x0F |

| | Stop unique ID.

|

| #define | EFC_FCMD_GCALB 0x10 |

| | Get CALIB Bit.

|

|

| #define | EFC_ACCESS_MODE_128 0 |

| #define | EFC_ACCESS_MODE_64 EEFC_FMR_FAM |

Functions |

| void | efc_disable_frdy_interrupt (Efc *p_efc) |

| | Disable the flash ready interrupt.

|

| void | efc_enable_frdy_interrupt (Efc *p_efc) |

| | Enable the flash ready interrupt.

|

| uint32_t | efc_get_flash_access_mode (Efc *p_efc) |

| | Get flash access mode.

|

| uint32_t | efc_get_result (Efc *p_efc) |

| | Get the result of the last executed command.

|

| uint32_t | efc_get_status (Efc *p_efc) |

| | Get the current status of the EEFC.

|

| uint32_t | efc_get_wait_state (Efc *p_efc) |

| | Get flash wait state.

|

| uint32_t | efc_init (Efc *p_efc, uint32_t ul_access_mode, uint32_t ul_fws) |

| | Initialize the EFC controller.

|

| uint32_t | efc_perform_command (Efc *p_efc, uint32_t ul_command, uint32_t ul_argument) |

| | Perform the given command and wait until its completion (or an error).

|

| uint32_t | efc_perform_read_sequence (Efc *p_efc, uint32_t ul_cmd_st, uint32_t ul_cmd_sp, uint32_t *p_ul_buf, uint32_t ul_size) |

| | Perform read sequence. Supported sequences are read Unique ID and read User Signature.

|

| void | efc_set_flash_access_mode (Efc *p_efc, uint32_t ul_mode) |

| | Set flash access mode.

|

| void | efc_set_wait_state (Efc *p_efc, uint32_t ul_fws) |

| | Set flash wait state.

|

EFC return codes |

| enum | efc_rc {

EFC_RC_OK = 0,

EFC_RC_YES = 0,

EFC_RC_NO = 1,

EFC_RC_ERROR = 1,

EFC_RC_INVALID,

EFC_RC_NOT_SUPPORT = 0xFFFFFFFF

} |

| typedef enum efc_rc | efc_rc_t |

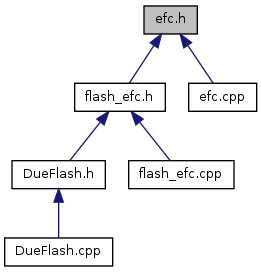

Embedded Flash Controller (EFC) driver for SAM.

Copyright (c) 2011-2012 Atmel Corporation. All rights reserved.

Definition in file efc.h.