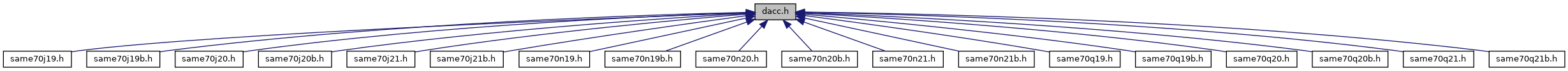

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Dacc |

| Dacc hardware registers. More... | |

Macros | |

| #define | DACC_ACR_IBCTLCH0(value) ((DACC_ACR_IBCTLCH0_Msk & ((value) << DACC_ACR_IBCTLCH0_Pos))) |

| #define | DACC_ACR_IBCTLCH0_Msk (0x3u << DACC_ACR_IBCTLCH0_Pos) |

| (DACC_ACR) Analog Output Current Control More... | |

| #define | DACC_ACR_IBCTLCH0_Pos 0 |

| #define | DACC_ACR_IBCTLCH1(value) ((DACC_ACR_IBCTLCH1_Msk & ((value) << DACC_ACR_IBCTLCH1_Pos))) |

| #define | DACC_ACR_IBCTLCH1_Msk (0x3u << DACC_ACR_IBCTLCH1_Pos) |

| (DACC_ACR) Analog Output Current Control More... | |

| #define | DACC_ACR_IBCTLCH1_Pos 2 |

| #define | DACC_CDR_DATA0(value) ((DACC_CDR_DATA0_Msk & ((value) << DACC_CDR_DATA0_Pos))) |

| #define | DACC_CDR_DATA0_Msk (0xffffu << DACC_CDR_DATA0_Pos) |

| (DACC_CDR[2]) Data to Convert for channel 0 More... | |

| #define | DACC_CDR_DATA0_Pos 0 |

| #define | DACC_CDR_DATA1(value) ((DACC_CDR_DATA1_Msk & ((value) << DACC_CDR_DATA1_Pos))) |

| #define | DACC_CDR_DATA1_Msk (0xffffu << DACC_CDR_DATA1_Pos) |

| (DACC_CDR[2]) Data to Convert for channel 1 More... | |

| #define | DACC_CDR_DATA1_Pos 16 |

| #define | DACC_CHDR_CH0 (0x1u << 0) |

| (DACC_CHDR) Channel 0 Disable More... | |

| #define | DACC_CHDR_CH1 (0x1u << 1) |

| (DACC_CHDR) Channel 1 Disable More... | |

| #define | DACC_CHER_CH0 (0x1u << 0) |

| (DACC_CHER) Channel 0 Enable More... | |

| #define | DACC_CHER_CH1 (0x1u << 1) |

| (DACC_CHER) Channel 1 Enable More... | |

| #define | DACC_CHSR_CH0 (0x1u << 0) |

| (DACC_CHSR) Channel 0 Status More... | |

| #define | DACC_CHSR_CH1 (0x1u << 1) |

| (DACC_CHSR) Channel 1 Status More... | |

| #define | DACC_CHSR_DACRDY0 (0x1u << 8) |

| (DACC_CHSR) DAC ready flag More... | |

| #define | DACC_CHSR_DACRDY1 (0x1u << 9) |

| (DACC_CHSR) DAC ready flag More... | |

| #define | DACC_CR_SWRST (0x1u << 0) |

| (DACC_CR) Software Reset More... | |

| #define | DACC_IDR_ENDTX0 (0x1u << 8) |

| (DACC_IDR) End of Transmit Buffer Interrupt Disable of channel 0 More... | |

| #define | DACC_IDR_ENDTX1 (0x1u << 9) |

| (DACC_IDR) End of Transmit Buffer Interrupt Disable of channel 1 More... | |

| #define | DACC_IDR_EOC0 (0x1u << 4) |

| (DACC_IDR) End of Conversion Interrupt Disable of channel 0 More... | |

| #define | DACC_IDR_EOC1 (0x1u << 5) |

| (DACC_IDR) End of Conversion Interrupt Disable of channel 1 More... | |

| #define | DACC_IDR_TXBUFE0 (0x1u << 12) |

| (DACC_IDR) Transmit Buffer Empty Interrupt Disable of channel 0 More... | |

| #define | DACC_IDR_TXBUFE1 (0x1u << 13) |

| (DACC_IDR) Transmit Buffer Empty Interrupt Disable of channel 1 More... | |

| #define | DACC_IDR_TXRDY0 (0x1u << 0) |

| (DACC_IDR) Transmit Ready Interrupt Disable of channel 0 More... | |

| #define | DACC_IDR_TXRDY1 (0x1u << 1) |

| (DACC_IDR) Transmit Ready Interrupt Disable of channel 1 More... | |

| #define | DACC_IER_ENDTX0 (0x1u << 8) |

| (DACC_IER) End of Transmit Buffer Interrupt Enable of channel 0 More... | |

| #define | DACC_IER_ENDTX1 (0x1u << 9) |

| (DACC_IER) End of Transmit Buffer Interrupt Enable of channel 1 More... | |

| #define | DACC_IER_EOC0 (0x1u << 4) |

| (DACC_IER) End of Conversion Interrupt Enable of channel 0 More... | |

| #define | DACC_IER_EOC1 (0x1u << 5) |

| (DACC_IER) End of Conversion Interrupt Enable of channel 1 More... | |

| #define | DACC_IER_TXBUFE0 (0x1u << 12) |

| (DACC_IER) Transmit Buffer Empty Interrupt Enable of channel 0 More... | |

| #define | DACC_IER_TXBUFE1 (0x1u << 13) |

| (DACC_IER) Transmit Buffer Empty Interrupt Enable of channel 1 More... | |

| #define | DACC_IER_TXRDY0 (0x1u << 0) |

| (DACC_IER) Transmit Ready Interrupt Enable of channel 0 More... | |

| #define | DACC_IER_TXRDY1 (0x1u << 1) |

| (DACC_IER) Transmit Ready Interrupt Enable of channel 1 More... | |

| #define | DACC_IMR_ENDTX0 (0x1u << 8) |

| (DACC_IMR) End of Transmit Buffer Interrupt Mask of channel 0 More... | |

| #define | DACC_IMR_ENDTX1 (0x1u << 9) |

| (DACC_IMR) End of Transmit Buffer Interrupt Mask of channel 1 More... | |

| #define | DACC_IMR_EOC0 (0x1u << 4) |

| (DACC_IMR) End of Conversion Interrupt Mask of channel 0 More... | |

| #define | DACC_IMR_EOC1 (0x1u << 5) |

| (DACC_IMR) End of Conversion Interrupt Mask of channel 1 More... | |

| #define | DACC_IMR_TXBUFE0 (0x1u << 12) |

| (DACC_IMR) Transmit Buffer Empty Interrupt Mask of channel 0 More... | |

| #define | DACC_IMR_TXBUFE1 (0x1u << 13) |

| (DACC_IMR) Transmit Buffer Empty Interrupt Mask of channel 1 More... | |

| #define | DACC_IMR_TXRDY0 (0x1u << 0) |

| (DACC_IMR) Transmit Ready Interrupt Mask of channel 0 More... | |

| #define | DACC_IMR_TXRDY1 (0x1u << 1) |

| (DACC_IMR) Transmit Ready Interrupt Mask of channel 1 More... | |

| #define | DACC_ISR_ENDTX0 (0x1u << 8) |

| (DACC_ISR) End of DMA Interrupt Flag of channel 0 More... | |

| #define | DACC_ISR_ENDTX1 (0x1u << 9) |

| (DACC_ISR) End of DMA Interrupt Flag of channel 1 More... | |

| #define | DACC_ISR_EOC0 (0x1u << 4) |

| (DACC_ISR) End of Conversion Interrupt Flag of channel 0 More... | |

| #define | DACC_ISR_EOC1 (0x1u << 5) |

| (DACC_ISR) End of Conversion Interrupt Flag of channel 1 More... | |

| #define | DACC_ISR_TXBUFE0 (0x1u << 12) |

| (DACC_ISR) Transmit Buffer Empty of channel 0 More... | |

| #define | DACC_ISR_TXBUFE1 (0x1u << 13) |

| (DACC_ISR) Transmit Buffer Empty of channel 1 More... | |

| #define | DACC_ISR_TXRDY0 (0x1u << 0) |

| (DACC_ISR) Transmit Ready Interrupt Flag of channel 0 More... | |

| #define | DACC_ISR_TXRDY1 (0x1u << 1) |

| (DACC_ISR) Transmit Ready Interrupt Flag of channel 1 More... | |

| #define | DACC_MR_DIFF (0x1u << 23) |

| (DACC_MR) Differential Mode More... | |

| #define | DACC_MR_DIFF_DISABLED (0x0u << 23) |

| (DACC_MR) DAC0 and DAC1 outputs can be separately configured More... | |

| #define | DACC_MR_DIFF_ENABLED (0x1u << 23) |

| (DACC_MR) DACP and DACN outputs are configured by the channel 0 value. More... | |

| #define | DACC_MR_MAXS0 (0x1u << 0) |

| (DACC_MR) Max Speed Mode for Channel 0 More... | |

| #define | DACC_MR_MAXS0_MAXIMUM (0x1u << 0) |

| (DACC_MR) Max Speed Mode enabled More... | |

| #define | DACC_MR_MAXS0_TRIG_EVENT (0x0u << 0) |

| (DACC_MR) Triggered by selected event More... | |

| #define | DACC_MR_MAXS1 (0x1u << 1) |

| (DACC_MR) Max Speed Mode for Channel 1 More... | |

| #define | DACC_MR_MAXS1_MAXIMUM (0x1u << 1) |

| (DACC_MR) Max Speed Mode enabled More... | |

| #define | DACC_MR_MAXS1_TRIG_EVENT (0x0u << 1) |

| (DACC_MR) Triggered by selected event More... | |

| #define | DACC_MR_PRESCALER(value) ((DACC_MR_PRESCALER_Msk & ((value) << DACC_MR_PRESCALER_Pos))) |

| #define | DACC_MR_PRESCALER_Msk (0xfu << DACC_MR_PRESCALER_Pos) |

| (DACC_MR) Peripheral Clock to DAC Clock Ratio More... | |

| #define | DACC_MR_PRESCALER_Pos 24 |

| #define | DACC_MR_REFRESH(value) ((DACC_MR_REFRESH_Msk & ((value) << DACC_MR_REFRESH_Pos))) |

| #define | DACC_MR_REFRESH_Msk (0xffu << DACC_MR_REFRESH_Pos) |

| (DACC_MR) Refresh Period More... | |

| #define | DACC_MR_REFRESH_Pos 8 |

| #define | DACC_MR_WORD (0x1u << 4) |

| (DACC_MR) Word Transfer Mode More... | |

| #define | DACC_MR_WORD_DISABLED (0x0u << 4) |

| (DACC_MR) One data to convert is written to the FIFO per access to DACC More... | |

| #define | DACC_MR_WORD_ENABLED (0x1u << 4) |

| (DACC_MR) Two data to convert are written to the FIFO per access to DACC (reduces number of requests to DMA and the number of system bus accesses) More... | |

| #define | DACC_MR_ZERO (0x1u << 5) |

| (DACC_MR) Must always be written to 0. More... | |

| #define | DACC_TRIGR_OSR0(value) ((DACC_TRIGR_OSR0_Msk & ((value) << DACC_TRIGR_OSR0_Pos))) |

| #define | DACC_TRIGR_OSR0_Msk (0x7u << DACC_TRIGR_OSR0_Pos) |

| (DACC_TRIGR) Over Sampling Ratio of Channel 0 More... | |

| #define | DACC_TRIGR_OSR0_OSR_1 (0x0u << 16) |

| (DACC_TRIGR) OSR = 1 More... | |

| #define | DACC_TRIGR_OSR0_OSR_16 (0x4u << 16) |

| (DACC_TRIGR) OSR = 16 More... | |

| #define | DACC_TRIGR_OSR0_OSR_2 (0x1u << 16) |

| (DACC_TRIGR) OSR = 2 More... | |

| #define | DACC_TRIGR_OSR0_OSR_32 (0x5u << 16) |

| (DACC_TRIGR) OSR = 32 More... | |

| #define | DACC_TRIGR_OSR0_OSR_4 (0x2u << 16) |

| (DACC_TRIGR) OSR = 4 More... | |

| #define | DACC_TRIGR_OSR0_OSR_8 (0x3u << 16) |

| (DACC_TRIGR) OSR = 8 More... | |

| #define | DACC_TRIGR_OSR0_Pos 16 |

| #define | DACC_TRIGR_OSR1(value) ((DACC_TRIGR_OSR1_Msk & ((value) << DACC_TRIGR_OSR1_Pos))) |

| #define | DACC_TRIGR_OSR1_Msk (0x7u << DACC_TRIGR_OSR1_Pos) |

| (DACC_TRIGR) Over Sampling Ratio of Channel 1 More... | |

| #define | DACC_TRIGR_OSR1_OSR_1 (0x0u << 20) |

| (DACC_TRIGR) OSR = 1 More... | |

| #define | DACC_TRIGR_OSR1_OSR_16 (0x4u << 20) |

| (DACC_TRIGR) OSR = 16 More... | |

| #define | DACC_TRIGR_OSR1_OSR_2 (0x1u << 20) |

| (DACC_TRIGR) OSR = 2 More... | |

| #define | DACC_TRIGR_OSR1_OSR_32 (0x5u << 20) |

| (DACC_TRIGR) OSR = 32 More... | |

| #define | DACC_TRIGR_OSR1_OSR_4 (0x2u << 20) |

| (DACC_TRIGR) OSR = 4 More... | |

| #define | DACC_TRIGR_OSR1_OSR_8 (0x3u << 20) |

| (DACC_TRIGR) OSR = 8 More... | |

| #define | DACC_TRIGR_OSR1_Pos 20 |

| #define | DACC_TRIGR_TRGEN0 (0x1u << 0) |

| (DACC_TRIGR) Trigger Enable of Channel 0 More... | |

| #define | DACC_TRIGR_TRGEN0_DIS (0x0u << 0) |

| (DACC_TRIGR) External trigger mode disabled. DAC is in free running mode. More... | |

| #define | DACC_TRIGR_TRGEN0_EN (0x1u << 0) |

| (DACC_TRIGR) External trigger mode enabled. More... | |

| #define | DACC_TRIGR_TRGEN1 (0x1u << 1) |

| (DACC_TRIGR) Trigger Enable of Channel 1 More... | |

| #define | DACC_TRIGR_TRGEN1_DIS (0x0u << 1) |

| (DACC_TRIGR) External trigger mode disabled. DAC is in free running mode. More... | |

| #define | DACC_TRIGR_TRGEN1_EN (0x1u << 1) |

| (DACC_TRIGR) External trigger mode enabled. More... | |

| #define | DACC_TRIGR_TRGSEL0(value) ((DACC_TRIGR_TRGSEL0_Msk & ((value) << DACC_TRIGR_TRGSEL0_Pos))) |

| #define | DACC_TRIGR_TRGSEL0_Msk (0x7u << DACC_TRIGR_TRGSEL0_Pos) |

| (DACC_TRIGR) Trigger Selection of Channel 0 More... | |

| #define | DACC_TRIGR_TRGSEL0_Pos 4 |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL0 (0x0u << 4) |

| (DACC_TRIGR) DATRG More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL1 (0x1u << 4) |

| (DACC_TRIGR) TC0 output More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL2 (0x2u << 4) |

| (DACC_TRIGR) TC1 output More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL3 (0x3u << 4) |

| (DACC_TRIGR) TC2 output More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL4 (0x4u << 4) |

| (DACC_TRIGR) PWM0 event 0 More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL5 (0x5u << 4) |

| (DACC_TRIGR) PWM0 event 1 More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL6 (0x6u << 4) |

| (DACC_TRIGR) PWM1 event 0 More... | |

| #define | DACC_TRIGR_TRGSEL0_TRGSEL7 (0x7u << 4) |

| (DACC_TRIGR) PWM1 event 1 More... | |

| #define | DACC_TRIGR_TRGSEL1(value) ((DACC_TRIGR_TRGSEL1_Msk & ((value) << DACC_TRIGR_TRGSEL1_Pos))) |

| #define | DACC_TRIGR_TRGSEL1_Msk (0x7u << DACC_TRIGR_TRGSEL1_Pos) |

| (DACC_TRIGR) Trigger Selection of Channel 1 More... | |

| #define | DACC_TRIGR_TRGSEL1_Pos 8 |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL0 (0x0u << 8) |

| (DACC_TRIGR) DATRG More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL1 (0x1u << 8) |

| (DACC_TRIGR) TC0 output More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL2 (0x2u << 8) |

| (DACC_TRIGR) TC1 output More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL3 (0x3u << 8) |

| (DACC_TRIGR) TC2 output More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL4 (0x4u << 8) |

| (DACC_TRIGR) PWM0 event 0 More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL5 (0x5u << 8) |

| (DACC_TRIGR) PWM0 event 1 More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL6 (0x6u << 8) |

| (DACC_TRIGR) PWM1 event 0 More... | |

| #define | DACC_TRIGR_TRGSEL1_TRGSEL7 (0x7u << 8) |

| (DACC_TRIGR) PWM1 event 1 More... | |

| #define | DACC_VERSION_MFN_Msk (0x7u << DACC_VERSION_MFN_Pos) |

| (DACC_VERSION) Metal Fix Number More... | |

| #define | DACC_VERSION_MFN_Pos 16 |

| #define | DACC_VERSION_VERSION_Msk (0xfffu << DACC_VERSION_VERSION_Pos) |

| (DACC_VERSION) Version More... | |

| #define | DACC_VERSION_VERSION_Pos 0 |

| #define | DACC_WPMR_WPEN (0x1u << 0) |

| (DACC_WPMR) Write Protection Enable More... | |

| #define | DACC_WPMR_WPKEY(value) ((DACC_WPMR_WPKEY_Msk & ((value) << DACC_WPMR_WPKEY_Pos))) |

| #define | DACC_WPMR_WPKEY_Msk (0xffffffu << DACC_WPMR_WPKEY_Pos) |

| (DACC_WPMR) Write Protect Key More... | |

| #define | DACC_WPMR_WPKEY_PASSWD (0x444143u << 8) |

| (DACC_WPMR) Writing any other value in this field aborts the write operation of bit WPEN.Always reads as 0. More... | |

| #define | DACC_WPMR_WPKEY_Pos 8 |

| #define | DACC_WPSR_WPVS (0x1u << 0) |

| (DACC_WPSR) Write Protection Violation Status More... | |

| #define | DACC_WPSR_WPVSRC_Msk (0xffu << DACC_WPSR_WPVSRC_Pos) |

| (DACC_WPSR) Write Protection Violation Source More... | |

| #define | DACC_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/dacc.h.