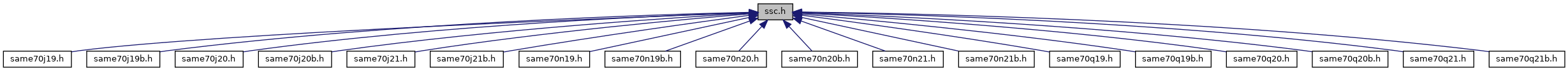

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Ssc |

| Ssc hardware registers. More... | |

Macros | |

| #define | SSC_CMR_DIV(value) ((SSC_CMR_DIV_Msk & ((value) << SSC_CMR_DIV_Pos))) |

| #define | SSC_CMR_DIV_Msk (0xfffu << SSC_CMR_DIV_Pos) |

| (SSC_CMR) Clock Divider More... | |

| #define | SSC_CMR_DIV_Pos 0 |

| #define | SSC_CR_RXDIS (0x1u << 1) |

| (SSC_CR) Receive Disable More... | |

| #define | SSC_CR_RXEN (0x1u << 0) |

| (SSC_CR) Receive Enable More... | |

| #define | SSC_CR_SWRST (0x1u << 15) |

| (SSC_CR) Software Reset More... | |

| #define | SSC_CR_TXDIS (0x1u << 9) |

| (SSC_CR) Transmit Disable More... | |

| #define | SSC_CR_TXEN (0x1u << 8) |

| (SSC_CR) Transmit Enable More... | |

| #define | SSC_IDR_CP0 (0x1u << 8) |

| (SSC_IDR) Compare 0 Interrupt Disable More... | |

| #define | SSC_IDR_CP1 (0x1u << 9) |

| (SSC_IDR) Compare 1 Interrupt Disable More... | |

| #define | SSC_IDR_OVRUN (0x1u << 5) |

| (SSC_IDR) Receive Overrun Interrupt Disable More... | |

| #define | SSC_IDR_RXRDY (0x1u << 4) |

| (SSC_IDR) Receive Ready Interrupt Disable More... | |

| #define | SSC_IDR_RXSYN (0x1u << 11) |

| (SSC_IDR) Rx Sync Interrupt Enable More... | |

| #define | SSC_IDR_TXEMPTY (0x1u << 1) |

| (SSC_IDR) Transmit Empty Interrupt Disable More... | |

| #define | SSC_IDR_TXRDY (0x1u << 0) |

| (SSC_IDR) Transmit Ready Interrupt Disable More... | |

| #define | SSC_IDR_TXSYN (0x1u << 10) |

| (SSC_IDR) Tx Sync Interrupt Enable More... | |

| #define | SSC_IER_CP0 (0x1u << 8) |

| (SSC_IER) Compare 0 Interrupt Enable More... | |

| #define | SSC_IER_CP1 (0x1u << 9) |

| (SSC_IER) Compare 1 Interrupt Enable More... | |

| #define | SSC_IER_OVRUN (0x1u << 5) |

| (SSC_IER) Receive Overrun Interrupt Enable More... | |

| #define | SSC_IER_RXRDY (0x1u << 4) |

| (SSC_IER) Receive Ready Interrupt Enable More... | |

| #define | SSC_IER_RXSYN (0x1u << 11) |

| (SSC_IER) Rx Sync Interrupt Enable More... | |

| #define | SSC_IER_TXEMPTY (0x1u << 1) |

| (SSC_IER) Transmit Empty Interrupt Enable More... | |

| #define | SSC_IER_TXRDY (0x1u << 0) |

| (SSC_IER) Transmit Ready Interrupt Enable More... | |

| #define | SSC_IER_TXSYN (0x1u << 10) |

| (SSC_IER) Tx Sync Interrupt Enable More... | |

| #define | SSC_IMR_CP0 (0x1u << 8) |

| (SSC_IMR) Compare 0 Interrupt Mask More... | |

| #define | SSC_IMR_CP1 (0x1u << 9) |

| (SSC_IMR) Compare 1 Interrupt Mask More... | |

| #define | SSC_IMR_OVRUN (0x1u << 5) |

| (SSC_IMR) Receive Overrun Interrupt Mask More... | |

| #define | SSC_IMR_RXRDY (0x1u << 4) |

| (SSC_IMR) Receive Ready Interrupt Mask More... | |

| #define | SSC_IMR_RXSYN (0x1u << 11) |

| (SSC_IMR) Rx Sync Interrupt Mask More... | |

| #define | SSC_IMR_TXEMPTY (0x1u << 1) |

| (SSC_IMR) Transmit Empty Interrupt Mask More... | |

| #define | SSC_IMR_TXRDY (0x1u << 0) |

| (SSC_IMR) Transmit Ready Interrupt Mask More... | |

| #define | SSC_IMR_TXSYN (0x1u << 10) |

| (SSC_IMR) Tx Sync Interrupt Mask More... | |

| #define | SSC_RC0R_CP0(value) ((SSC_RC0R_CP0_Msk & ((value) << SSC_RC0R_CP0_Pos))) |

| #define | SSC_RC0R_CP0_Msk (0xffffu << SSC_RC0R_CP0_Pos) |

| (SSC_RC0R) Receive Compare Data 0 More... | |

| #define | SSC_RC0R_CP0_Pos 0 |

| #define | SSC_RC1R_CP1(value) ((SSC_RC1R_CP1_Msk & ((value) << SSC_RC1R_CP1_Pos))) |

| #define | SSC_RC1R_CP1_Msk (0xffffu << SSC_RC1R_CP1_Pos) |

| (SSC_RC1R) Receive Compare Data 1 More... | |

| #define | SSC_RC1R_CP1_Pos 0 |

| #define | SSC_RCMR_CKG(value) ((SSC_RCMR_CKG_Msk & ((value) << SSC_RCMR_CKG_Pos))) |

| #define | SSC_RCMR_CKG_CONTINUOUS (0x0u << 6) |

| (SSC_RCMR) None More... | |

| #define | SSC_RCMR_CKG_EN_RF_HIGH (0x2u << 6) |

| (SSC_RCMR) Receive Clock enabled only if RF High More... | |

| #define | SSC_RCMR_CKG_EN_RF_LOW (0x1u << 6) |

| (SSC_RCMR) Receive Clock enabled only if RF Low More... | |

| #define | SSC_RCMR_CKG_Msk (0x3u << SSC_RCMR_CKG_Pos) |

| (SSC_RCMR) Receive Clock Gating Selection More... | |

| #define | SSC_RCMR_CKG_Pos 6 |

| #define | SSC_RCMR_CKI (0x1u << 5) |

| (SSC_RCMR) Receive Clock Inversion More... | |

| #define | SSC_RCMR_CKO(value) ((SSC_RCMR_CKO_Msk & ((value) << SSC_RCMR_CKO_Pos))) |

| #define | SSC_RCMR_CKO_CONTINUOUS (0x1u << 2) |

| (SSC_RCMR) Continuous Receive Clock, RK pin is an output More... | |

| #define | SSC_RCMR_CKO_Msk (0x7u << SSC_RCMR_CKO_Pos) |

| (SSC_RCMR) Receive Clock Output Mode Selection More... | |

| #define | SSC_RCMR_CKO_NONE (0x0u << 2) |

| (SSC_RCMR) None, RK pin is an input More... | |

| #define | SSC_RCMR_CKO_Pos 2 |

| #define | SSC_RCMR_CKO_TRANSFER (0x2u << 2) |

| (SSC_RCMR) Receive Clock only during data transfers, RK pin is an output More... | |

| #define | SSC_RCMR_CKS(value) ((SSC_RCMR_CKS_Msk & ((value) << SSC_RCMR_CKS_Pos))) |

| #define | SSC_RCMR_CKS_MCK (0x0u << 0) |

| (SSC_RCMR) Divided Clock More... | |

| #define | SSC_RCMR_CKS_Msk (0x3u << SSC_RCMR_CKS_Pos) |

| (SSC_RCMR) Receive Clock Selection More... | |

| #define | SSC_RCMR_CKS_Pos 0 |

| #define | SSC_RCMR_CKS_RK (0x2u << 0) |

| (SSC_RCMR) RK pin More... | |

| #define | SSC_RCMR_CKS_TK (0x1u << 0) |

| (SSC_RCMR) TK Clock signal More... | |

| #define | SSC_RCMR_PERIOD(value) ((SSC_RCMR_PERIOD_Msk & ((value) << SSC_RCMR_PERIOD_Pos))) |

| #define | SSC_RCMR_PERIOD_Msk (0xffu << SSC_RCMR_PERIOD_Pos) |

| (SSC_RCMR) Receive Period Divider Selection More... | |

| #define | SSC_RCMR_PERIOD_Pos 24 |

| #define | SSC_RCMR_START(value) ((SSC_RCMR_START_Msk & ((value) << SSC_RCMR_START_Pos))) |

| #define | SSC_RCMR_START_CMP_0 (0x8u << 8) |

| (SSC_RCMR) Compare 0 More... | |

| #define | SSC_RCMR_START_CONTINUOUS (0x0u << 8) |

| (SSC_RCMR) Continuous, as soon as the receiver is enabled, and immediately after the end of transfer of the previous data. More... | |

| #define | SSC_RCMR_START_Msk (0xfu << SSC_RCMR_START_Pos) |

| (SSC_RCMR) Receive Start Selection More... | |

| #define | SSC_RCMR_START_Pos 8 |

| #define | SSC_RCMR_START_RF_EDGE (0x7u << 8) |

| (SSC_RCMR) Detection of any edge on RF signal More... | |

| #define | SSC_RCMR_START_RF_FALLING (0x4u << 8) |

| (SSC_RCMR) Detection of a falling edge on RF signal More... | |

| #define | SSC_RCMR_START_RF_HIGH (0x3u << 8) |

| (SSC_RCMR) Detection of a high level on RF signal More... | |

| #define | SSC_RCMR_START_RF_LEVEL (0x6u << 8) |

| (SSC_RCMR) Detection of any level change on RF signal More... | |

| #define | SSC_RCMR_START_RF_LOW (0x2u << 8) |

| (SSC_RCMR) Detection of a low level on RF signal More... | |

| #define | SSC_RCMR_START_RF_RISING (0x5u << 8) |

| (SSC_RCMR) Detection of a rising edge on RF signal More... | |

| #define | SSC_RCMR_START_TRANSMIT (0x1u << 8) |

| (SSC_RCMR) Transmit start More... | |

| #define | SSC_RCMR_STOP (0x1u << 12) |

| (SSC_RCMR) Receive Stop Selection More... | |

| #define | SSC_RCMR_STTDLY(value) ((SSC_RCMR_STTDLY_Msk & ((value) << SSC_RCMR_STTDLY_Pos))) |

| #define | SSC_RCMR_STTDLY_Msk (0xffu << SSC_RCMR_STTDLY_Pos) |

| (SSC_RCMR) Receive Start Delay More... | |

| #define | SSC_RCMR_STTDLY_Pos 16 |

| #define | SSC_RFMR_DATLEN(value) ((SSC_RFMR_DATLEN_Msk & ((value) << SSC_RFMR_DATLEN_Pos))) |

| #define | SSC_RFMR_DATLEN_Msk (0x1fu << SSC_RFMR_DATLEN_Pos) |

| (SSC_RFMR) Data Length More... | |

| #define | SSC_RFMR_DATLEN_Pos 0 |

| #define | SSC_RFMR_DATNB(value) ((SSC_RFMR_DATNB_Msk & ((value) << SSC_RFMR_DATNB_Pos))) |

| #define | SSC_RFMR_DATNB_Msk (0xfu << SSC_RFMR_DATNB_Pos) |

| (SSC_RFMR) Data Number per Frame More... | |

| #define | SSC_RFMR_DATNB_Pos 8 |

| #define | SSC_RFMR_FSEDGE (0x1u << 24) |

| (SSC_RFMR) Frame Sync Edge Detection More... | |

| #define | SSC_RFMR_FSEDGE_NEGATIVE (0x1u << 24) |

| (SSC_RFMR) Negative Edge Detection More... | |

| #define | SSC_RFMR_FSEDGE_POSITIVE (0x0u << 24) |

| (SSC_RFMR) Positive Edge Detection More... | |

| #define | SSC_RFMR_FSLEN(value) ((SSC_RFMR_FSLEN_Msk & ((value) << SSC_RFMR_FSLEN_Pos))) |

| #define | SSC_RFMR_FSLEN_EXT(value) ((SSC_RFMR_FSLEN_EXT_Msk & ((value) << SSC_RFMR_FSLEN_EXT_Pos))) |

| #define | SSC_RFMR_FSLEN_EXT_Msk (0xfu << SSC_RFMR_FSLEN_EXT_Pos) |

| (SSC_RFMR) FSLEN Field Extension More... | |

| #define | SSC_RFMR_FSLEN_EXT_Pos 28 |

| #define | SSC_RFMR_FSLEN_Msk (0xfu << SSC_RFMR_FSLEN_Pos) |

| (SSC_RFMR) Receive Frame Sync Length More... | |

| #define | SSC_RFMR_FSLEN_Pos 16 |

| #define | SSC_RFMR_FSOS(value) ((SSC_RFMR_FSOS_Msk & ((value) << SSC_RFMR_FSOS_Pos))) |

| #define | SSC_RFMR_FSOS_HIGH (0x4u << 20) |

| (SSC_RFMR) Driven High during data transfer, RF pin is an output More... | |

| #define | SSC_RFMR_FSOS_LOW (0x3u << 20) |

| (SSC_RFMR) Driven Low during data transfer, RF pin is an output More... | |

| #define | SSC_RFMR_FSOS_Msk (0x7u << SSC_RFMR_FSOS_Pos) |

| (SSC_RFMR) Receive Frame Sync Output Selection More... | |

| #define | SSC_RFMR_FSOS_NEGATIVE (0x1u << 20) |

| (SSC_RFMR) Negative Pulse, RF pin is an output More... | |

| #define | SSC_RFMR_FSOS_NONE (0x0u << 20) |

| (SSC_RFMR) None, RF pin is an input More... | |

| #define | SSC_RFMR_FSOS_Pos 20 |

| #define | SSC_RFMR_FSOS_POSITIVE (0x2u << 20) |

| (SSC_RFMR) Positive Pulse, RF pin is an output More... | |

| #define | SSC_RFMR_FSOS_TOGGLING (0x5u << 20) |

| (SSC_RFMR) Toggling at each start of data transfer, RF pin is an output More... | |

| #define | SSC_RFMR_LOOP (0x1u << 5) |

| (SSC_RFMR) Loop Mode More... | |

| #define | SSC_RFMR_MSBF (0x1u << 7) |

| (SSC_RFMR) Most Significant Bit First More... | |

| #define | SSC_RHR_RDAT_Msk (0xffffffffu << SSC_RHR_RDAT_Pos) |

| (SSC_RHR) Receive Data More... | |

| #define | SSC_RHR_RDAT_Pos 0 |

| #define | SSC_RSHR_RSDAT_Msk (0xffffu << SSC_RSHR_RSDAT_Pos) |

| (SSC_RSHR) Receive Synchronization Data More... | |

| #define | SSC_RSHR_RSDAT_Pos 0 |

| #define | SSC_SR_CP0 (0x1u << 8) |

| (SSC_SR) Compare 0 More... | |

| #define | SSC_SR_CP1 (0x1u << 9) |

| (SSC_SR) Compare 1 More... | |

| #define | SSC_SR_OVRUN (0x1u << 5) |

| (SSC_SR) Receive Overrun More... | |

| #define | SSC_SR_RXEN (0x1u << 17) |

| (SSC_SR) Receive Enable More... | |

| #define | SSC_SR_RXRDY (0x1u << 4) |

| (SSC_SR) Receive Ready More... | |

| #define | SSC_SR_RXSYN (0x1u << 11) |

| (SSC_SR) Receive Sync More... | |

| #define | SSC_SR_TXEMPTY (0x1u << 1) |

| (SSC_SR) Transmit Empty More... | |

| #define | SSC_SR_TXEN (0x1u << 16) |

| (SSC_SR) Transmit Enable More... | |

| #define | SSC_SR_TXRDY (0x1u << 0) |

| (SSC_SR) Transmit Ready More... | |

| #define | SSC_SR_TXSYN (0x1u << 10) |

| (SSC_SR) Transmit Sync More... | |

| #define | SSC_TCMR_CKG(value) ((SSC_TCMR_CKG_Msk & ((value) << SSC_TCMR_CKG_Pos))) |

| #define | SSC_TCMR_CKG_CONTINUOUS (0x0u << 6) |

| (SSC_TCMR) None More... | |

| #define | SSC_TCMR_CKG_EN_TF_HIGH (0x2u << 6) |

| (SSC_TCMR) Transmit Clock enabled only if TF High More... | |

| #define | SSC_TCMR_CKG_EN_TF_LOW (0x1u << 6) |

| (SSC_TCMR) Transmit Clock enabled only if TF Low More... | |

| #define | SSC_TCMR_CKG_Msk (0x3u << SSC_TCMR_CKG_Pos) |

| (SSC_TCMR) Transmit Clock Gating Selection More... | |

| #define | SSC_TCMR_CKG_Pos 6 |

| #define | SSC_TCMR_CKI (0x1u << 5) |

| (SSC_TCMR) Transmit Clock Inversion More... | |

| #define | SSC_TCMR_CKO(value) ((SSC_TCMR_CKO_Msk & ((value) << SSC_TCMR_CKO_Pos))) |

| #define | SSC_TCMR_CKO_CONTINUOUS (0x1u << 2) |

| (SSC_TCMR) Continuous Transmit Clock, TK pin is an output More... | |

| #define | SSC_TCMR_CKO_Msk (0x7u << SSC_TCMR_CKO_Pos) |

| (SSC_TCMR) Transmit Clock Output Mode Selection More... | |

| #define | SSC_TCMR_CKO_NONE (0x0u << 2) |

| (SSC_TCMR) None, TK pin is an input More... | |

| #define | SSC_TCMR_CKO_Pos 2 |

| #define | SSC_TCMR_CKO_TRANSFER (0x2u << 2) |

| (SSC_TCMR) Transmit Clock only during data transfers, TK pin is an output More... | |

| #define | SSC_TCMR_CKS(value) ((SSC_TCMR_CKS_Msk & ((value) << SSC_TCMR_CKS_Pos))) |

| #define | SSC_TCMR_CKS_MCK (0x0u << 0) |

| (SSC_TCMR) Divided Clock More... | |

| #define | SSC_TCMR_CKS_Msk (0x3u << SSC_TCMR_CKS_Pos) |

| (SSC_TCMR) Transmit Clock Selection More... | |

| #define | SSC_TCMR_CKS_Pos 0 |

| #define | SSC_TCMR_CKS_RK (0x1u << 0) |

| (SSC_TCMR) RK Clock signal More... | |

| #define | SSC_TCMR_CKS_TK (0x2u << 0) |

| (SSC_TCMR) TK pin More... | |

| #define | SSC_TCMR_PERIOD(value) ((SSC_TCMR_PERIOD_Msk & ((value) << SSC_TCMR_PERIOD_Pos))) |

| #define | SSC_TCMR_PERIOD_Msk (0xffu << SSC_TCMR_PERIOD_Pos) |

| (SSC_TCMR) Transmit Period Divider Selection More... | |

| #define | SSC_TCMR_PERIOD_Pos 24 |

| #define | SSC_TCMR_START(value) ((SSC_TCMR_START_Msk & ((value) << SSC_TCMR_START_Pos))) |

| #define | SSC_TCMR_START_CONTINUOUS (0x0u << 8) |

| (SSC_TCMR) Continuous, as soon as a word is written in the SSC_THR (if Transmit is enabled), and immediately after the end of transfer of the previous data More... | |

| #define | SSC_TCMR_START_Msk (0xfu << SSC_TCMR_START_Pos) |

| (SSC_TCMR) Transmit Start Selection More... | |

| #define | SSC_TCMR_START_Pos 8 |

| #define | SSC_TCMR_START_RECEIVE (0x1u << 8) |

| (SSC_TCMR) Receive start More... | |

| #define | SSC_TCMR_START_TF_EDGE (0x7u << 8) |

| (SSC_TCMR) Detection of any edge on TF signal More... | |

| #define | SSC_TCMR_START_TF_FALLING (0x4u << 8) |

| (SSC_TCMR) Detection of a falling edge on TF signal More... | |

| #define | SSC_TCMR_START_TF_HIGH (0x3u << 8) |

| (SSC_TCMR) Detection of a high level on TF signal More... | |

| #define | SSC_TCMR_START_TF_LEVEL (0x6u << 8) |

| (SSC_TCMR) Detection of any level change on TF signal More... | |

| #define | SSC_TCMR_START_TF_LOW (0x2u << 8) |

| (SSC_TCMR) Detection of a low level on TF signal More... | |

| #define | SSC_TCMR_START_TF_RISING (0x5u << 8) |

| (SSC_TCMR) Detection of a rising edge on TF signal More... | |

| #define | SSC_TCMR_STTDLY(value) ((SSC_TCMR_STTDLY_Msk & ((value) << SSC_TCMR_STTDLY_Pos))) |

| #define | SSC_TCMR_STTDLY_Msk (0xffu << SSC_TCMR_STTDLY_Pos) |

| (SSC_TCMR) Transmit Start Delay More... | |

| #define | SSC_TCMR_STTDLY_Pos 16 |

| #define | SSC_TFMR_DATDEF (0x1u << 5) |

| (SSC_TFMR) Data Default Value More... | |

| #define | SSC_TFMR_DATLEN(value) ((SSC_TFMR_DATLEN_Msk & ((value) << SSC_TFMR_DATLEN_Pos))) |

| #define | SSC_TFMR_DATLEN_Msk (0x1fu << SSC_TFMR_DATLEN_Pos) |

| (SSC_TFMR) Data Length More... | |

| #define | SSC_TFMR_DATLEN_Pos 0 |

| #define | SSC_TFMR_DATNB(value) ((SSC_TFMR_DATNB_Msk & ((value) << SSC_TFMR_DATNB_Pos))) |

| #define | SSC_TFMR_DATNB_Msk (0xfu << SSC_TFMR_DATNB_Pos) |

| (SSC_TFMR) Data Number per Frame More... | |

| #define | SSC_TFMR_DATNB_Pos 8 |

| #define | SSC_TFMR_FSDEN (0x1u << 23) |

| (SSC_TFMR) Frame Sync Data Enable More... | |

| #define | SSC_TFMR_FSEDGE (0x1u << 24) |

| (SSC_TFMR) Frame Sync Edge Detection More... | |

| #define | SSC_TFMR_FSEDGE_NEGATIVE (0x1u << 24) |

| (SSC_TFMR) Negative Edge Detection More... | |

| #define | SSC_TFMR_FSEDGE_POSITIVE (0x0u << 24) |

| (SSC_TFMR) Positive Edge Detection More... | |

| #define | SSC_TFMR_FSLEN(value) ((SSC_TFMR_FSLEN_Msk & ((value) << SSC_TFMR_FSLEN_Pos))) |

| #define | SSC_TFMR_FSLEN_EXT(value) ((SSC_TFMR_FSLEN_EXT_Msk & ((value) << SSC_TFMR_FSLEN_EXT_Pos))) |

| #define | SSC_TFMR_FSLEN_EXT_Msk (0xfu << SSC_TFMR_FSLEN_EXT_Pos) |

| (SSC_TFMR) FSLEN Field Extension More... | |

| #define | SSC_TFMR_FSLEN_EXT_Pos 28 |

| #define | SSC_TFMR_FSLEN_Msk (0xfu << SSC_TFMR_FSLEN_Pos) |

| (SSC_TFMR) Transmit Frame Sync Length More... | |

| #define | SSC_TFMR_FSLEN_Pos 16 |

| #define | SSC_TFMR_FSOS(value) ((SSC_TFMR_FSOS_Msk & ((value) << SSC_TFMR_FSOS_Pos))) |

| #define | SSC_TFMR_FSOS_HIGH (0x4u << 20) |

| (SSC_TFMR) Driven High during data transfer More... | |

| #define | SSC_TFMR_FSOS_LOW (0x3u << 20) |

| (SSC_TFMR) Driven Low during data transfer More... | |

| #define | SSC_TFMR_FSOS_Msk (0x7u << SSC_TFMR_FSOS_Pos) |

| (SSC_TFMR) Transmit Frame Sync Output Selection More... | |

| #define | SSC_TFMR_FSOS_NEGATIVE (0x1u << 20) |

| (SSC_TFMR) Negative Pulse, TF pin is an output More... | |

| #define | SSC_TFMR_FSOS_NONE (0x0u << 20) |

| (SSC_TFMR) None, TF pin is an input More... | |

| #define | SSC_TFMR_FSOS_Pos 20 |

| #define | SSC_TFMR_FSOS_POSITIVE (0x2u << 20) |

| (SSC_TFMR) Positive Pulse, TF pin is an output More... | |

| #define | SSC_TFMR_FSOS_TOGGLING (0x5u << 20) |

| (SSC_TFMR) Toggling at each start of data transfer More... | |

| #define | SSC_TFMR_MSBF (0x1u << 7) |

| (SSC_TFMR) Most Significant Bit First More... | |

| #define | SSC_THR_TDAT(value) ((SSC_THR_TDAT_Msk & ((value) << SSC_THR_TDAT_Pos))) |

| #define | SSC_THR_TDAT_Msk (0xffffffffu << SSC_THR_TDAT_Pos) |

| (SSC_THR) Transmit Data More... | |

| #define | SSC_THR_TDAT_Pos 0 |

| #define | SSC_TSHR_TSDAT(value) ((SSC_TSHR_TSDAT_Msk & ((value) << SSC_TSHR_TSDAT_Pos))) |

| #define | SSC_TSHR_TSDAT_Msk (0xffffu << SSC_TSHR_TSDAT_Pos) |

| (SSC_TSHR) Transmit Synchronization Data More... | |

| #define | SSC_TSHR_TSDAT_Pos 0 |

| #define | SSC_VERSION_MFN_Msk (0x7u << SSC_VERSION_MFN_Pos) |

| (SSC_VERSION) Metal Fix Number More... | |

| #define | SSC_VERSION_MFN_Pos 16 |

| #define | SSC_VERSION_VERSION_Msk (0xffffu << SSC_VERSION_VERSION_Pos) |

| (SSC_VERSION) Version of the Hardware Module More... | |

| #define | SSC_VERSION_VERSION_Pos 0 |

| #define | SSC_WPMR_WPEN (0x1u << 0) |

| (SSC_WPMR) Write Protection Enable More... | |

| #define | SSC_WPMR_WPKEY(value) ((SSC_WPMR_WPKEY_Msk & ((value) << SSC_WPMR_WPKEY_Pos))) |

| #define | SSC_WPMR_WPKEY_Msk (0xffffffu << SSC_WPMR_WPKEY_Pos) |

| (SSC_WPMR) Write Protection Key More... | |

| #define | SSC_WPMR_WPKEY_PASSWD (0x535343u << 8) |

| (SSC_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | SSC_WPMR_WPKEY_Pos 8 |

| #define | SSC_WPSR_WPVS (0x1u << 0) |

| (SSC_WPSR) Write Protection Violation Status More... | |

| #define | SSC_WPSR_WPVSRC_Msk (0xffffu << SSC_WPSR_WPVSRC_Pos) |

| (SSC_WPSR) Write Protect Violation Source More... | |

| #define | SSC_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/ssc.h.