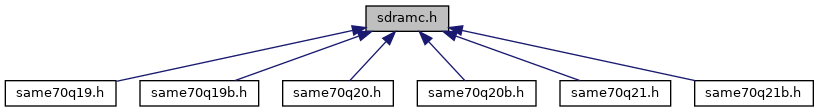

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Sdramc |

| Sdramc hardware registers. More... | |

Macros | |

| #define | SDRAMC_CFR1_TMRD(value) ((SDRAMC_CFR1_TMRD_Msk & ((value) << SDRAMC_CFR1_TMRD_Pos))) |

| #define | SDRAMC_CFR1_TMRD_Msk (0xfu << SDRAMC_CFR1_TMRD_Pos) |

| (SDRAMC_CFR1) Load Mode Register Command to Active or Refresh Command More... | |

| #define | SDRAMC_CFR1_TMRD_Pos 0 |

| #define | SDRAMC_CFR1_UNAL (0x1u << 8) |

| (SDRAMC_CFR1) Support Unaligned Access More... | |

| #define | SDRAMC_CFR1_UNAL_SUPPORTED (0x1u << 8) |

| (SDRAMC_CFR1) Unaligned access is supported. More... | |

| #define | SDRAMC_CFR1_UNAL_UNSUPPORTED (0x0u << 8) |

| (SDRAMC_CFR1) Unaligned access is not supported. More... | |

| #define | SDRAMC_CR_CAS(value) ((SDRAMC_CR_CAS_Msk & ((value) << SDRAMC_CR_CAS_Pos))) |

| #define | SDRAMC_CR_CAS_LATENCY1 (0x1u << 5) |

| (SDRAMC_CR) 1 cycle CAS latency More... | |

| #define | SDRAMC_CR_CAS_LATENCY2 (0x2u << 5) |

| (SDRAMC_CR) 2 cycle CAS latency More... | |

| #define | SDRAMC_CR_CAS_LATENCY3 (0x3u << 5) |

| (SDRAMC_CR) 3 cycle CAS latency More... | |

| #define | SDRAMC_CR_CAS_Msk (0x3u << SDRAMC_CR_CAS_Pos) |

| (SDRAMC_CR) CAS Latency More... | |

| #define | SDRAMC_CR_CAS_Pos 5 |

| #define | SDRAMC_CR_DBW (0x1u << 7) |

| (SDRAMC_CR) Data Bus Width More... | |

| #define | SDRAMC_CR_NB (0x1u << 4) |

| (SDRAMC_CR) Number of Banks More... | |

| #define | SDRAMC_CR_NB_BANK2 (0x0u << 4) |

| (SDRAMC_CR) 2 banks More... | |

| #define | SDRAMC_CR_NB_BANK4 (0x1u << 4) |

| (SDRAMC_CR) 4 banks More... | |

| #define | SDRAMC_CR_NC(value) ((SDRAMC_CR_NC_Msk & ((value) << SDRAMC_CR_NC_Pos))) |

| #define | SDRAMC_CR_NC_COL10 (0x2u << 0) |

| (SDRAMC_CR) 10 column bits More... | |

| #define | SDRAMC_CR_NC_COL11 (0x3u << 0) |

| (SDRAMC_CR) 11 column bits More... | |

| #define | SDRAMC_CR_NC_COL8 (0x0u << 0) |

| (SDRAMC_CR) 8 column bits More... | |

| #define | SDRAMC_CR_NC_COL9 (0x1u << 0) |

| (SDRAMC_CR) 9 column bits More... | |

| #define | SDRAMC_CR_NC_Msk (0x3u << SDRAMC_CR_NC_Pos) |

| (SDRAMC_CR) Number of Column Bits More... | |

| #define | SDRAMC_CR_NC_Pos 0 |

| #define | SDRAMC_CR_NR(value) ((SDRAMC_CR_NR_Msk & ((value) << SDRAMC_CR_NR_Pos))) |

| #define | SDRAMC_CR_NR_Msk (0x3u << SDRAMC_CR_NR_Pos) |

| (SDRAMC_CR) Number of Row Bits More... | |

| #define | SDRAMC_CR_NR_Pos 2 |

| #define | SDRAMC_CR_NR_ROW11 (0x0u << 2) |

| (SDRAMC_CR) 11 row bits More... | |

| #define | SDRAMC_CR_NR_ROW12 (0x1u << 2) |

| (SDRAMC_CR) 12 row bits More... | |

| #define | SDRAMC_CR_NR_ROW13 (0x2u << 2) |

| (SDRAMC_CR) 13 row bits More... | |

| #define | SDRAMC_CR_TRAS(value) ((SDRAMC_CR_TRAS_Msk & ((value) << SDRAMC_CR_TRAS_Pos))) |

| #define | SDRAMC_CR_TRAS_Msk (0xfu << SDRAMC_CR_TRAS_Pos) |

| (SDRAMC_CR) Active to Precharge Delay More... | |

| #define | SDRAMC_CR_TRAS_Pos 24 |

| #define | SDRAMC_CR_TRC_TRFC(value) ((SDRAMC_CR_TRC_TRFC_Msk & ((value) << SDRAMC_CR_TRC_TRFC_Pos))) |

| #define | SDRAMC_CR_TRC_TRFC_Msk (0xfu << SDRAMC_CR_TRC_TRFC_Pos) |

| (SDRAMC_CR) Row Cycle Delay and Row Refresh Cycle More... | |

| #define | SDRAMC_CR_TRC_TRFC_Pos 12 |

| #define | SDRAMC_CR_TRCD(value) ((SDRAMC_CR_TRCD_Msk & ((value) << SDRAMC_CR_TRCD_Pos))) |

| #define | SDRAMC_CR_TRCD_Msk (0xfu << SDRAMC_CR_TRCD_Pos) |

| (SDRAMC_CR) Row to Column Delay More... | |

| #define | SDRAMC_CR_TRCD_Pos 20 |

| #define | SDRAMC_CR_TRP(value) ((SDRAMC_CR_TRP_Msk & ((value) << SDRAMC_CR_TRP_Pos))) |

| #define | SDRAMC_CR_TRP_Msk (0xfu << SDRAMC_CR_TRP_Pos) |

| (SDRAMC_CR) Row Precharge Delay More... | |

| #define | SDRAMC_CR_TRP_Pos 16 |

| #define | SDRAMC_CR_TWR(value) ((SDRAMC_CR_TWR_Msk & ((value) << SDRAMC_CR_TWR_Pos))) |

| #define | SDRAMC_CR_TWR_Msk (0xfu << SDRAMC_CR_TWR_Pos) |

| (SDRAMC_CR) Write Recovery Delay More... | |

| #define | SDRAMC_CR_TWR_Pos 8 |

| #define | SDRAMC_CR_TXSR(value) ((SDRAMC_CR_TXSR_Msk & ((value) << SDRAMC_CR_TXSR_Pos))) |

| #define | SDRAMC_CR_TXSR_Msk (0xfu << SDRAMC_CR_TXSR_Pos) |

| (SDRAMC_CR) Exit Self Refresh to Active Delay More... | |

| #define | SDRAMC_CR_TXSR_Pos 28 |

| #define | SDRAMC_IDR_RES (0x1u << 0) |

| (SDRAMC_IDR) Refresh Error Status More... | |

| #define | SDRAMC_IER_RES (0x1u << 0) |

| (SDRAMC_IER) Refresh Error Status More... | |

| #define | SDRAMC_IMR_RES (0x1u << 0) |

| (SDRAMC_IMR) Refresh Error Status More... | |

| #define | SDRAMC_ISR_RES (0x1u << 0) |

| (SDRAMC_ISR) Refresh Error Status (cleared on read) More... | |

| #define | SDRAMC_LPR_DS(value) ((SDRAMC_LPR_DS_Msk & ((value) << SDRAMC_LPR_DS_Pos))) |

| #define | SDRAMC_LPR_DS_Msk (0x3u << SDRAMC_LPR_DS_Pos) |

| (SDRAMC_LPR) Drive Strength (only for low-power SDRAM) More... | |

| #define | SDRAMC_LPR_DS_Pos 10 |

| #define | SDRAMC_LPR_LPCB(value) ((SDRAMC_LPR_LPCB_Msk & ((value) << SDRAMC_LPR_LPCB_Pos))) |

| #define | SDRAMC_LPR_LPCB_DEEP_POWER_DOWN (0x3u << 0) |

| (SDRAMC_LPR) The SDRAMC issues a Deep Power-down command to the SDRAM device. This mode is unique to low-power SDRAM. More... | |

| #define | SDRAMC_LPR_LPCB_DISABLED (0x0u << 0) |

| (SDRAMC_LPR) Low Power Feature is inhibited: no Power-down, Self-refresh or Deep Power-down command is issued to the SDRAM device. More... | |

| #define | SDRAMC_LPR_LPCB_Msk (0x3u << SDRAMC_LPR_LPCB_Pos) |

| (SDRAMC_LPR) Low-power Configuration Bits More... | |

| #define | SDRAMC_LPR_LPCB_Pos 0 |

| #define | SDRAMC_LPR_LPCB_POWER_DOWN (0x2u << 0) |

| (SDRAMC_LPR) The SDRAMC issues a Power-down Command to the SDRAM device after each access, the SDCKE signal is set to low. The SDRAM device leaves the Power-down Mode when accessed and enters it after the access. More... | |

| #define | SDRAMC_LPR_LPCB_SELF_REFRESH (0x1u << 0) |

| (SDRAMC_LPR) The SDRAMC issues a Self-refresh command to the SDRAM device, the SDCK clock is deactivated and the SDCKE signal is set low. The SDRAM device leaves the Self Refresh Mode when accessed and enters it after the access. More... | |

| #define | SDRAMC_LPR_PASR(value) ((SDRAMC_LPR_PASR_Msk & ((value) << SDRAMC_LPR_PASR_Pos))) |

| #define | SDRAMC_LPR_PASR_Msk (0x7u << SDRAMC_LPR_PASR_Pos) |

| (SDRAMC_LPR) Partial Array Self-refresh (only for low-power SDRAM) More... | |

| #define | SDRAMC_LPR_PASR_Pos 4 |

| #define | SDRAMC_LPR_TCSR(value) ((SDRAMC_LPR_TCSR_Msk & ((value) << SDRAMC_LPR_TCSR_Pos))) |

| #define | SDRAMC_LPR_TCSR_Msk (0x3u << SDRAMC_LPR_TCSR_Pos) |

| (SDRAMC_LPR) Temperature Compensated Self-Refresh (only for low-power SDRAM) More... | |

| #define | SDRAMC_LPR_TCSR_Pos 8 |

| #define | SDRAMC_LPR_TIMEOUT(value) ((SDRAMC_LPR_TIMEOUT_Msk & ((value) << SDRAMC_LPR_TIMEOUT_Pos))) |

| #define | SDRAMC_LPR_TIMEOUT_LP_LAST_XFER (0x0u << 12) |

| (SDRAMC_LPR) The SDRAMC activates the SDRAM low-power mode immediately after the end of the last transfer. More... | |

| #define | SDRAMC_LPR_TIMEOUT_LP_LAST_XFER_128 (0x2u << 12) |

| (SDRAMC_LPR) The SDRAMC activates the SDRAM low-power mode 128 clock cycles after the end of the last transfer. More... | |

| #define | SDRAMC_LPR_TIMEOUT_LP_LAST_XFER_64 (0x1u << 12) |

| (SDRAMC_LPR) The SDRAMC activates the SDRAM low-power mode 64 clock cycles after the end of the last transfer. More... | |

| #define | SDRAMC_LPR_TIMEOUT_Msk (0x3u << SDRAMC_LPR_TIMEOUT_Pos) |

| (SDRAMC_LPR) Time to Define When Low-power Mode Is Enabled More... | |

| #define | SDRAMC_LPR_TIMEOUT_Pos 12 |

| #define | SDRAMC_MDR_MD(value) ((SDRAMC_MDR_MD_Msk & ((value) << SDRAMC_MDR_MD_Pos))) |

| #define | SDRAMC_MDR_MD_LPSDRAM (0x1u << 0) |

| (SDRAMC_MDR) Low-power SDRAM More... | |

| #define | SDRAMC_MDR_MD_Msk (0x3u << SDRAMC_MDR_MD_Pos) |

| (SDRAMC_MDR) Memory Device Type More... | |

| #define | SDRAMC_MDR_MD_Pos 0 |

| #define | SDRAMC_MDR_MD_SDRAM (0x0u << 0) |

| (SDRAMC_MDR) SDRAM More... | |

| #define | SDRAMC_MR_MODE(value) ((SDRAMC_MR_MODE_Msk & ((value) << SDRAMC_MR_MODE_Pos))) |

| #define | SDRAMC_MR_MODE_ALLBANKS_PRECHARGE (0x2u << 0) |

| (SDRAMC_MR) The SDRAMC issues an "All Banks Precharge" command when the SDRAM device is accessed regardless of the cycle. To activate this mode, command must be followed by a write to the SDRAM. More... | |

| #define | SDRAMC_MR_MODE_AUTO_REFRESH (0x4u << 0) |

| (SDRAMC_MR) The SDRAMC issues an "Auto-Refresh" Command when the SDRAM device is accessed regardless of the cycle. Previously, an "All Banks Precharge" command must be issued. To activate this mode, command must be followed by a write to the SDRAM. More... | |

| #define | SDRAMC_MR_MODE_DEEP_POWERDOWN (0x6u << 0) |

| (SDRAMC_MR) Deep power-down mode. Enters deep power-down mode. More... | |

| #define | SDRAMC_MR_MODE_EXT_LOAD_MODEREG (0x5u << 0) |

| (SDRAMC_MR) The SDRAMC issues an "Extended Load Mode Register" command when the SDRAM device is accessed regardless of the cycle. To activate this mode, the "Extended Load Mode Register" command must be followed by a write to the SDRAM. The write in the SDRAM must be done in the appropriate bank; most low-power SDRAM devices use the bank 1. More... | |

| #define | SDRAMC_MR_MODE_LOAD_MODEREG (0x3u << 0) |

| (SDRAMC_MR) The SDRAMC issues a "Load Mode Register" command when the SDRAM device is accessed regardless of the cycle. To activate this mode, command must be followed by a write to the SDRAM. More... | |

| #define | SDRAMC_MR_MODE_Msk (0x7u << SDRAMC_MR_MODE_Pos) |

| (SDRAMC_MR) SDRAMC Command Mode More... | |

| #define | SDRAMC_MR_MODE_NOP (0x1u << 0) |

| (SDRAMC_MR) The SDRAMC issues a NOP command when the SDRAM device is accessed regardless of the cycle. To activate this mode, command must be followed by a write to the SDRAM. More... | |

| #define | SDRAMC_MR_MODE_NORMAL (0x0u << 0) |

| (SDRAMC_MR) Normal mode. Any access to the SDRAM is decoded normally. To activate this mode, command must be followed by a write to the SDRAM. More... | |

| #define | SDRAMC_MR_MODE_Pos 0 |

| #define | SDRAMC_OCMS_KEY1_KEY1(value) ((SDRAMC_OCMS_KEY1_KEY1_Msk & ((value) << SDRAMC_OCMS_KEY1_KEY1_Pos))) |

| #define | SDRAMC_OCMS_KEY1_KEY1_Msk (0xffffffffu << SDRAMC_OCMS_KEY1_KEY1_Pos) |

| (SDRAMC_OCMS_KEY1) Off-chip Memory Scrambling (OCMS) Key Part 1 More... | |

| #define | SDRAMC_OCMS_KEY1_KEY1_Pos 0 |

| #define | SDRAMC_OCMS_KEY2_KEY2(value) ((SDRAMC_OCMS_KEY2_KEY2_Msk & ((value) << SDRAMC_OCMS_KEY2_KEY2_Pos))) |

| #define | SDRAMC_OCMS_KEY2_KEY2_Msk (0xffffffffu << SDRAMC_OCMS_KEY2_KEY2_Pos) |

| (SDRAMC_OCMS_KEY2) Off-chip Memory Scrambling (OCMS) Key Part 2 More... | |

| #define | SDRAMC_OCMS_KEY2_KEY2_Pos 0 |

| #define | SDRAMC_OCMS_SDR_SE (0x1u << 0) |

| (SDRAMC_OCMS) SDRAM Memory Controller Scrambling Enable More... | |

| #define | SDRAMC_TR_COUNT(value) ((SDRAMC_TR_COUNT_Msk & ((value) << SDRAMC_TR_COUNT_Pos))) |

| #define | SDRAMC_TR_COUNT_Msk (0xfffu << SDRAMC_TR_COUNT_Pos) |

| (SDRAMC_TR) SDRAMC Refresh Timer Count More... | |

| #define | SDRAMC_TR_COUNT_Pos 0 |

| #define | SDRAMC_VERSION_MFN_Msk (0x7u << SDRAMC_VERSION_MFN_Pos) |

| (SDRAMC_VERSION) Metal Fix Number More... | |

| #define | SDRAMC_VERSION_MFN_Pos 16 |

| #define | SDRAMC_VERSION_VERSION_Msk (0xfffu << SDRAMC_VERSION_VERSION_Pos) |

| (SDRAMC_VERSION) Version of the Hardware Module More... | |

| #define | SDRAMC_VERSION_VERSION_Pos 0 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/sdramc.h.