This file provides firmware functions to manage the following functionalities of the 7 analog comparators (COMP1, COMP2...COMP7) peripheral: More...

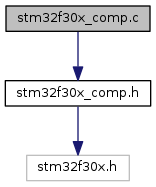

#include "stm32f30x_comp.h"

Go to the source code of this file.

Macros | |

| #define | COMP_CSR_CLEAR_MASK ((uint32_t)0x00000003) |

Functions | |

| void | COMP_Cmd (uint32_t COMP_Selection, FunctionalState NewState) |

| Enable or disable the COMP peripheral. More... | |

| void | COMP_DeInit (uint32_t COMP_Selection) |

| Deinitializes COMP peripheral registers to their default reset values. More... | |

| uint32_t | COMP_GetOutputLevel (uint32_t COMP_Selection) |

| Return the output level (high or low) of the selected comparator. The output level depends on the selected polarity. If the polarity is not inverted: More... | |

| void | COMP_Init (uint32_t COMP_Selection, COMP_InitTypeDef *COMP_InitStruct) |

| Initializes the COMP peripheral according to the specified parameters in COMP_InitStruct. More... | |

| void | COMP_LockConfig (uint32_t COMP_Selection) |

| Lock the selected comparator (COMP1/COMP2) configuration. More... | |

| void | COMP_StructInit (COMP_InitTypeDef *COMP_InitStruct) |

| Fills each COMP_InitStruct member with its default value. More... | |

| void | COMP_SwitchCmd (uint32_t COMP_Selection, FunctionalState NewState) |

| Close or Open the SW1 switch. More... | |

| void | COMP_WindowCmd (uint32_t COMP_Selection, FunctionalState NewState) |

| Enables or disables the window mode. Window mode for comparators makes use of two comparators: COMP1 and COM2, COMP3 and COMP4, COMP5 and COMP6. In window mode, COMPx and COMPx-1 (where x can be 2, 4 or 6) non inverting inputs are connected together and only COMPx-1 non inverting input can be used. e.g When window mode enabled for COMP4, COMP3 non inverting input (PB14 or PD14) is to be used. More... | |

Detailed Description

This file provides firmware functions to manage the following functionalities of the 7 analog comparators (COMP1, COMP2...COMP7) peripheral:

- Version

- V1.1.1

- Date

- 04-April-2014

- Comparators configuration

- Window mode control

==============================================================================

##### COMP Peripheral features #####

==============================================================================

[..]

The device integrates 7 analog comparators COMP1, COMP2...COMP7:

(#) The non inverting input and inverting input can be set to GPIO pins

as shown in table1. COMP Inputs below.

(#) The COMP output is internally is available using COMP_GetOutputLevel()

and can be set on GPIO pins. Refer to table 2. COMP Outputs below.

(#) The COMP output can be redirected to embedded timers (TIM1, TIM2, TIM3...)

Refer to table 3. COMP Outputs redirection to embedded timers below.

(#) The comparators COMP1 and COMP2, COMP3 and COMP4, COMP5 and COMP6 can be combined in window

mode and only COMP1, COMP3 and COMP5 non inverting input can be used as non-inverting input.

(#) The seven comparators have interrupt capability with wake-up

from Sleep and Stop modes (through the EXTI controller):

(++) COMP1 is internally connected to EXTI Line 21

(++) COMP2 is internally connected to EXTI Line 22

(++) COMP3 is internally connected to EXTI Line 29

(++) COMP4 is internally connected to EXTI Line 30

(++) COMP5 is internally connected to EXTI Line 31

(++) COMP6 is internally connected to EXTI Line 32

(++) COMP7 is internally connected to EXTI Line 33

[..] Table 1. COMP Inputs

+------------------------------------------------------------------------------------------+

| | | COMP1 | COMP2 | COMP3 | COMP4 | COMP5 | COMP6 | COMP7 |

|-----------------|----------------|---------------|---------------------------------------|

| | 1/4 VREFINT | OK | OK | OK | OK | OK | OK | OK |

| | 1/2 VREFINT | OK | OK | OK | OK | OK | OK | OK |

| | 3/4 VREFINT | OK | OK | OK | OK | OK | OK | OK |

| Inverting Input | VREFINT | OK | OK | OK | OK | OK | OK | OK |

| | DAC1 OUT1(PA4) | OK | OK | OK | OK | OK | OK | OK |

| | DAC1 OUT2(PA5) | OK | OK | OK | OK | OK | OK | OK |

| | IO1 | PA0 | PA2 | PD15 | PE8 | PD13 | PD10 | PC0 |

| | IO2 | --- | --- | PB12 | PB2 | PB10 | PB15 | --- |

| | DAC2 OUT1(PA6) | --- | OK | --- | OK | --- | OK | --- |

|-----------------|----------------|-------|-------|-------|-------|-------|-------|-------|

| Non Inverting | IO1 | PA1 | PA7 | PB14 | PB0 | PD12 | PD11 | PA0 |

| Input | IO2 | --- | PA3 | PD14 | PE7 | PB13 | PB11 | PC1 |

+------------------------------------------------------------------------------------------+

[..] Table 2. COMP Outputs

+-------------------------------------------------------+

| COMP1 | COMP2 | COMP3 | COMP4 | COMP5 | COMP6 | COMP7 |

|-------|-------|-------|-------|-------|-------|-------|

| PA0 | PA2 | PB1 | PC8 | PC7 | PA10 | PC2 |

| PF4 | PA7 | --- | PA8 | PA9 | PC6 | --- |

| PA6 | PA12 | --- | --- | --- | --- | --- |

| PA11 | PB9 | --- | --- | --- | --- | --- |

| PB8 | --- | --- | --- | --- | --- | --- |

+-------------------------------------------------------+

[..] Table 3. COMP Outputs redirection to embedded timers

+----------------------------------------------------------------------------------------------------------------------+

| COMP1 | COMP2 | COMP3 | COMP4 | COMP5 | COMP6 | COMP7 |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| TIM1 BKIN | TIM1 BKIN | TIM1 BKIN | TIM1 BKIN | TIM1 BKIN | TIM1 BKIN | TIM1 BKIN |

| | | | | | | |

| TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 |

| | | | | | | |

| TIM8 BKIN | TIM8 BKIN | TIM8 BKIN | TIM8 BKIN | TIM8 BKIN | TIM8 BKIN | TIM8 BKIN |

| | | | | | | |

| TIM8 BKIN2 | TIM8 BKIN2 | TIM8 BKIN2 | TIM8 BKIN2 | TIM8 BKIN2 | TIM8 BKIN2 | TIM8 BKIN2 |

| | | | | | | |

| TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 | TIM1 BKIN2 |

| + | + | + | + | + | + | + |

| TIM8BKIN2 | TIM8BKIN2 | TIM8BKIN2 | TIM8BKIN2 | TIM8BKIN2 | TIM8BKIN2 | TIM8BKIN2 |

| | | | | | | |

| TIM1 OCREFCLR | TIM1 OCREFCLR | TIM1 OCREFCLR | TIM8 OCREFCLR | TIM8 OCREFCLR | TIM8 OCREFCLR | TIM1 OCREFCLR |

| | | | | | | |

| TIM1 IC1 | TIM1 IC1 | TIM2 OCREFCLR | TIM3 IC3 | TIM2 IC1 | TIM2 IC2 | TIM8 OCREFCLR |

| | | | | | | |

| TIM2 IC4 | TIM2 IC4 | TIM3 IC2 | TIM3 OCREFCLR | TIM3 OCREFCLR | TIM2 OCREFCLR | TIM2 IC3 |

| | | | | | | |

| TIM2 OCREFCLR | TIM2 OCREFCLR | TIM4 IC1 | TIM4 IC2 | TIM4 IC3 | TIM16 OCREFCLR| TIM1 IC2 |

| | | | | | | |

| TIM3 IC1 | TIM3 IC1 | TIM15 IC1 | TIM15 OCREFCLR| TIM16 BKIN | TIM16 IC1 | TIM17 OCREFCLR|

| | | | | | | |

| TIM3 OCREFCLR | TIM3 OCREFCLR | TIM15 BKIN | TIM15 IC2 | TIM17 IC1 | TIM4 IC4 | TIM17 BKIN |

+----------------------------------------------------------------------------------------------------------------------+

[..] Table 4. COMP Outputs blanking sources

+----------------------------------------------------------------------------------------------------------------------+

| COMP1 | COMP2 | COMP3 | COMP4 | COMP5 | COMP6 | COMP7 |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| TIM1 OC5 | TIM1 OC5 | TIM1 OC5 | TIM3 OC4 | TIM3 OC3 | TIM2 OC4 | TIM1 OC5 |

| | | | | | | |

| TIM2 OC3 | TIM2 OC3 | -------- | TIM8 OC5 | TIM8 OC5 | TIM8 OC5 | TIM8 OC5 |

| | | | | | | |

| TIM3 OC3 | TIM3 OC3 | TIM2 OC4 | TIM15 OC1 | TIM8 BKIN | TIM15 OC2 | TIM15 OC2 |

| | | | | | | |

+----------------------------------------------------------------------------------------------------------------------+

##### How to use this driver #####

==============================================================================

[..]

This driver provides functions to configure and program the Comparators

of all STM32F30x devices.

To use the comparator, perform the following steps:

(#) Enable the SYSCFG APB clock to get write access to comparator

register using RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE);

(#) Configure the comparator input in analog mode using GPIO_Init()

(#) Configure the comparator output in alternate function mode

using GPIO_Init() and use GPIO_PinAFConfig() function to map the

comparator output to the GPIO pin

(#) Configure the comparator using COMP_Init() function:

(++) Select the inverting input

(++) Select the non-inverting input

(++) Select the output polarity

(++) Select the output redirection

(++) Select the hysteresis level

(++) Select the power mode

(#) Enable the comparator using COMP_Cmd() function

(#) If required enable the COMP interrupt by configuring and enabling

EXTI line in Interrupt mode and selecting the desired sensitivity

level using EXTI_Init() function. After that enable the comparator

interrupt vector using NVIC_Init() function.- Attention

© COPYRIGHT 2014 STMicroelectronics

Licensed under MCD-ST Liberty SW License Agreement V2, (the "License"); You may not use this file except in compliance with the License. You may obtain a copy of the License at:

http://www.st.com/software_license_agreement_liberty_v2

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Definition in file stm32f30x_comp.c.