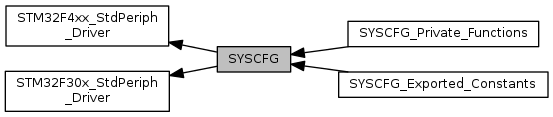

SYSCFG driver modules. More...

|

Modules | |

| SYSCFG_Exported_Constants | |

| SYSCFG_Private_Functions | |

Macros | |

| #define | BYPADDRPAR_BitNumber 0x04 |

| #define | CFGR1_BYPADDRPAR_BB (PERIPH_BB_BASE + (CFGR2_OFFSET * 32) + (BYPADDRPAR_BitNumber * 4)) |

| #define | CFGR1_CLEAR_MASK ((uint32_t)0x7C000000) |

| #define | CFGR1_OFFSET (SYSCFG_OFFSET + 0x00) |

| #define | CFGR1_USBITRMP_BB (PERIPH_BB_BASE + (CFGR1_OFFSET * 32) + (USBITRMP_BitNumber * 4)) |

| #define | CFGR2_OFFSET (SYSCFG_OFFSET + 0x18) |

| #define | CMP_PD_BitNumber ((uint8_t)0x00) |

| #define | CMPCR_CMP_PD_BB (PERIPH_BB_BASE + (CMPCR_OFFSET * 32) + (CMP_PD_BitNumber * 4)) |

| #define | CMPCR_OFFSET (SYSCFG_OFFSET + 0x20) |

| #define | MII_RMII_SEL_BitNumber ((uint8_t)0x17) |

| #define | PMC_MII_RMII_SEL_BB (PERIPH_BB_BASE + (PMC_OFFSET * 32) + (MII_RMII_SEL_BitNumber * 4)) |

| #define | PMC_OFFSET (SYSCFG_OFFSET + 0x04) |

| #define | SYSCFG_OFFSET (SYSCFG_BASE - PERIPH_BASE) |

| #define | SYSCFG_OFFSET (SYSCFG_BASE - PERIPH_BASE) |

| #define | USBITRMP_BitNumber 0x05 |

Functions | |

| void | SYSCFG_BreakConfig (uint32_t SYSCFG_Break) |

| Connects the selected parameter to the break input of TIM1. More... | |

| void | SYSCFG_BypassParityCheckDisable (void) |

| Disables the parity check on RAM. More... | |

| void | SYSCFG_ClearFlag (uint32_t SYSCFG_Flag) |

| Clears the selected SYSCFG flag. More... | |

| void | SYSCFG_CompensationCellCmd (FunctionalState NewState) |

| Enables or disables the I/O Compensation Cell. More... | |

| void | SYSCFG_DeInit (void) |

| Deinitializes the Alternate Functions (remap and EXTI configuration) registers to their default reset values. More... | |

| void | SYSCFG_DMAChannelRemapConfig (uint32_t SYSCFG_DMARemap, FunctionalState NewState) |

| Configures the DMA channels remapping. More... | |

| void | SYSCFG_EncoderRemapConfig (uint32_t SYSCFG_EncoderRemap) |

| Configures the remapping capabilities of encoder mode. @ note This feature implement the so-called M/T method for measuring speed and position using quadrature encoders. More... | |

| void | SYSCFG_ETH_MediaInterfaceConfig (uint32_t SYSCFG_ETH_MediaInterface) |

| Selects the ETHERNET media interface. More... | |

| void | SYSCFG_EXTILineConfig (uint8_t EXTI_PortSourceGPIOx, uint8_t EXTI_PinSourcex) |

| Selects the GPIO pin used as EXTI Line. More... | |

| FlagStatus | SYSCFG_GetCompensationCellStatus (void) |

| Checks whether the I/O Compensation Cell ready flag is set or not. More... | |

| FlagStatus | SYSCFG_GetFlagStatus (uint32_t SYSCFG_Flag) |

| Checks whether the specified SYSCFG flag is set or not. More... | |

| void | SYSCFG_I2CFastModePlusConfig (uint32_t SYSCFG_I2CFastModePlus, FunctionalState NewState) |

| Configures the I2C fast mode plus driving capability. More... | |

| void | SYSCFG_ITConfig (uint32_t SYSCFG_IT, FunctionalState NewState) |

| Enables or disables the selected SYSCFG interrupts. More... | |

| void | SYSCFG_MemoryRemapConfig (uint8_t SYSCFG_MemoryRemap) |

| Changes the mapping of the specified pin. More... | |

| void | SYSCFG_MemoryRemapConfig (uint32_t SYSCFG_MemoryRemap) |

| Configures the memory mapping at address 0x00000000. More... | |

| void | SYSCFG_SRAMWRPEnable (uint32_t SYSCFG_SRAMWRP) |

| Enables the ICODE SRAM write protection. More... | |

| void | SYSCFG_TriggerRemapConfig (uint32_t SYSCFG_TriggerRemap, FunctionalState NewState) |

| Configures the remapping capabilities of DAC/TIM triggers. More... | |

| void | SYSCFG_USBInterruptLineRemapCmd (FunctionalState NewState) |

| Remaps the USB interrupt lines. More... | |

Detailed Description

SYSCFG driver modules.

Macro Definition Documentation

| #define BYPADDRPAR_BitNumber 0x04 |

Definition at line 77 of file stm32f30x_syscfg.c.

| #define CFGR1_BYPADDRPAR_BB (PERIPH_BB_BASE + (CFGR2_OFFSET * 32) + (BYPADDRPAR_BitNumber * 4)) |

Definition at line 78 of file stm32f30x_syscfg.c.

| #define CFGR1_CLEAR_MASK ((uint32_t)0x7C000000) |

Definition at line 63 of file stm32f30x_syscfg.c.

| #define CFGR1_OFFSET (SYSCFG_OFFSET + 0x00) |

Definition at line 70 of file stm32f30x_syscfg.c.

| #define CFGR1_USBITRMP_BB (PERIPH_BB_BASE + (CFGR1_OFFSET * 32) + (USBITRMP_BitNumber * 4)) |

Definition at line 72 of file stm32f30x_syscfg.c.

| #define CFGR2_OFFSET (SYSCFG_OFFSET + 0x18) |

Definition at line 76 of file stm32f30x_syscfg.c.

| #define CMP_PD_BitNumber ((uint8_t)0x00) |

Definition at line 73 of file stm32f4xx_syscfg.c.

| #define CMPCR_CMP_PD_BB (PERIPH_BB_BASE + (CMPCR_OFFSET * 32) + (CMP_PD_BitNumber * 4)) |

Definition at line 74 of file stm32f4xx_syscfg.c.

| #define CMPCR_OFFSET (SYSCFG_OFFSET + 0x20) |

Definition at line 72 of file stm32f4xx_syscfg.c.

| #define MII_RMII_SEL_BitNumber ((uint8_t)0x17) |

Definition at line 67 of file stm32f4xx_syscfg.c.

| #define PMC_MII_RMII_SEL_BB (PERIPH_BB_BASE + (PMC_OFFSET * 32) + (MII_RMII_SEL_BitNumber * 4)) |

Definition at line 68 of file stm32f4xx_syscfg.c.

| #define PMC_OFFSET (SYSCFG_OFFSET + 0x04) |

Definition at line 66 of file stm32f4xx_syscfg.c.

| #define SYSCFG_OFFSET (SYSCFG_BASE - PERIPH_BASE) |

Definition at line 62 of file stm32f4xx_syscfg.c.

| #define SYSCFG_OFFSET (SYSCFG_BASE - PERIPH_BASE) |

Definition at line 66 of file stm32f30x_syscfg.c.

| #define USBITRMP_BitNumber 0x05 |

Definition at line 71 of file stm32f30x_syscfg.c.

Function Documentation

| void SYSCFG_BreakConfig | ( | uint32_t | SYSCFG_Break | ) |

Connects the selected parameter to the break input of TIM1.

- Note

- The selected configuration is locked and can be unlocked by system reset

- Parameters

-

SYSCFG_Break selects the configuration to be connected to break input of TIM1 This parameter can be any combination of the following values: - SYSCFG_Break_PVD: PVD interrupt is connected to the break input of TIM1.

- SYSCFG_Break_SRAMParity: SRAM Parity error is connected to the break input of TIM1.

- SYSCFG_Break_HardFault: Lockup output of CortexM4 is connected to the break input of TIM1.

- Return values

-

None

Definition at line 426 of file stm32f30x_syscfg.c.

| void SYSCFG_BypassParityCheckDisable | ( | void | ) |

Disables the parity check on RAM.

- Note

- Disabling the parity check on RAM locks the configuration bit. To re-enable the parity check on RAM perform a system reset.

- Parameters

-

None

- Return values

-

None

Definition at line 441 of file stm32f30x_syscfg.c.

| void SYSCFG_ClearFlag | ( | uint32_t | SYSCFG_Flag | ) |

Clears the selected SYSCFG flag.

- Parameters

-

SYSCFG_Flag selects the flag to be cleared. This parameter can be any combination of the following values: - SYSCFG_FLAG_PE: SRAM parity error flag.

- Return values

-

None

Definition at line 506 of file stm32f30x_syscfg.c.

| void SYSCFG_CompensationCellCmd | ( | FunctionalState | NewState | ) |

Enables or disables the I/O Compensation Cell.

- Note

- The I/O compensation cell can be used only when the device supply voltage ranges from 2.4 to 3.6 V.

- Parameters

-

NewState new state of the I/O Compensation Cell. This parameter can be one of the following values: - ENABLE: I/O compensation cell enabled

- DISABLE: I/O compensation cell power-down mode

- Return values

-

None

Definition at line 166 of file stm32f4xx_syscfg.c.

| void SYSCFG_DeInit | ( | void | ) |

Deinitializes the Alternate Functions (remap and EXTI configuration) registers to their default reset values.

- Parameters

-

None

- Return values

-

None Deinitializes the Alternate Functions (remap and EXTI configuration) registers to their default reset values.

- Parameters

-

None

- Return values

-

None

- Note

- MEM_MODE bits are not affected by APB reset. MEM_MODE bits took the value from the user option bytes.

Definition at line 91 of file stm32f4xx_syscfg.c.

| void SYSCFG_DMAChannelRemapConfig | ( | uint32_t | SYSCFG_DMARemap, |

| FunctionalState | NewState | ||

| ) |

Configures the DMA channels remapping.

- Parameters

-

SYSCFG_DMARemap selects the DMA channels remap. This parameter can be one of the following values: - SYSCFG_DMARemap_TIM17: Remap TIM17 DMA requests from DMA1 channel1 to channel2

- SYSCFG_DMARemap_TIM16: Remap TIM16 DMA requests from DMA1 channel3 to channel4

- SYSCFG_DMARemap_TIM6DAC1Ch1: Remap TIM6/DAC1 DMA requests from DMA2 channel 3 to DMA1 channel 3

- SYSCFG_DMARemap_TIM7DAC1Ch2: Remap TIM7/DAC2 DMA requests from DMA2 channel 4 to DMA1 channel 4

- SYSCFG_DMARemap_ADC2ADC4: Remap ADC2 and ADC4 DMA requests from DMA2 channel1/channel3 to channel3/channel4

- SYSCFG_DMARemap_DAC2Ch1: Remap DAC2 DMA requests to DMA1 channel5

- SYSCFG_DMARemapCh2_SPI1_RX: Remap SPI1 RX DMA1 CH2 requests

- SYSCFG_DMARemapCh4_SPI1_RX: Remap SPI1 RX DMA CH4 requests

- SYSCFG_DMARemapCh6_SPI1_RX: Remap SPI1 RX DMA CH6 requests

- SYSCFG_DMARemapCh3_SPI1_TX: Remap SPI1 TX DMA CH2 requests

- SYSCFG_DMARemapCh5_SPI1_TX: Remap SPI1 TX DMA CH5 requests

- SYSCFG_DMARemapCh7_SPI1_TX: Remap SPI1 TX DMA CH7 requests

- SYSCFG_DMARemapCh7_I2C1_RX: Remap I2C1 RX DMA CH7 requests

- SYSCFG_DMARemapCh3_I2C1_RX: Remap I2C1 RX DMA CH3 requests

- SYSCFG_DMARemapCh5_I2C1_RX: Remap I2C1 RX DMA CH5 requests

- SYSCFG_DMARemapCh6_I2C1_TX: Remap I2C1 TX DMA CH6 requests

- SYSCFG_DMARemapCh2_I2C1_TX: Remap I2C1 TX DMA CH2 requests

- SYSCFG_DMARemapCh4_I2C1_TX: Remap I2C1 TX DMA CH4 requests

- SYSCFG_DMARemapCh4_ADC2: Remap ADC2 DMA1 Ch4 requests

- SYSCFG_DMARemapCh2_ADC2: Remap ADC2 DMA1 Ch2 requests

NewState new state of the DMA channel remapping. This parameter can be: Enable or Disable.

- Note

- When enabled, DMA channel of the selected peripheral is remapped

- When disabled, Default DMA channel is mapped to the selected peripheral

- By default TIM17 DMA requests is mapped to channel 1 use SYSCFG_DMAChannelRemapConfig(SYSCFG_DMARemap_TIM17, Enable) to remap TIM17 DMA requests to DMA1 channel 2 use SYSCFG_DMAChannelRemapConfig(SYSCFG_DMARemap_TIM17, Disable) to map TIM17 DMA requests to DMA1 channel 1 (default mapping)

- Return values

-

None

Definition at line 192 of file stm32f30x_syscfg.c.

| void SYSCFG_EncoderRemapConfig | ( | uint32_t | SYSCFG_EncoderRemap | ) |

Configures the remapping capabilities of encoder mode. @ note This feature implement the so-called M/T method for measuring speed and position using quadrature encoders.

- Parameters

-

SYSCFG_EncoderRemap selects the remap option for encoder mode. This parameter can be one of the following values: - SYSCFG_EncoderRemap_No: No remap

- SYSCFG_EncoderRemap_TIM2: Timer 2 IC1 and IC2 connected to TIM15 IC1 and IC2

- SYSCFG_EncoderRemap_TIM3: Timer 3 IC1 and IC2 connected to TIM15 IC1 and IC2

- SYSCFG_EncoderRemap_TIM4: Timer 4 IC1 and IC2 connected to TIM15 IC1 and IC2

- Return values

-

None

Definition at line 286 of file stm32f30x_syscfg.c.

| void SYSCFG_ETH_MediaInterfaceConfig | ( | uint32_t | SYSCFG_ETH_MediaInterface | ) |

Selects the ETHERNET media interface.

- Parameters

-

SYSCFG_ETH_MediaInterface specifies the Media Interface mode. This parameter can be one of the following values: - SYSCFG_ETH_MediaInterface_MII: MII mode selected

- SYSCFG_ETH_MediaInterface_RMII: RMII mode selected

- Return values

-

None

Definition at line 149 of file stm32f4xx_syscfg.c.

| void SYSCFG_EXTILineConfig | ( | uint8_t | EXTI_PortSourceGPIOx, |

| uint8_t | EXTI_PinSourcex | ||

| ) |

Selects the GPIO pin used as EXTI Line.

- Parameters

-

EXTI_PortSourceGPIOx : selects the GPIO port to be used as source for EXTI lines where x can be (A..I) for STM32F40xx/STM32F41xx and STM32F427x/STM32F437x devices. EXTI_PinSourcex specifies the EXTI line to be configured. This parameter can be EXTI_PinSourcex where x can be (0..15, except for EXTI_PortSourceGPIOI x can be (0..11) for STM32F40xx/STM32F41xx and STM32F427x/STM32F437x devices.

- Return values

-

None

- Parameters

-

EXTI_PortSourceGPIOx : selects the GPIO port to be used as source for EXTI lines where x can be (A, B, C, D, E or F). EXTI_PinSourcex specifies the EXTI line to be configured. This parameter can be EXTI_PinSourcex where x can be (0..15)

- Return values

-

None

Definition at line 128 of file stm32f4xx_syscfg.c.

| FlagStatus SYSCFG_GetCompensationCellStatus | ( | void | ) |

Checks whether the I/O Compensation Cell ready flag is set or not.

- Parameters

-

None

- Return values

-

The new state of the I/O Compensation Cell ready flag (SET or RESET)

Definition at line 179 of file stm32f4xx_syscfg.c.

| FlagStatus SYSCFG_GetFlagStatus | ( | uint32_t | SYSCFG_Flag | ) |

Checks whether the specified SYSCFG flag is set or not.

- Parameters

-

SYSCFG_Flag specifies the SYSCFG flag to check. This parameter can be one of the following values: - SYSCFG_FLAG_PE: SRAM parity error flag.

- Return values

-

The new state of SYSCFG_Flag (SET or RESET).

Definition at line 474 of file stm32f30x_syscfg.c.

| void SYSCFG_I2CFastModePlusConfig | ( | uint32_t | SYSCFG_I2CFastModePlus, |

| FunctionalState | NewState | ||

| ) |

Configures the I2C fast mode plus driving capability.

- Parameters

-

SYSCFG_I2CFastModePlus selects the pin. This parameter can be one of the following values: - SYSCFG_I2CFastModePlus_PB6: Configure fast mode plus driving capability for PB6

- SYSCFG_I2CFastModePlus_PB7: Configure fast mode plus driving capability for PB7

- SYSCFG_I2CFastModePlus_PB8: Configure fast mode plus driving capability for PB8

- SYSCFG_I2CFastModePlus_PB9: Configure fast mode plus driving capability for PB9

- SYSCFG_I2CFastModePlus_I2C1: Configure fast mode plus driving capability for I2C1 pins

- SYSCFG_I2CFastModePlus_I2C2: Configure fast mode plus driving capability for I2C2 pins

NewState new state of the DMA channel remapping. This parameter can be:

- Note

- For I2C1, fast mode plus driving capability can be enabled on all selected I2C1 pins using SYSCFG_I2CFastModePlus_I2C1 parameter or independently on each one of the following pins PB6, PB7, PB8 and PB9.

- For remaing I2C1 pins (PA14, PA15...) fast mode plus driving capability can be enabled only by using SYSCFG_I2CFastModePlus_I2C1 parameter.

- For all I2C2 pins fast mode plus driving capability can be enabled only by using SYSCFG_I2CFastModePlus_I2C2 parameter.

- Return values

-

None

Definition at line 344 of file stm32f30x_syscfg.c.

| void SYSCFG_ITConfig | ( | uint32_t | SYSCFG_IT, |

| FunctionalState | NewState | ||

| ) |

Enables or disables the selected SYSCFG interrupts.

- Parameters

-

SYSCFG_IT specifies the SYSCFG interrupt sources to be enabled or disabled. This parameter can be one of the following values: - SYSCFG_IT_IXC: Inexact Interrupt

- SYSCFG_IT_IDC: Input denormal Interrupt

- SYSCFG_IT_OFC: Overflow Interrupt

- SYSCFG_IT_UFC: Underflow Interrupt

- SYSCFG_IT_DZC: Divide-by-zero Interrupt

- SYSCFG_IT_IOC: Invalid operation Interrupt

NewState new state of the specified SYSCFG interrupts. This parameter can be: ENABLE or DISABLE.

- Return values

-

None

Definition at line 376 of file stm32f30x_syscfg.c.

| void SYSCFG_MemoryRemapConfig | ( | uint8_t | SYSCFG_MemoryRemap | ) |

Changes the mapping of the specified pin.

- Parameters

-

SYSCFG_Memory selects the memory remapping. This parameter can be one of the following values: - SYSCFG_MemoryRemap_Flash: Main Flash memory mapped at 0x00000000

- SYSCFG_MemoryRemap_SystemFlash: System Flash memory mapped at 0x00000000

- SYSCFG_MemoryRemap_FSMC: FSMC (Bank1 (NOR/PSRAM 1 and 2) mapped at 0x00000000

- SYSCFG_MemoryRemap_SRAM: Embedded SRAM (112kB) mapped at 0x00000000

- Return values

-

None

Definition at line 107 of file stm32f4xx_syscfg.c.

| void SYSCFG_MemoryRemapConfig | ( | uint32_t | SYSCFG_MemoryRemap | ) |

Configures the memory mapping at address 0x00000000.

- Parameters

-

SYSCFG_MemoryRemap selects the memory remapping. This parameter can be one of the following values: - SYSCFG_MemoryRemap_Flash: Main Flash memory mapped at 0x00000000

- SYSCFG_MemoryRemap_SystemMemory: System Flash memory mapped at 0x00000000

- SYSCFG_MemoryRemap_SRAM: Embedded SRAM mapped at 0x00000000

- Return values

-

None

Definition at line 136 of file stm32f30x_syscfg.c.

| void SYSCFG_SRAMWRPEnable | ( | uint32_t | SYSCFG_SRAMWRP | ) |

Enables the ICODE SRAM write protection.

- Note

- Enabling the ICODE SRAM write protection locks the configuration bit. To disable the ICODE SRAM write protection perform a system reset.

- Parameters

-

None

- Return values

-

None

Definition at line 454 of file stm32f30x_syscfg.c.

| void SYSCFG_TriggerRemapConfig | ( | uint32_t | SYSCFG_TriggerRemap, |

| FunctionalState | NewState | ||

| ) |

Configures the remapping capabilities of DAC/TIM triggers.

- Parameters

-

SYSCFG_TriggerRemap selects the trigger to be remapped. This parameter can be one of the following values: - SYSCFG_TriggerRemap_DACTIM3: Remap DAC trigger from TIM8 to TIM3

- SYSCFG_TriggerRemap_TIM1TIM17: Remap TIM1 ITR3 from TIM4 TRGO to TIM17 OC

- SYSCFG_TriggerRemap_DACHRTIM1_TRIG1: Remap DAC trigger to HRTIM1 TRIG1

- SYSCFG_TriggerRemap_DACHRTIM1_TRIG2: Remap DAC trigger to HRTIM1 TRIG2

NewState new state of the trigger mapping. This parameter can be: ENABLE or DISABLE.

- Note

- ENABLE: Enable fast mode plus driving capability for selected pin

- DISABLE: Disable fast mode plus driving capability for selected pin

- Return values

-

None

Definition at line 240 of file stm32f30x_syscfg.c.

| void SYSCFG_USBInterruptLineRemapCmd | ( | FunctionalState | NewState | ) |

Remaps the USB interrupt lines.

- Parameters

-

NewState new state of the mapping of USB interrupt lines. This parameter can be: ENABLE Remap the USB interrupt line as following: - USB Device High Priority (USB_HP) interrupt mapped to line 74.

- USB Device Low Priority (USB_LP) interrupt mapped to line 75.

- USB Wakeup Interrupt (USB_WKUP) interrupt mapped to line 76.

DISABLE Use the default USB interrupt line: - USB Device High Priority (USB_HP) interrupt mapped to line 19.

- USB Device Low Priority (USB_LP) interrupt mapped to line 20.

- USB Wakeup Interrupt (USB_WKUP) interrupt mapped to line 42.

- Return values

-

None

Definition at line 312 of file stm32f30x_syscfg.c.