|

| #define | __HAL_RAMECC_CLEAR_FLAG(__HANDLE__, __FLAG__) ((__HANDLE__)->Instance->SR &= ~(__FLAG__)) |

| | Clear the RAMECC pending flags. More...

|

| |

| #define | __HAL_RAMECC_DISABLE_GLOBAL_IT(__HANDLE__, __INTERRUPT__) ((((RAMECC_TypeDef *)((uint32_t)(__HANDLE__)->Instance & 0xFFFFFF00U))->IER) &= ~((__INTERRUPT__) & ~RAMECC_IT_GLOBAL_ID)) |

| |

| #define | __HAL_RAMECC_DISABLE_IT(__HANDLE__, __INTERRUPT__) |

| | Disable the specified RAMECC interrupts. More...

|

| |

| #define | __HAL_RAMECC_DISABLE_MONITOR_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->CR &= ~((__INTERRUPT__) & ~RAMECC_IT_MONITOR_ID)) |

| |

| #define | __HAL_RAMECC_ENABLE_GLOBAL_IT(__HANDLE__, __INTERRUPT__) ((((RAMECC_TypeDef *)((uint32_t)(__HANDLE__)->Instance & 0xFFFFFF00U))->IER) |= ((__INTERRUPT__) & ~RAMECC_IT_GLOBAL_ID)) |

| |

| #define | __HAL_RAMECC_ENABLE_IT(__HANDLE__, __INTERRUPT__) |

| | Enable the specified RAMECC interrupts. More...

|

| |

| #define | __HAL_RAMECC_ENABLE_MONITOR_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->CR |= ((__INTERRUPT__) & ~RAMECC_IT_MONITOR_ID)) |

| |

| #define | __HAL_RAMECC_GET_FLAG(__HANDLE__, __FLAG__) ((__HANDLE__)->Instance->SR &= (__FLAG__)) |

| | Get the RAMECC pending flags. More...

|

| |

| #define | __HAL_RAMECC_GET_GLOBAL_IT_SOURCE(__HANDLE__, __INTERRUPT__) (((((RAMECC_TypeDef *)((uint32_t)(__HANDLE__)->Instance & 0xFFFFFF00U))->IER) & ((__INTERRUPT__) & ~RAMECC_IT_GLOBAL_ID)) ? SET : RESET) |

| |

| #define | __HAL_RAMECC_GET_IT_SOURCE(__HANDLE__, __INTERRUPT__) |

| | Check whether the specified RAMECC interrupt source is enabled or not. More...

|

| |

| #define | __HAL_RAMECC_GET_MONITOR_IT_SOURCE(__HANDLE__, __INTERRUPT__) ((((__HANDLE__)->Instance->CR) & ((__INTERRUPT__) & ~RAMECC_IT_GLOBAL_ID)) ? SET : RESET) |

| |

| #define | __HAL_RAMECC_RESET_HANDLE_STATE(__HANDLE__) ((__HANDLE__)->State = HAL_RAMECC_STATE_RESET) |

| | Reset the RAMECC handle state. More...

|

| |

| #define | HAL_RAMECC_ERROR_BUSY 0x00000002U |

| |

| #define | HAL_RAMECC_ERROR_INVALID_CALLBACK 0x00000003U |

| |

| #define | HAL_RAMECC_ERROR_NONE 0x00000000U |

| |

| #define | HAL_RAMECC_ERROR_TIMEOUT 0x00000001U |

| |

| #define | IS_RAMECC_GLOBAL_INTERRUPT(INTERRUPT) |

| |

| #define | IS_RAMECC_INTERRUPT(INTERRUPT) |

| |

| #define | IS_RAMECC_MONITOR_INTERRUPT(INTERRUPT) |

| |

| #define | RAMECC_FLAG_DOUBLEERR_R RAMECC_SR_DEDF |

| |

| #define | RAMECC_FLAG_DOUBLEERR_W RAMECC_SR_DEBWDF |

| |

| #define | RAMECC_FLAG_SINGLEERR_R RAMECC_SR_SEDCF |

| |

| #define | RAMECC_FLAGS_ALL (RAMECC_SR_SEDCF | RAMECC_SR_DEDF | RAMECC_SR_DEBWDF) |

| |

| #define | RAMECC_IT_GLOBAL_ALL (RAMECC_IT_GLOBAL_ID | RAMECC_IER_GIE | RAMECC_IER_GECCSEIE | RAMECC_IER_GECCDEIE | RAMECC_IER_GECCDEBWIE) |

| |

| #define | RAMECC_IT_GLOBAL_DOUBLEERR_R (RAMECC_IT_GLOBAL_ID | RAMECC_IER_GECCDEIE) |

| |

| #define | RAMECC_IT_GLOBAL_DOUBLEERR_W (RAMECC_IT_GLOBAL_ID | RAMECC_IER_GECCDEBWIE) |

| |

| #define | RAMECC_IT_GLOBAL_ENABLE (RAMECC_IT_GLOBAL_ID | RAMECC_IER_GIE) |

| |

| #define | RAMECC_IT_GLOBAL_ID 0x10000000UL |

| |

| #define | RAMECC_IT_GLOBAL_SINGLEERR_R (RAMECC_IT_GLOBAL_ID | RAMECC_IER_GECCSEIE) |

| |

| #define | RAMECC_IT_MONITOR_ALL (RAMECC_IT_MONITOR_ID | RAMECC_CR_ECCDEBWIE | RAMECC_CR_ECCDEIE | RAMECC_CR_ECCSEIE) |

| |

| #define | RAMECC_IT_MONITOR_DOUBLEERR_R (RAMECC_IT_MONITOR_ID | RAMECC_CR_ECCDEIE) |

| |

| #define | RAMECC_IT_MONITOR_DOUBLEERR_W (RAMECC_IT_MONITOR_ID | RAMECC_CR_ECCDEBWIE) |

| |

| #define | RAMECC_IT_MONITOR_ID 0x20000000UL |

| |

| #define | RAMECC_IT_MONITOR_SINGLEERR_R (RAMECC_IT_MONITOR_ID | RAMECC_CR_ECCSEIE) |

| |

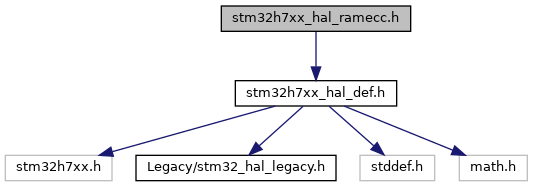

Header file of RAMECC HAL module.

- Author

- MCD Application Team

- Attention

© COPYRIGHT(c) 2017 STMicroelectronics. All rights reserved.

This software component is licensed by ST under BSD 3-Clause license, the "License"; You may not use this file except in compliance with the License. You may obtain a copy of the License at: opensource.org/licenses/BSD-3-Clause

Definition in file stm32h7xx_hal_ramecc.h.