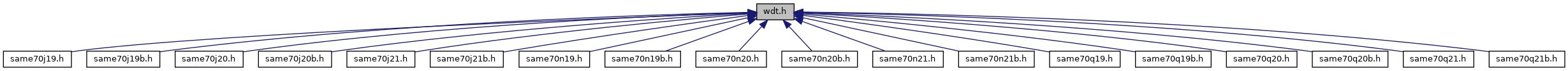

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Wdt |

| Wdt hardware registers. More... | |

Macros | |

| #define | WDT_CR_KEY(value) ((WDT_CR_KEY_Msk & ((value) << WDT_CR_KEY_Pos))) |

| #define | WDT_CR_KEY_Msk (0xffu << WDT_CR_KEY_Pos) |

| (WDT_CR) Password More... | |

| #define | WDT_CR_KEY_PASSWD (0xA5u << 24) |

| (WDT_CR) Writing any other value in this field aborts the write operation. More... | |

| #define | WDT_CR_KEY_Pos 24 |

| #define | WDT_CR_WDRSTT (0x1u << 0) |

| (WDT_CR) Watchdog Restart More... | |

| #define | WDT_MR_WDD(value) ((WDT_MR_WDD_Msk & ((value) << WDT_MR_WDD_Pos))) |

| #define | WDT_MR_WDD_Msk (0xfffu << WDT_MR_WDD_Pos) |

| (WDT_MR) Watchdog Delta Value More... | |

| #define | WDT_MR_WDD_Pos 16 |

| #define | WDT_MR_WDDBGHLT (0x1u << 28) |

| (WDT_MR) Watchdog Debug Halt More... | |

| #define | WDT_MR_WDDIS (0x1u << 15) |

| (WDT_MR) Watchdog Disable More... | |

| #define | WDT_MR_WDFIEN (0x1u << 12) |

| (WDT_MR) Watchdog Fault Interrupt Enable More... | |

| #define | WDT_MR_WDIDLEHLT (0x1u << 29) |

| (WDT_MR) Watchdog Idle Halt More... | |

| #define | WDT_MR_WDRSTEN (0x1u << 13) |

| (WDT_MR) Watchdog Reset Enable More... | |

| #define | WDT_MR_WDV(value) ((WDT_MR_WDV_Msk & ((value) << WDT_MR_WDV_Pos))) |

| #define | WDT_MR_WDV_Msk (0xfffu << WDT_MR_WDV_Pos) |

| (WDT_MR) Watchdog Counter Value More... | |

| #define | WDT_MR_WDV_Pos 0 |

| #define | WDT_SR_WDERR (0x1u << 1) |

| (WDT_SR) Watchdog Error (cleared on read) More... | |

| #define | WDT_SR_WDUNF (0x1u << 0) |

| (WDT_SR) Watchdog Underflow (cleared on read) More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/wdt.h.