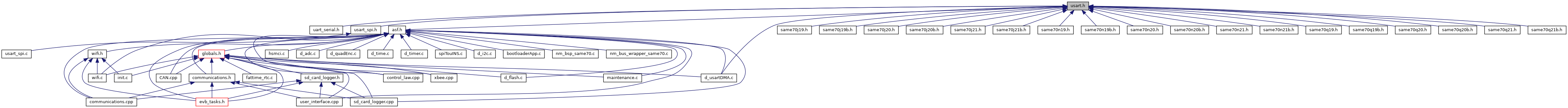

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Usart |

| Usart hardware registers. More... | |

Macros | |

| #define | US_BRGR_CD(value) ((US_BRGR_CD_Msk & ((value) << US_BRGR_CD_Pos))) |

| #define | US_BRGR_CD_Msk (0xffffu << US_BRGR_CD_Pos) |

| (US_BRGR) Clock Divider More... | |

| #define | US_BRGR_CD_Pos 0 |

| #define | US_BRGR_FP(value) ((US_BRGR_FP_Msk & ((value) << US_BRGR_FP_Pos))) |

| #define | US_BRGR_FP_Msk (0x7u << US_BRGR_FP_Pos) |

| (US_BRGR) Fractional Part More... | |

| #define | US_BRGR_FP_Pos 16 |

| #define | US_CR_DTRDIS (0x1u << 17) |

| (US_CR) Data Terminal Ready Disable More... | |

| #define | US_CR_DTREN (0x1u << 16) |

| (US_CR) Data Terminal Ready Enable More... | |

| #define | US_CR_FCS (0x1u << 18) |

| (US_CR) Force SPI Chip Select More... | |

| #define | US_CR_LINABT (0x1u << 20) |

| (US_CR) Abort LIN Transmission More... | |

| #define | US_CR_LINWKUP (0x1u << 21) |

| (US_CR) Send LIN Wakeup Signal More... | |

| #define | US_CR_RCS (0x1u << 19) |

| (US_CR) Release SPI Chip Select More... | |

| #define | US_CR_RETTO (0x1u << 15) |

| (US_CR) Start Time-out Immediately More... | |

| #define | US_CR_RSTIT (0x1u << 13) |

| (US_CR) Reset Iterations More... | |

| #define | US_CR_RSTNACK (0x1u << 14) |

| (US_CR) Reset Non Acknowledge More... | |

| #define | US_CR_RSTRX (0x1u << 2) |

| (US_CR) Reset Receiver More... | |

| #define | US_CR_RSTSTA (0x1u << 8) |

| (US_CR) Reset Status Bits More... | |

| #define | US_CR_RSTTX (0x1u << 3) |

| (US_CR) Reset Transmitter More... | |

| #define | US_CR_RTSDIS (0x1u << 19) |

| (US_CR) Request to Send Pin Control More... | |

| #define | US_CR_RTSEN (0x1u << 18) |

| (US_CR) Request to Send Pin Control More... | |

| #define | US_CR_RXDIS (0x1u << 5) |

| (US_CR) Receiver Disable More... | |

| #define | US_CR_RXEN (0x1u << 4) |

| (US_CR) Receiver Enable More... | |

| #define | US_CR_SENDA (0x1u << 12) |

| (US_CR) Send Address More... | |

| #define | US_CR_STPBRK (0x1u << 10) |

| (US_CR) Stop Break More... | |

| #define | US_CR_STTBRK (0x1u << 9) |

| (US_CR) Start Break More... | |

| #define | US_CR_STTTO (0x1u << 11) |

| (US_CR) Clear TIMEOUT Flag and Start Time-out After Next Character Received More... | |

| #define | US_CR_TXDIS (0x1u << 7) |

| (US_CR) Transmitter Disable More... | |

| #define | US_CR_TXEN (0x1u << 6) |

| (US_CR) Transmitter Enable More... | |

| #define | US_CSR_CTS (0x1u << 23) |

| (US_CSR) Image of CTS Input More... | |

| #define | US_CSR_CTSIC (0x1u << 19) |

| (US_CSR) Clear to Send Input Change Flag (cleared on read) More... | |

| #define | US_CSR_DCD (0x1u << 22) |

| (US_CSR) Image of DCD Input More... | |

| #define | US_CSR_DCDIC (0x1u << 18) |

| (US_CSR) Data Carrier Detect Input Change Flag (cleared on read) More... | |

| #define | US_CSR_DSR (0x1u << 21) |

| (US_CSR) Image of DSR Input More... | |

| #define | US_CSR_DSRIC (0x1u << 17) |

| (US_CSR) Data Set Ready Input Change Flag (cleared on read) More... | |

| #define | US_CSR_FRAME (0x1u << 6) |

| (US_CSR) Framing Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_ITER (0x1u << 10) |

| (US_CSR) Max Number of Repetitions Reached (cleared by writing a one to bit US_CR.RSTIT) More... | |

| #define | US_CSR_LBLOVFE (0x1u << 28) |

| (US_CSR) LON Backlog Overflow Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LCOL (0x1u << 25) |

| (US_CSR) LON Collision Detected Flag (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LCRCE (0x1u << 7) |

| (US_CSR) LON CRC Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LFET (0x1u << 26) |

| (US_CSR) LON Frame Early Termination (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINBE (0x1u << 25) |

| (US_CSR) LIN Bit Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINBK (0x1u << 13) |

| (US_CSR) LIN Break Sent or LIN Break Received (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINBLS (0x1u << 23) |

| (US_CSR) LIN Bus Line Status More... | |

| #define | US_CSR_LINCE (0x1u << 28) |

| (US_CSR) LIN Checksum Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINHTE (0x1u << 31) |

| (US_CSR) LIN Header Timeout Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINID (0x1u << 14) |

| (US_CSR) LIN Identifier Sent or LIN Identifier Received (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINIPE (0x1u << 27) |

| (US_CSR) LIN Identifier Parity Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINISFE (0x1u << 26) |

| (US_CSR) LIN Inconsistent Synch Field Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINSNRE (0x1u << 29) |

| (US_CSR) LIN Slave Not Responding Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINSTE (0x1u << 30) |

| (US_CSR) LIN Synch Tolerance Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LINTC (0x1u << 15) |

| (US_CSR) LIN Transfer Completed (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LRXD (0x1u << 27) |

| (US_CSR) LON Reception End Flag (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LSFE (0x1u << 6) |

| (US_CSR) LON Short Frame Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_LTXD (0x1u << 24) |

| (US_CSR) LON Transmission End Flag (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_MANERR (0x1u << 24) |

| (US_CSR) Manchester Error (cleared by writing a one to the bit US_CR.RSTSTA) More... | |

| #define | US_CSR_NACK (0x1u << 13) |

| (US_CSR) Non Acknowledge Interrupt (cleared by writing a one to bit US_CR.RSTNACK) More... | |

| #define | US_CSR_NSS (0x1u << 23) |

| (US_CSR) NSS Line (Driving CTS Pin) Rising or Falling Edge Event (cleared on read) More... | |

| #define | US_CSR_NSSE (0x1u << 19) |

| (US_CSR) NSS Line (Driving CTS Pin) Rising or Falling Edge Event (cleared on read) More... | |

| #define | US_CSR_OVRE (0x1u << 5) |

| (US_CSR) Overrun Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_PARE (0x1u << 7) |

| (US_CSR) Parity Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_RI (0x1u << 20) |

| (US_CSR) Image of RI Input More... | |

| #define | US_CSR_RIIC (0x1u << 16) |

| (US_CSR) Ring Indicator Input Change Flag (cleared on read) More... | |

| #define | US_CSR_RXBRK (0x1u << 2) |

| (US_CSR) Break Received/End of Break (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_CSR_RXRDY (0x1u << 0) |

| (US_CSR) Receiver Ready (cleared by reading US_RHR) More... | |

| #define | US_CSR_TIMEOUT (0x1u << 8) |

| (US_CSR) Receiver Time-out (cleared by writing a one to bit US_CR.STTTO) More... | |

| #define | US_CSR_TXEMPTY (0x1u << 9) |

| (US_CSR) Transmitter Empty (cleared by writing US_THR) More... | |

| #define | US_CSR_TXRDY (0x1u << 1) |

| (US_CSR) Transmitter Ready (cleared by writing US_THR) More... | |

| #define | US_CSR_UNRE (0x1u << 10) |

| (US_CSR) Underrun Error (cleared by writing a one to bit US_CR.RSTSTA) More... | |

| #define | US_FIDI_BETA2(value) ((US_FIDI_BETA2_Msk & ((value) << US_FIDI_BETA2_Pos))) |

| #define | US_FIDI_BETA2_Msk (0xffffffu << US_FIDI_BETA2_Pos) |

| (US_FIDI) LON BETA2 Length More... | |

| #define | US_FIDI_BETA2_Pos 0 |

| #define | US_FIDI_FI_DI_RATIO(value) ((US_FIDI_FI_DI_RATIO_Msk & ((value) << US_FIDI_FI_DI_RATIO_Pos))) |

| #define | US_FIDI_FI_DI_RATIO_Msk (0xffffu << US_FIDI_FI_DI_RATIO_Pos) |

| (US_FIDI) FI Over DI Ratio Value More... | |

| #define | US_FIDI_FI_DI_RATIO_Pos 0 |

| #define | US_ICDIFF_ICDIFF(value) ((US_ICDIFF_ICDIFF_Msk & ((value) << US_ICDIFF_ICDIFF_Pos))) |

| #define | US_ICDIFF_ICDIFF_Msk (0xfu << US_ICDIFF_ICDIFF_Pos) |

| (US_ICDIFF) IC Differentiator Number More... | |

| #define | US_ICDIFF_ICDIFF_Pos 0 |

| #define | US_IDR_CTSIC (0x1u << 19) |

| (US_IDR) Clear to Send Input Change Interrupt Disable More... | |

| #define | US_IDR_DCDIC (0x1u << 18) |

| (US_IDR) Data Carrier Detect Input Change Interrupt Disable More... | |

| #define | US_IDR_DSRIC (0x1u << 17) |

| (US_IDR) Data Set Ready Input Change Disable More... | |

| #define | US_IDR_FRAME (0x1u << 6) |

| (US_IDR) Framing Error Interrupt Disable More... | |

| #define | US_IDR_ITER (0x1u << 10) |

| (US_IDR) Max Number of Repetitions Reached Interrupt Disable More... | |

| #define | US_IDR_LBLOVFE (0x1u << 28) |

| (US_IDR) LON Backlog Overflow Error Interrupt Disable More... | |

| #define | US_IDR_LCOL (0x1u << 25) |

| (US_IDR) LON Collision Interrupt Disable More... | |

| #define | US_IDR_LCRCE (0x1u << 7) |

| (US_IDR) LON CRC Error Interrupt Disable More... | |

| #define | US_IDR_LFET (0x1u << 26) |

| (US_IDR) LON Frame Early Termination Interrupt Disable More... | |

| #define | US_IDR_LINBE (0x1u << 25) |

| (US_IDR) LIN Bus Error Interrupt Disable More... | |

| #define | US_IDR_LINBK (0x1u << 13) |

| (US_IDR) LIN Break Sent or LIN Break Received Interrupt Disable More... | |

| #define | US_IDR_LINCE (0x1u << 28) |

| (US_IDR) LIN Checksum Error Interrupt Disable More... | |

| #define | US_IDR_LINHTE (0x1u << 31) |

| (US_IDR) LIN Header Timeout Error Interrupt Disable More... | |

| #define | US_IDR_LINID (0x1u << 14) |

| (US_IDR) LIN Identifier Sent or LIN Identifier Received Interrupt Disable More... | |

| #define | US_IDR_LINIPE (0x1u << 27) |

| (US_IDR) LIN Identifier Parity Interrupt Disable More... | |

| #define | US_IDR_LINISFE (0x1u << 26) |

| (US_IDR) LIN Inconsistent Synch Field Error Interrupt Disable More... | |

| #define | US_IDR_LINSNRE (0x1u << 29) |

| (US_IDR) LIN Slave Not Responding Error Interrupt Disable More... | |

| #define | US_IDR_LINSTE (0x1u << 30) |

| (US_IDR) LIN Synch Tolerance Error Interrupt Disable More... | |

| #define | US_IDR_LINTC (0x1u << 15) |

| (US_IDR) LIN Transfer Completed Interrupt Disable More... | |

| #define | US_IDR_LRXD (0x1u << 27) |

| (US_IDR) LON Reception Done Interrupt Disable More... | |

| #define | US_IDR_LSFE (0x1u << 6) |

| (US_IDR) LON Short Frame Error Interrupt Disable More... | |

| #define | US_IDR_LTXD (0x1u << 24) |

| (US_IDR) LON Transmission Done Interrupt Disable More... | |

| #define | US_IDR_MANE (0x1u << 24) |

| (US_IDR) Manchester Error Interrupt Disable More... | |

| #define | US_IDR_NACK (0x1u << 13) |

| (US_IDR) Non Acknowledge Interrupt Disable More... | |

| #define | US_IDR_NSSE (0x1u << 19) |

| (US_IDR) NSS Line (Driving CTS Pin) Rising or Falling Edge Event Interrupt Disable More... | |

| #define | US_IDR_OVRE (0x1u << 5) |

| (US_IDR) Overrun Error Interrupt Enable More... | |

| #define | US_IDR_PARE (0x1u << 7) |

| (US_IDR) Parity Error Interrupt Disable More... | |

| #define | US_IDR_RIIC (0x1u << 16) |

| (US_IDR) Ring Indicator Input Change Disable More... | |

| #define | US_IDR_RXBRK (0x1u << 2) |

| (US_IDR) Receiver Break Interrupt Disable More... | |

| #define | US_IDR_RXRDY (0x1u << 0) |

| (US_IDR) RXRDY Interrupt Disable More... | |

| #define | US_IDR_TIMEOUT (0x1u << 8) |

| (US_IDR) Time-out Interrupt Disable More... | |

| #define | US_IDR_TXEMPTY (0x1u << 9) |

| (US_IDR) TXEMPTY Interrupt Disable More... | |

| #define | US_IDR_TXRDY (0x1u << 1) |

| (US_IDR) TXRDY Interrupt Disable More... | |

| #define | US_IDR_UNRE (0x1u << 10) |

| (US_IDR) SPI Underrun Error Interrupt Disable More... | |

| #define | US_IDTRX_IDTRX(value) ((US_IDTRX_IDTRX_Msk & ((value) << US_IDTRX_IDTRX_Pos))) |

| #define | US_IDTRX_IDTRX_Msk (0xffffffu << US_IDTRX_IDTRX_Pos) |

| (US_IDTRX) LON Indeterminate Time after Reception (comm_type = 1 mode only) More... | |

| #define | US_IDTRX_IDTRX_Pos 0 |

| #define | US_IDTTX_IDTTX(value) ((US_IDTTX_IDTTX_Msk & ((value) << US_IDTTX_IDTTX_Pos))) |

| #define | US_IDTTX_IDTTX_Msk (0xffffffu << US_IDTTX_IDTTX_Pos) |

| (US_IDTTX) LON Indeterminate Time after Transmission (comm_type = 1 mode only) More... | |

| #define | US_IDTTX_IDTTX_Pos 0 |

| #define | US_IER_CTSIC (0x1u << 19) |

| (US_IER) Clear to Send Input Change Interrupt Enable More... | |

| #define | US_IER_DCDIC (0x1u << 18) |

| (US_IER) Data Carrier Detect Input Change Interrupt Enable More... | |

| #define | US_IER_DSRIC (0x1u << 17) |

| (US_IER) Data Set Ready Input Change Enable More... | |

| #define | US_IER_FRAME (0x1u << 6) |

| (US_IER) Framing Error Interrupt Enable More... | |

| #define | US_IER_ITER (0x1u << 10) |

| (US_IER) Max number of Repetitions Reached Interrupt Enable More... | |

| #define | US_IER_LBLOVFE (0x1u << 28) |

| (US_IER) LON Backlog Overflow Error Interrupt Enable More... | |

| #define | US_IER_LCOL (0x1u << 25) |

| (US_IER) LON Collision Interrupt Enable More... | |

| #define | US_IER_LCRCE (0x1u << 7) |

| (US_IER) LON CRC Error Interrupt Enable More... | |

| #define | US_IER_LFET (0x1u << 26) |

| (US_IER) LON Frame Early Termination Interrupt Enable More... | |

| #define | US_IER_LINBE (0x1u << 25) |

| (US_IER) LIN Bus Error Interrupt Enable More... | |

| #define | US_IER_LINBK (0x1u << 13) |

| (US_IER) LIN Break Sent or LIN Break Received Interrupt Enable More... | |

| #define | US_IER_LINCE (0x1u << 28) |

| (US_IER) LIN Checksum Error Interrupt Enable More... | |

| #define | US_IER_LINHTE (0x1u << 31) |

| (US_IER) LIN Header Timeout Error Interrupt Enable More... | |

| #define | US_IER_LINID (0x1u << 14) |

| (US_IER) LIN Identifier Sent or LIN Identifier Received Interrupt Enable More... | |

| #define | US_IER_LINIPE (0x1u << 27) |

| (US_IER) LIN Identifier Parity Interrupt Enable More... | |

| #define | US_IER_LINISFE (0x1u << 26) |

| (US_IER) LIN Inconsistent Synch Field Error Interrupt Enable More... | |

| #define | US_IER_LINSNRE (0x1u << 29) |

| (US_IER) LIN Slave Not Responding Error Interrupt Enable More... | |

| #define | US_IER_LINSTE (0x1u << 30) |

| (US_IER) LIN Synch Tolerance Error Interrupt Enable More... | |

| #define | US_IER_LINTC (0x1u << 15) |

| (US_IER) LIN Transfer Completed Interrupt Enable More... | |

| #define | US_IER_LRXD (0x1u << 27) |

| (US_IER) LON Reception Done Interrupt Enable More... | |

| #define | US_IER_LSFE (0x1u << 6) |

| (US_IER) LON Short Frame Error Interrupt Enable More... | |

| #define | US_IER_LTXD (0x1u << 24) |

| (US_IER) LON Transmission Done Interrupt Enable More... | |

| #define | US_IER_MANE (0x1u << 24) |

| (US_IER) Manchester Error Interrupt Enable More... | |

| #define | US_IER_NACK (0x1u << 13) |

| (US_IER) Non Acknowledge Interrupt Enable More... | |

| #define | US_IER_NSSE (0x1u << 19) |

| (US_IER) NSS Line (Driving CTS Pin) Rising or Falling Edge Event Interrupt Enable More... | |

| #define | US_IER_OVRE (0x1u << 5) |

| (US_IER) Overrun Error Interrupt Enable More... | |

| #define | US_IER_PARE (0x1u << 7) |

| (US_IER) Parity Error Interrupt Enable More... | |

| #define | US_IER_RIIC (0x1u << 16) |

| (US_IER) Ring Indicator Input Change Enable More... | |

| #define | US_IER_RXBRK (0x1u << 2) |

| (US_IER) Receiver Break Interrupt Enable More... | |

| #define | US_IER_RXRDY (0x1u << 0) |

| (US_IER) RXRDY Interrupt Enable More... | |

| #define | US_IER_TIMEOUT (0x1u << 8) |

| (US_IER) Time-out Interrupt Enable More... | |

| #define | US_IER_TXEMPTY (0x1u << 9) |

| (US_IER) TXEMPTY Interrupt Enable More... | |

| #define | US_IER_TXRDY (0x1u << 1) |

| (US_IER) TXRDY Interrupt Enable More... | |

| #define | US_IER_UNRE (0x1u << 10) |

| (US_IER) SPI Underrun Error Interrupt Enable More... | |

| #define | US_IF_IRDA_FILTER(value) ((US_IF_IRDA_FILTER_Msk & ((value) << US_IF_IRDA_FILTER_Pos))) |

| #define | US_IF_IRDA_FILTER_Msk (0xffu << US_IF_IRDA_FILTER_Pos) |

| (US_IF) IrDA Filter More... | |

| #define | US_IF_IRDA_FILTER_Pos 0 |

| #define | US_IMR_CTSIC (0x1u << 19) |

| (US_IMR) Clear to Send Input Change Interrupt Mask More... | |

| #define | US_IMR_DCDIC (0x1u << 18) |

| (US_IMR) Data Carrier Detect Input Change Interrupt Mask More... | |

| #define | US_IMR_DSRIC (0x1u << 17) |

| (US_IMR) Data Set Ready Input Change Mask More... | |

| #define | US_IMR_FRAME (0x1u << 6) |

| (US_IMR) Framing Error Interrupt Mask More... | |

| #define | US_IMR_ITER (0x1u << 10) |

| (US_IMR) Max Number of Repetitions Reached Interrupt Mask More... | |

| #define | US_IMR_LBLOVFE (0x1u << 28) |

| (US_IMR) LON Backlog Overflow Error Interrupt Mask More... | |

| #define | US_IMR_LCOL (0x1u << 25) |

| (US_IMR) LON Collision Interrupt Mask More... | |

| #define | US_IMR_LCRCE (0x1u << 7) |

| (US_IMR) LON CRC Error Interrupt Mask More... | |

| #define | US_IMR_LFET (0x1u << 26) |

| (US_IMR) LON Frame Early Termination Interrupt Mask More... | |

| #define | US_IMR_LINBE (0x1u << 25) |

| (US_IMR) LIN Bus Error Interrupt Mask More... | |

| #define | US_IMR_LINBK (0x1u << 13) |

| (US_IMR) LIN Break Sent or LIN Break Received Interrupt Mask More... | |

| #define | US_IMR_LINCE (0x1u << 28) |

| (US_IMR) LIN Checksum Error Interrupt Mask More... | |

| #define | US_IMR_LINHTE (0x1u << 31) |

| (US_IMR) LIN Header Timeout Error Interrupt Mask More... | |

| #define | US_IMR_LINID (0x1u << 14) |

| (US_IMR) LIN Identifier Sent or LIN Identifier Received Interrupt Mask More... | |

| #define | US_IMR_LINIPE (0x1u << 27) |

| (US_IMR) LIN Identifier Parity Interrupt Mask More... | |

| #define | US_IMR_LINISFE (0x1u << 26) |

| (US_IMR) LIN Inconsistent Synch Field Error Interrupt Mask More... | |

| #define | US_IMR_LINSNRE (0x1u << 29) |

| (US_IMR) LIN Slave Not Responding Error Interrupt Mask More... | |

| #define | US_IMR_LINSTE (0x1u << 30) |

| (US_IMR) LIN Synch Tolerance Error Interrupt Mask More... | |

| #define | US_IMR_LINTC (0x1u << 15) |

| (US_IMR) LIN Transfer Completed Interrupt Mask More... | |

| #define | US_IMR_LRXD (0x1u << 27) |

| (US_IMR) LON Reception Done Interrupt Mask More... | |

| #define | US_IMR_LSFE (0x1u << 6) |

| (US_IMR) LON Short Frame Error Interrupt Mask More... | |

| #define | US_IMR_LTXD (0x1u << 24) |

| (US_IMR) LON Transmission Done Interrupt Mask More... | |

| #define | US_IMR_MANE (0x1u << 24) |

| (US_IMR) Manchester Error Interrupt Mask More... | |

| #define | US_IMR_NACK (0x1u << 13) |

| (US_IMR) Non Acknowledge Interrupt Mask More... | |

| #define | US_IMR_NSSE (0x1u << 19) |

| (US_IMR) NSS Line (Driving CTS Pin) Rising or Falling Edge Event Interrupt Mask More... | |

| #define | US_IMR_OVRE (0x1u << 5) |

| (US_IMR) Overrun Error Interrupt Mask More... | |

| #define | US_IMR_PARE (0x1u << 7) |

| (US_IMR) Parity Error Interrupt Mask More... | |

| #define | US_IMR_RIIC (0x1u << 16) |

| (US_IMR) Ring Indicator Input Change Mask More... | |

| #define | US_IMR_RXBRK (0x1u << 2) |

| (US_IMR) Receiver Break Interrupt Mask More... | |

| #define | US_IMR_RXRDY (0x1u << 0) |

| (US_IMR) RXRDY Interrupt Mask More... | |

| #define | US_IMR_TIMEOUT (0x1u << 8) |

| (US_IMR) Time-out Interrupt Mask More... | |

| #define | US_IMR_TXEMPTY (0x1u << 9) |

| (US_IMR) TXEMPTY Interrupt Mask More... | |

| #define | US_IMR_TXRDY (0x1u << 1) |

| (US_IMR) TXRDY Interrupt Mask More... | |

| #define | US_IMR_UNRE (0x1u << 10) |

| (US_IMR) SPI Underrun Error Interrupt Mask More... | |

| #define | US_LINBRR_LINCD_Msk (0xffffu << US_LINBRR_LINCD_Pos) |

| (US_LINBRR) Clock Divider after Synchronization More... | |

| #define | US_LINBRR_LINCD_Pos 0 |

| #define | US_LINBRR_LINFP_Msk (0x7u << US_LINBRR_LINFP_Pos) |

| (US_LINBRR) Fractional Part after Synchronization More... | |

| #define | US_LINBRR_LINFP_Pos 16 |

| #define | US_LINIR_IDCHR(value) ((US_LINIR_IDCHR_Msk & ((value) << US_LINIR_IDCHR_Pos))) |

| #define | US_LINIR_IDCHR_Msk (0xffu << US_LINIR_IDCHR_Pos) |

| (US_LINIR) Identifier Character More... | |

| #define | US_LINIR_IDCHR_Pos 0 |

| #define | US_LINMR_CHKDIS (0x1u << 3) |

| (US_LINMR) Checksum Disable More... | |

| #define | US_LINMR_CHKTYP (0x1u << 4) |

| (US_LINMR) Checksum Type More... | |

| #define | US_LINMR_DLC(value) ((US_LINMR_DLC_Msk & ((value) << US_LINMR_DLC_Pos))) |

| #define | US_LINMR_DLC_Msk (0xffu << US_LINMR_DLC_Pos) |

| (US_LINMR) Data Length Control More... | |

| #define | US_LINMR_DLC_Pos 8 |

| #define | US_LINMR_DLM (0x1u << 5) |

| (US_LINMR) Data Length Mode More... | |

| #define | US_LINMR_FSDIS (0x1u << 6) |

| (US_LINMR) Frame Slot Mode Disable More... | |

| #define | US_LINMR_NACT(value) ((US_LINMR_NACT_Msk & ((value) << US_LINMR_NACT_Pos))) |

| #define | US_LINMR_NACT_IGNORE (0x2u << 0) |

| (US_LINMR) The USART does not transmit and does not receive the response. More... | |

| #define | US_LINMR_NACT_Msk (0x3u << US_LINMR_NACT_Pos) |

| (US_LINMR) LIN Node Action More... | |

| #define | US_LINMR_NACT_Pos 0 |

| #define | US_LINMR_NACT_PUBLISH (0x0u << 0) |

| (US_LINMR) The USART transmits the response. More... | |

| #define | US_LINMR_NACT_SUBSCRIBE (0x1u << 0) |

| (US_LINMR) The USART receives the response. More... | |

| #define | US_LINMR_PARDIS (0x1u << 2) |

| (US_LINMR) Parity Disable More... | |

| #define | US_LINMR_PDCM (0x1u << 16) |

| (US_LINMR) DMAC Mode More... | |

| #define | US_LINMR_SYNCDIS (0x1u << 17) |

| (US_LINMR) Synchronization Disable More... | |

| #define | US_LINMR_WKUPTYP (0x1u << 7) |

| (US_LINMR) Wakeup Signal Type More... | |

| #define | US_LONB1RX_BETA1RX(value) ((US_LONB1RX_BETA1RX_Msk & ((value) << US_LONB1RX_BETA1RX_Pos))) |

| #define | US_LONB1RX_BETA1RX_Msk (0xffffffu << US_LONB1RX_BETA1RX_Pos) |

| (US_LONB1RX) LON Beta1 Length after Reception More... | |

| #define | US_LONB1RX_BETA1RX_Pos 0 |

| #define | US_LONB1TX_BETA1TX(value) ((US_LONB1TX_BETA1TX_Msk & ((value) << US_LONB1TX_BETA1TX_Pos))) |

| #define | US_LONB1TX_BETA1TX_Msk (0xffffffu << US_LONB1TX_BETA1TX_Pos) |

| (US_LONB1TX) LON Beta1 Length after Transmission More... | |

| #define | US_LONB1TX_BETA1TX_Pos 0 |

| #define | US_LONBL_LONBL_Msk (0x3fu << US_LONBL_LONBL_Pos) |

| (US_LONBL) LON Node Backlog Value More... | |

| #define | US_LONBL_LONBL_Pos 0 |

| #define | US_LONDL_LONDL(value) ((US_LONDL_LONDL_Msk & ((value) << US_LONDL_LONDL_Pos))) |

| #define | US_LONDL_LONDL_Msk (0xffu << US_LONDL_LONDL_Pos) |

| (US_LONDL) LON Data Length More... | |

| #define | US_LONDL_LONDL_Pos 0 |

| #define | US_LONL2HDR_ALTP (0x1u << 6) |

| (US_LONL2HDR) LON Alternate Path Bit More... | |

| #define | US_LONL2HDR_BLI(value) ((US_LONL2HDR_BLI_Msk & ((value) << US_LONL2HDR_BLI_Pos))) |

| #define | US_LONL2HDR_BLI_Msk (0x3fu << US_LONL2HDR_BLI_Pos) |

| (US_LONL2HDR) LON Backlog Increment More... | |

| #define | US_LONL2HDR_BLI_Pos 0 |

| #define | US_LONL2HDR_PB (0x1u << 7) |

| (US_LONL2HDR) LON Priority Bit More... | |

| #define | US_LONMR_CDTAIL (0x1u << 3) |

| (US_LONMR) LON Collision Detection on Frame Tail More... | |

| #define | US_LONMR_COLDET (0x1u << 1) |

| (US_LONMR) LON Collision Detection Feature More... | |

| #define | US_LONMR_COMMT (0x1u << 0) |

| (US_LONMR) LON comm_type Parameter Value More... | |

| #define | US_LONMR_DMAM (0x1u << 4) |

| (US_LONMR) LON DMA Mode More... | |

| #define | US_LONMR_EOFS(value) ((US_LONMR_EOFS_Msk & ((value) << US_LONMR_EOFS_Pos))) |

| #define | US_LONMR_EOFS_Msk (0xffu << US_LONMR_EOFS_Pos) |

| (US_LONMR) End of Frame Condition Size More... | |

| #define | US_LONMR_EOFS_Pos 16 |

| #define | US_LONMR_LCDS (0x1u << 5) |

| (US_LONMR) LON Collision Detection Source More... | |

| #define | US_LONMR_TCOL (0x1u << 2) |

| (US_LONMR) Terminate Frame upon Collision Notification More... | |

| #define | US_LONPR_LONPL(value) ((US_LONPR_LONPL_Msk & ((value) << US_LONPR_LONPL_Pos))) |

| #define | US_LONPR_LONPL_Msk (0x3fffu << US_LONPR_LONPL_Pos) |

| (US_LONPR) LON Preamble Length More... | |

| #define | US_LONPR_LONPL_Pos 0 |

| #define | US_LONPRIO_NPS(value) ((US_LONPRIO_NPS_Msk & ((value) << US_LONPRIO_NPS_Pos))) |

| #define | US_LONPRIO_NPS_Msk (0x7fu << US_LONPRIO_NPS_Pos) |

| (US_LONPRIO) LON Node Priority Slot More... | |

| #define | US_LONPRIO_NPS_Pos 8 |

| #define | US_LONPRIO_PSNB(value) ((US_LONPRIO_PSNB_Msk & ((value) << US_LONPRIO_PSNB_Pos))) |

| #define | US_LONPRIO_PSNB_Msk (0x7fu << US_LONPRIO_PSNB_Pos) |

| (US_LONPRIO) LON Priority Slot Number More... | |

| #define | US_LONPRIO_PSNB_Pos 0 |

| #define | US_MAN_DRIFT (0x1u << 30) |

| (US_MAN) Drift Compensation More... | |

| #define | US_MAN_ONE (0x1u << 29) |

| (US_MAN) Must Be Set to 1 More... | |

| #define | US_MAN_RX_MPOL (0x1u << 28) |

| (US_MAN) Receiver Manchester Polarity More... | |

| #define | US_MAN_RX_PL(value) ((US_MAN_RX_PL_Msk & ((value) << US_MAN_RX_PL_Pos))) |

| #define | US_MAN_RX_PL_Msk (0xfu << US_MAN_RX_PL_Pos) |

| (US_MAN) Receiver Preamble Length More... | |

| #define | US_MAN_RX_PL_Pos 16 |

| #define | US_MAN_RX_PP(value) ((US_MAN_RX_PP_Msk & ((value) << US_MAN_RX_PP_Pos))) |

| #define | US_MAN_RX_PP_ALL_ONE (0x0u << 24) |

| (US_MAN) The preamble is composed of '1's More... | |

| #define | US_MAN_RX_PP_ALL_ZERO (0x1u << 24) |

| (US_MAN) The preamble is composed of '0's More... | |

| #define | US_MAN_RX_PP_Msk (0x3u << US_MAN_RX_PP_Pos) |

| (US_MAN) Receiver Preamble Pattern detected More... | |

| #define | US_MAN_RX_PP_ONE_ZERO (0x3u << 24) |

| (US_MAN) The preamble is composed of '10's More... | |

| #define | US_MAN_RX_PP_Pos 24 |

| #define | US_MAN_RX_PP_ZERO_ONE (0x2u << 24) |

| (US_MAN) The preamble is composed of '01's More... | |

| #define | US_MAN_RXIDLEV (0x1u << 31) |

| (US_MAN) More... | |

| #define | US_MAN_TX_MPOL (0x1u << 12) |

| (US_MAN) Transmitter Manchester Polarity More... | |

| #define | US_MAN_TX_PL(value) ((US_MAN_TX_PL_Msk & ((value) << US_MAN_TX_PL_Pos))) |

| #define | US_MAN_TX_PL_Msk (0xfu << US_MAN_TX_PL_Pos) |

| (US_MAN) Transmitter Preamble Length More... | |

| #define | US_MAN_TX_PL_Pos 0 |

| #define | US_MAN_TX_PP(value) ((US_MAN_TX_PP_Msk & ((value) << US_MAN_TX_PP_Pos))) |

| #define | US_MAN_TX_PP_ALL_ONE (0x0u << 8) |

| (US_MAN) The preamble is composed of '1's More... | |

| #define | US_MAN_TX_PP_ALL_ZERO (0x1u << 8) |

| (US_MAN) The preamble is composed of '0's More... | |

| #define | US_MAN_TX_PP_Msk (0x3u << US_MAN_TX_PP_Pos) |

| (US_MAN) Transmitter Preamble Pattern More... | |

| #define | US_MAN_TX_PP_ONE_ZERO (0x3u << 8) |

| (US_MAN) The preamble is composed of '10's More... | |

| #define | US_MAN_TX_PP_Pos 8 |

| #define | US_MAN_TX_PP_ZERO_ONE (0x2u << 8) |

| (US_MAN) The preamble is composed of '01's More... | |

| #define | US_MR_CHMODE(value) ((US_MR_CHMODE_Msk & ((value) << US_MR_CHMODE_Pos))) |

| #define | US_MR_CHMODE_AUTOMATIC (0x1u << 14) |

| (US_MR) Automatic Echo. Receiver input is connected to the TXD pin. More... | |

| #define | US_MR_CHMODE_LOCAL_LOOPBACK (0x2u << 14) |

| (US_MR) Local Loopback. Transmitter output is connected to the Receiver Input. More... | |

| #define | US_MR_CHMODE_Msk (0x3u << US_MR_CHMODE_Pos) |

| (US_MR) Channel Mode More... | |

| #define | US_MR_CHMODE_NORMAL (0x0u << 14) |

| (US_MR) Normal mode More... | |

| #define | US_MR_CHMODE_Pos 14 |

| #define | US_MR_CHMODE_REMOTE_LOOPBACK (0x3u << 14) |

| (US_MR) Remote Loopback. RXD pin is internally connected to the TXD pin. More... | |

| #define | US_MR_CHRL(value) ((US_MR_CHRL_Msk & ((value) << US_MR_CHRL_Pos))) |

| #define | US_MR_CHRL_5_BIT (0x0u << 6) |

| (US_MR) Character length is 5 bits More... | |

| #define | US_MR_CHRL_6_BIT (0x1u << 6) |

| (US_MR) Character length is 6 bits More... | |

| #define | US_MR_CHRL_7_BIT (0x2u << 6) |

| (US_MR) Character length is 7 bits More... | |

| #define | US_MR_CHRL_8_BIT (0x3u << 6) |

| (US_MR) Character length is 8 bits More... | |

| #define | US_MR_CHRL_Msk (0x3u << US_MR_CHRL_Pos) |

| (US_MR) Character Length More... | |

| #define | US_MR_CHRL_Pos 6 |

| #define | US_MR_CLKO (0x1u << 18) |

| (US_MR) Clock Output Select More... | |

| #define | US_MR_CPHA (0x1u << 8) |

| (US_MR) SPI Clock Phase More... | |

| #define | US_MR_CPOL (0x1u << 16) |

| (US_MR) SPI Clock Polarity More... | |

| #define | US_MR_DSNACK (0x1u << 21) |

| (US_MR) Disable Successive NACK More... | |

| #define | US_MR_FILTER (0x1u << 28) |

| (US_MR) Receive Line Filter More... | |

| #define | US_MR_INACK (0x1u << 20) |

| (US_MR) Inhibit Non Acknowledge More... | |

| #define | US_MR_INVDATA (0x1u << 23) |

| (US_MR) Inverted Data More... | |

| #define | US_MR_MAN (0x1u << 29) |

| (US_MR) Manchester Encoder/Decoder Enable More... | |

| #define | US_MR_MAX_ITERATION(value) ((US_MR_MAX_ITERATION_Msk & ((value) << US_MR_MAX_ITERATION_Pos))) |

| #define | US_MR_MAX_ITERATION_Msk (0x7u << US_MR_MAX_ITERATION_Pos) |

| (US_MR) Maximum Number of Automatic Iteration More... | |

| #define | US_MR_MAX_ITERATION_Pos 24 |

| #define | US_MR_MODE9 (0x1u << 17) |

| (US_MR) 9-bit Character Length More... | |

| #define | US_MR_MODSYNC (0x1u << 30) |

| (US_MR) Manchester Synchronization Mode More... | |

| #define | US_MR_MSBF (0x1u << 16) |

| (US_MR) Bit Order More... | |

| #define | US_MR_NBSTOP(value) ((US_MR_NBSTOP_Msk & ((value) << US_MR_NBSTOP_Pos))) |

| #define | US_MR_NBSTOP_1_5_BIT (0x1u << 12) |

| (US_MR) 1.5 stop bit (SYNC = 0) or reserved (SYNC = 1) More... | |

| #define | US_MR_NBSTOP_1_BIT (0x0u << 12) |

| (US_MR) 1 stop bit More... | |

| #define | US_MR_NBSTOP_2_BIT (0x2u << 12) |

| (US_MR) 2 stop bits More... | |

| #define | US_MR_NBSTOP_Msk (0x3u << US_MR_NBSTOP_Pos) |

| (US_MR) Number of Stop Bits More... | |

| #define | US_MR_NBSTOP_Pos 12 |

| #define | US_MR_ONEBIT (0x1u << 31) |

| (US_MR) Start Frame Delimiter Selector More... | |

| #define | US_MR_OVER (0x1u << 19) |

| (US_MR) Oversampling Mode More... | |

| #define | US_MR_PAR(value) ((US_MR_PAR_Msk & ((value) << US_MR_PAR_Pos))) |

| #define | US_MR_PAR_EVEN (0x0u << 9) |

| (US_MR) Even parity More... | |

| #define | US_MR_PAR_MARK (0x3u << 9) |

| (US_MR) Parity forced to 1 (Mark) More... | |

| #define | US_MR_PAR_Msk (0x7u << US_MR_PAR_Pos) |

| (US_MR) Parity Type More... | |

| #define | US_MR_PAR_MULTIDROP (0x6u << 9) |

| (US_MR) Multidrop mode More... | |

| #define | US_MR_PAR_NO (0x4u << 9) |

| (US_MR) No parity More... | |

| #define | US_MR_PAR_ODD (0x1u << 9) |

| (US_MR) Odd parity More... | |

| #define | US_MR_PAR_Pos 9 |

| #define | US_MR_PAR_SPACE (0x2u << 9) |

| (US_MR) Parity forced to 0 (Space) More... | |

| #define | US_MR_SYNC (0x1u << 8) |

| (US_MR) Synchronous Mode Select More... | |

| #define | US_MR_USART_MODE(value) ((US_MR_USART_MODE_Msk & ((value) << US_MR_USART_MODE_Pos))) |

| #define | US_MR_USART_MODE_HW_HANDSHAKING (0x2u << 0) |

| (US_MR) Hardware Handshaking More... | |

| #define | US_MR_USART_MODE_IRDA (0x8u << 0) |

| (US_MR) IrDA More... | |

| #define | US_MR_USART_MODE_IS07816_T_0 (0x4u << 0) |

| (US_MR) IS07816 Protocol: T = 0 More... | |

| #define | US_MR_USART_MODE_IS07816_T_1 (0x6u << 0) |

| (US_MR) IS07816 Protocol: T = 1 More... | |

| #define | US_MR_USART_MODE_LIN_MASTER (0xAu << 0) |

| (US_MR) LIN Master mode More... | |

| #define | US_MR_USART_MODE_LIN_SLAVE (0xBu << 0) |

| (US_MR) LIN Slave mode More... | |

| #define | US_MR_USART_MODE_LON (0x9u << 0) |

| (US_MR) LON More... | |

| #define | US_MR_USART_MODE_MODEM (0x3u << 0) |

| (US_MR) Modem More... | |

| #define | US_MR_USART_MODE_Msk (0xfu << US_MR_USART_MODE_Pos) |

| (US_MR) USART Mode of Operation More... | |

| #define | US_MR_USART_MODE_NORMAL (0x0u << 0) |

| (US_MR) Normal mode More... | |

| #define | US_MR_USART_MODE_Pos 0 |

| #define | US_MR_USART_MODE_RS485 (0x1u << 0) |

| (US_MR) RS485 More... | |

| #define | US_MR_USART_MODE_SPI_MASTER (0xEu << 0) |

| (US_MR) SPI master mode (CLKO must be written to 1 and USCLKS = 0, 1 or 2) More... | |

| #define | US_MR_USART_MODE_SPI_SLAVE (0xFu << 0) |

| (US_MR) SPI Slave mode More... | |

| #define | US_MR_USCLKS(value) ((US_MR_USCLKS_Msk & ((value) << US_MR_USCLKS_Pos))) |

| #define | US_MR_USCLKS_DIV (0x1u << 4) |

| (US_MR) Peripheral clock divided (DIV=DIV=8) is selected More... | |

| #define | US_MR_USCLKS_MCK (0x0u << 4) |

| (US_MR) Peripheral clock is selected More... | |

| #define | US_MR_USCLKS_Msk (0x3u << US_MR_USCLKS_Pos) |

| (US_MR) Clock Selection More... | |

| #define | US_MR_USCLKS_PCK (0x2u << 4) |

| (US_MR) PMC programmable clock (PCK) is selected. If the SCK pin is driven (CLKO = 1), the CD field must be greater than 1. More... | |

| #define | US_MR_USCLKS_Pos 4 |

| #define | US_MR_USCLKS_SCK (0x3u << 4) |

| (US_MR) Serial clock (SCK) is selected More... | |

| #define | US_MR_VAR_SYNC (0x1u << 22) |

| (US_MR) Variable Synchronization of Command/Data Sync Start Frame Delimiter More... | |

| #define | US_MR_WRDBT (0x1u << 20) |

| (US_MR) Wait Read Data Before Transfer More... | |

| #define | US_NER_NB_ERRORS_Msk (0xffu << US_NER_NB_ERRORS_Pos) |

| (US_NER) Number of Errors More... | |

| #define | US_NER_NB_ERRORS_Pos 0 |

| #define | US_RHR_RXCHR_Msk (0x1ffu << US_RHR_RXCHR_Pos) |

| (US_RHR) Received Character More... | |

| #define | US_RHR_RXCHR_Pos 0 |

| #define | US_RHR_RXSYNH (0x1u << 15) |

| (US_RHR) Received Sync More... | |

| #define | US_RTOR_TO(value) ((US_RTOR_TO_Msk & ((value) << US_RTOR_TO_Pos))) |

| #define | US_RTOR_TO_Msk (0x1ffffu << US_RTOR_TO_Pos) |

| (US_RTOR) Time-out Value More... | |

| #define | US_RTOR_TO_Pos 0 |

| #define | US_THR_TXCHR(value) ((US_THR_TXCHR_Msk & ((value) << US_THR_TXCHR_Pos))) |

| #define | US_THR_TXCHR_Msk (0x1ffu << US_THR_TXCHR_Pos) |

| (US_THR) Character to be Transmitted More... | |

| #define | US_THR_TXCHR_Pos 0 |

| #define | US_THR_TXSYNH (0x1u << 15) |

| (US_THR) Sync Field to be Transmitted More... | |

| #define | US_TTGR_PCYCLE(value) ((US_TTGR_PCYCLE_Msk & ((value) << US_TTGR_PCYCLE_Pos))) |

| #define | US_TTGR_PCYCLE_Msk (0xffffffu << US_TTGR_PCYCLE_Pos) |

| (US_TTGR) LON PCYCLE Length More... | |

| #define | US_TTGR_PCYCLE_Pos 0 |

| #define | US_TTGR_TG(value) ((US_TTGR_TG_Msk & ((value) << US_TTGR_TG_Pos))) |

| #define | US_TTGR_TG_Msk (0xffu << US_TTGR_TG_Pos) |

| (US_TTGR) Timeguard Value More... | |

| #define | US_TTGR_TG_Pos 0 |

| #define | US_VERSION_MFN_Msk (0x7u << US_VERSION_MFN_Pos) |

| (US_VERSION) Metal Fix Number More... | |

| #define | US_VERSION_MFN_Pos 16 |

| #define | US_VERSION_VERSION_Msk (0xfffu << US_VERSION_VERSION_Pos) |

| (US_VERSION) Hardware Module Version More... | |

| #define | US_VERSION_VERSION_Pos 0 |

| #define | US_WPMR_WPEN (0x1u << 0) |

| (US_WPMR) Write Protection Enable More... | |

| #define | US_WPMR_WPKEY(value) ((US_WPMR_WPKEY_Msk & ((value) << US_WPMR_WPKEY_Pos))) |

| #define | US_WPMR_WPKEY_Msk (0xffffffu << US_WPMR_WPKEY_Pos) |

| (US_WPMR) Write Protection Key More... | |

| #define | US_WPMR_WPKEY_PASSWD (0x555341u << 8) |

| (US_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0. More... | |

| #define | US_WPMR_WPKEY_Pos 8 |

| #define | US_WPSR_WPVS (0x1u << 0) |

| (US_WPSR) Write Protection Violation Status More... | |

| #define | US_WPSR_WPVSRC_Msk (0xffffu << US_WPSR_WPVSRC_Pos) |

| (US_WPSR) Write Protection Violation Source More... | |

| #define | US_WPSR_WPVSRC_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/usart.h.