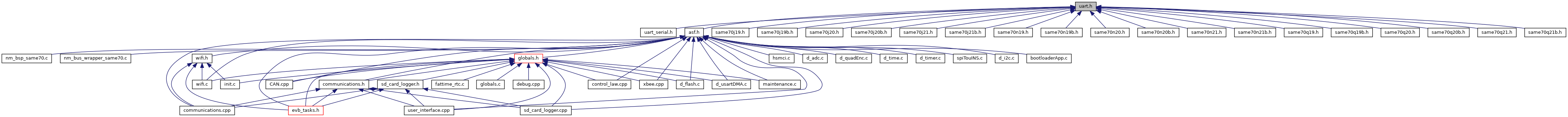

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Uart |

| Uart hardware registers. More... | |

Macros | |

| #define | UART_BRGR_CD(value) ((UART_BRGR_CD_Msk & ((value) << UART_BRGR_CD_Pos))) |

| #define | UART_BRGR_CD_Msk (0xffffu << UART_BRGR_CD_Pos) |

| (UART_BRGR) Clock Divisor More... | |

| #define | UART_BRGR_CD_Pos 0 |

| #define | UART_CMPR_CMPMODE (0x1u << 12) |

| (UART_CMPR) Comparison Mode More... | |

| #define | UART_CMPR_CMPMODE_FLAG_ONLY (0x0u << 12) |

| (UART_CMPR) Any character is received and comparison function drives CMP flag. More... | |

| #define | UART_CMPR_CMPMODE_START_CONDITION (0x1u << 12) |

| (UART_CMPR) Comparison condition must be met to start reception. More... | |

| #define | UART_CMPR_CMPPAR (0x1u << 14) |

| (UART_CMPR) Compare Parity More... | |

| #define | UART_CMPR_VAL1(value) ((UART_CMPR_VAL1_Msk & ((value) << UART_CMPR_VAL1_Pos))) |

| #define | UART_CMPR_VAL1_Msk (0xffu << UART_CMPR_VAL1_Pos) |

| (UART_CMPR) First Comparison Value for Received Character More... | |

| #define | UART_CMPR_VAL1_Pos 0 |

| #define | UART_CMPR_VAL2(value) ((UART_CMPR_VAL2_Msk & ((value) << UART_CMPR_VAL2_Pos))) |

| #define | UART_CMPR_VAL2_Msk (0xffu << UART_CMPR_VAL2_Pos) |

| (UART_CMPR) Second Comparison Value for Received Character More... | |

| #define | UART_CMPR_VAL2_Pos 16 |

| #define | UART_CR_DBGE (0x1u << 15) |

| (UART_CR) Debug Enable More... | |

| #define | UART_CR_REQCLR (0x1u << 12) |

| (UART_CR) Request Clear More... | |

| #define | UART_CR_RSTRX (0x1u << 2) |

| (UART_CR) Reset Receiver More... | |

| #define | UART_CR_RSTSTA (0x1u << 8) |

| (UART_CR) Reset Status More... | |

| #define | UART_CR_RSTTX (0x1u << 3) |

| (UART_CR) Reset Transmitter More... | |

| #define | UART_CR_RXDIS (0x1u << 5) |

| (UART_CR) Receiver Disable More... | |

| #define | UART_CR_RXEN (0x1u << 4) |

| (UART_CR) Receiver Enable More... | |

| #define | UART_CR_TXDIS (0x1u << 7) |

| (UART_CR) Transmitter Disable More... | |

| #define | UART_CR_TXEN (0x1u << 6) |

| (UART_CR) Transmitter Enable More... | |

| #define | UART_IDR_CMP (0x1u << 15) |

| (UART_IDR) Disable Comparison Interrupt More... | |

| #define | UART_IDR_FRAME (0x1u << 6) |

| (UART_IDR) Disable Framing Error Interrupt More... | |

| #define | UART_IDR_OVRE (0x1u << 5) |

| (UART_IDR) Disable Overrun Error Interrupt More... | |

| #define | UART_IDR_PARE (0x1u << 7) |

| (UART_IDR) Disable Parity Error Interrupt More... | |

| #define | UART_IDR_RXRDY (0x1u << 0) |

| (UART_IDR) Disable RXRDY Interrupt More... | |

| #define | UART_IDR_TXEMPTY (0x1u << 9) |

| (UART_IDR) Disable TXEMPTY Interrupt More... | |

| #define | UART_IDR_TXRDY (0x1u << 1) |

| (UART_IDR) Disable TXRDY Interrupt More... | |

| #define | UART_IER_CMP (0x1u << 15) |

| (UART_IER) Enable Comparison Interrupt More... | |

| #define | UART_IER_FRAME (0x1u << 6) |

| (UART_IER) Enable Framing Error Interrupt More... | |

| #define | UART_IER_OVRE (0x1u << 5) |

| (UART_IER) Enable Overrun Error Interrupt More... | |

| #define | UART_IER_PARE (0x1u << 7) |

| (UART_IER) Enable Parity Error Interrupt More... | |

| #define | UART_IER_RXRDY (0x1u << 0) |

| (UART_IER) Enable RXRDY Interrupt More... | |

| #define | UART_IER_TXEMPTY (0x1u << 9) |

| (UART_IER) Enable TXEMPTY Interrupt More... | |

| #define | UART_IER_TXRDY (0x1u << 1) |

| (UART_IER) Enable TXRDY Interrupt More... | |

| #define | UART_IMR_CMP (0x1u << 15) |

| (UART_IMR) Mask Comparison Interrupt More... | |

| #define | UART_IMR_FRAME (0x1u << 6) |

| (UART_IMR) Mask Framing Error Interrupt More... | |

| #define | UART_IMR_OVRE (0x1u << 5) |

| (UART_IMR) Mask Overrun Error Interrupt More... | |

| #define | UART_IMR_PARE (0x1u << 7) |

| (UART_IMR) Mask Parity Error Interrupt More... | |

| #define | UART_IMR_RXRDY (0x1u << 0) |

| (UART_IMR) Mask RXRDY Interrupt More... | |

| #define | UART_IMR_TXEMPTY (0x1u << 9) |

| (UART_IMR) Mask TXEMPTY Interrupt More... | |

| #define | UART_IMR_TXRDY (0x1u << 1) |

| (UART_IMR) Disable TXRDY Interrupt More... | |

| #define | UART_MR_BRSRCCK (0x1u << 12) |

| (UART_MR) Baud Rate Source Clock More... | |

| #define | UART_MR_BRSRCCK_PERIPH_CLK (0x0u << 12) |

| (UART_MR) The baud rate is driven by the peripheral clock More... | |

| #define | UART_MR_BRSRCCK_PMC_PCK (0x1u << 12) |

| (UART_MR) The baud rate is driven by a PMC programmable clock PCK (see section Power Management Controller (PMC)). More... | |

| #define | UART_MR_CHMODE(value) ((UART_MR_CHMODE_Msk & ((value) << UART_MR_CHMODE_Pos))) |

| #define | UART_MR_CHMODE_AUTOMATIC (0x1u << 14) |

| (UART_MR) Automatic echo More... | |

| #define | UART_MR_CHMODE_LOCAL_LOOPBACK (0x2u << 14) |

| (UART_MR) Local loopback More... | |

| #define | UART_MR_CHMODE_Msk (0x3u << UART_MR_CHMODE_Pos) |

| (UART_MR) Channel Mode More... | |

| #define | UART_MR_CHMODE_NORMAL (0x0u << 14) |

| (UART_MR) Normal mode More... | |

| #define | UART_MR_CHMODE_Pos 14 |

| #define | UART_MR_CHMODE_REMOTE_LOOPBACK (0x3u << 14) |

| (UART_MR) Remote loopback More... | |

| #define | UART_MR_FILTER (0x1u << 4) |

| (UART_MR) Receiver Digital Filter More... | |

| #define | UART_MR_FILTER_DISABLED (0x0u << 4) |

| (UART_MR) UART does not filter the receive line. More... | |

| #define | UART_MR_FILTER_ENABLED (0x1u << 4) |

| (UART_MR) UART filters the receive line using a three-sample filter (16x-bit clock) (2 over 3 majority). More... | |

| #define | UART_MR_PAR(value) ((UART_MR_PAR_Msk & ((value) << UART_MR_PAR_Pos))) |

| #define | UART_MR_PAR_EVEN (0x0u << 9) |

| (UART_MR) Even Parity More... | |

| #define | UART_MR_PAR_MARK (0x3u << 9) |

| (UART_MR) Mark: parity forced to 1 More... | |

| #define | UART_MR_PAR_Msk (0x7u << UART_MR_PAR_Pos) |

| (UART_MR) Parity Type More... | |

| #define | UART_MR_PAR_NO (0x4u << 9) |

| (UART_MR) No parity More... | |

| #define | UART_MR_PAR_ODD (0x1u << 9) |

| (UART_MR) Odd Parity More... | |

| #define | UART_MR_PAR_Pos 9 |

| #define | UART_MR_PAR_SPACE (0x2u << 9) |

| (UART_MR) Space: parity forced to 0 More... | |

| #define | UART_RHR_RXCHR_Msk (0xffu << UART_RHR_RXCHR_Pos) |

| (UART_RHR) Received Character More... | |

| #define | UART_RHR_RXCHR_Pos 0 |

| #define | UART_SR_CLKREQ (0x1u << 22) |

| (UART_SR) Clock Request More... | |

| #define | UART_SR_CMP (0x1u << 15) |

| (UART_SR) Comparison Match More... | |

| #define | UART_SR_FRAME (0x1u << 6) |

| (UART_SR) Framing Error More... | |

| #define | UART_SR_OVRE (0x1u << 5) |

| (UART_SR) Overrun Error More... | |

| #define | UART_SR_PARE (0x1u << 7) |

| (UART_SR) Parity Error More... | |

| #define | UART_SR_RXRDY (0x1u << 0) |

| (UART_SR) Receiver Ready More... | |

| #define | UART_SR_SWES (0x1u << 21) |

| (UART_SR) SleepWalking Enable Status More... | |

| #define | UART_SR_TXEMPTY (0x1u << 9) |

| (UART_SR) Transmitter Empty More... | |

| #define | UART_SR_TXRDY (0x1u << 1) |

| (UART_SR) Transmitter Ready More... | |

| #define | UART_SR_WKUPREQ (0x1u << 23) |

| (UART_SR) Wake-Up Request More... | |

| #define | UART_THR_TXCHR(value) ((UART_THR_TXCHR_Msk & ((value) << UART_THR_TXCHR_Pos))) |

| #define | UART_THR_TXCHR_Msk (0xffu << UART_THR_TXCHR_Pos) |

| (UART_THR) Character to be Transmitted More... | |

| #define | UART_THR_TXCHR_Pos 0 |

| #define | UART_VERSION_MFN_Msk (0x7u << UART_VERSION_MFN_Pos) |

| (UART_VERSION) Metal Fix Number More... | |

| #define | UART_VERSION_MFN_Pos 16 |

| #define | UART_VERSION_VERSION_Msk (0xfffu << UART_VERSION_VERSION_Pos) |

| (UART_VERSION) Hardware Module Version More... | |

| #define | UART_VERSION_VERSION_Pos 0 |

| #define | UART_WPMR_WPEN (0x1u << 0) |

| (UART_WPMR) Write Protection Enable More... | |

| #define | UART_WPMR_WPKEY(value) ((UART_WPMR_WPKEY_Msk & ((value) << UART_WPMR_WPKEY_Pos))) |

| #define | UART_WPMR_WPKEY_Msk (0xffffffu << UART_WPMR_WPKEY_Pos) |

| (UART_WPMR) Write Protection Key More... | |

| #define | UART_WPMR_WPKEY_PASSWD (0x554152u << 8) |

| (UART_WPMR) Writing any other value in this field aborts the write operation.Always reads as 0. More... | |

| #define | UART_WPMR_WPKEY_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/uart.h.