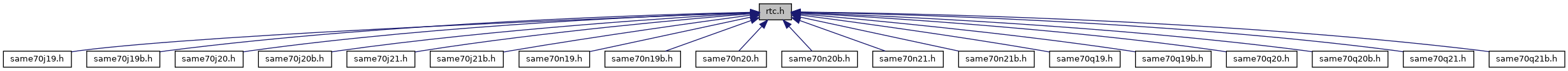

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Rtc |

| Rtc hardware registers. More... | |

Macros | |

| #define | RTC_CALALR_DATE(value) ((RTC_CALALR_DATE_Msk & ((value) << RTC_CALALR_DATE_Pos))) |

| #define | RTC_CALALR_DATE_Msk (0x3fu << RTC_CALALR_DATE_Pos) |

| (RTC_CALALR) Date Alarm More... | |

| #define | RTC_CALALR_DATE_Pos 24 |

| #define | RTC_CALALR_DATEEN (0x1u << 31) |

| (RTC_CALALR) Date Alarm Enable More... | |

| #define | RTC_CALALR_MONTH(value) ((RTC_CALALR_MONTH_Msk & ((value) << RTC_CALALR_MONTH_Pos))) |

| #define | RTC_CALALR_MONTH_Msk (0x1fu << RTC_CALALR_MONTH_Pos) |

| (RTC_CALALR) Month Alarm More... | |

| #define | RTC_CALALR_MONTH_Pos 16 |

| #define | RTC_CALALR_MTHEN (0x1u << 23) |

| (RTC_CALALR) Month Alarm Enable More... | |

| #define | RTC_CALR_CENT(value) ((RTC_CALR_CENT_Msk & ((value) << RTC_CALR_CENT_Pos))) |

| #define | RTC_CALR_CENT_Msk (0x7fu << RTC_CALR_CENT_Pos) |

| (RTC_CALR) Current Century More... | |

| #define | RTC_CALR_CENT_Pos 0 |

| #define | RTC_CALR_DATE(value) ((RTC_CALR_DATE_Msk & ((value) << RTC_CALR_DATE_Pos))) |

| #define | RTC_CALR_DATE_Msk (0x3fu << RTC_CALR_DATE_Pos) |

| (RTC_CALR) Current Day in Current Month More... | |

| #define | RTC_CALR_DATE_Pos 24 |

| #define | RTC_CALR_DAY(value) ((RTC_CALR_DAY_Msk & ((value) << RTC_CALR_DAY_Pos))) |

| #define | RTC_CALR_DAY_Msk (0x7u << RTC_CALR_DAY_Pos) |

| (RTC_CALR) Current Day in Current Week More... | |

| #define | RTC_CALR_DAY_Pos 21 |

| #define | RTC_CALR_MONTH(value) ((RTC_CALR_MONTH_Msk & ((value) << RTC_CALR_MONTH_Pos))) |

| #define | RTC_CALR_MONTH_Msk (0x1fu << RTC_CALR_MONTH_Pos) |

| (RTC_CALR) Current Month More... | |

| #define | RTC_CALR_MONTH_Pos 16 |

| #define | RTC_CALR_YEAR(value) ((RTC_CALR_YEAR_Msk & ((value) << RTC_CALR_YEAR_Pos))) |

| #define | RTC_CALR_YEAR_Msk (0xffu << RTC_CALR_YEAR_Pos) |

| (RTC_CALR) Current Year More... | |

| #define | RTC_CALR_YEAR_Pos 8 |

| #define | RTC_CR_CALEVSEL(value) ((RTC_CR_CALEVSEL_Msk & ((value) << RTC_CR_CALEVSEL_Pos))) |

| #define | RTC_CR_CALEVSEL_MONTH (0x1u << 16) |

| (RTC_CR) Month change (every 01 of each month at time 00:00:00) More... | |

| #define | RTC_CR_CALEVSEL_Msk (0x3u << RTC_CR_CALEVSEL_Pos) |

| (RTC_CR) Calendar Event Selection More... | |

| #define | RTC_CR_CALEVSEL_Pos 16 |

| #define | RTC_CR_CALEVSEL_WEEK (0x0u << 16) |

| (RTC_CR) Week change (every Monday at time 00:00:00) More... | |

| #define | RTC_CR_CALEVSEL_YEAR (0x2u << 16) |

| (RTC_CR) Year change (every January 1 at time 00:00:00) More... | |

| #define | RTC_CR_TIMEVSEL(value) ((RTC_CR_TIMEVSEL_Msk & ((value) << RTC_CR_TIMEVSEL_Pos))) |

| #define | RTC_CR_TIMEVSEL_HOUR (0x1u << 8) |

| (RTC_CR) Hour change More... | |

| #define | RTC_CR_TIMEVSEL_MIDNIGHT (0x2u << 8) |

| (RTC_CR) Every day at midnight More... | |

| #define | RTC_CR_TIMEVSEL_MINUTE (0x0u << 8) |

| (RTC_CR) Minute change More... | |

| #define | RTC_CR_TIMEVSEL_Msk (0x3u << RTC_CR_TIMEVSEL_Pos) |

| (RTC_CR) Time Event Selection More... | |

| #define | RTC_CR_TIMEVSEL_NOON (0x3u << 8) |

| (RTC_CR) Every day at noon More... | |

| #define | RTC_CR_TIMEVSEL_Pos 8 |

| #define | RTC_CR_UPDCAL (0x1u << 1) |

| (RTC_CR) Update Request Calendar Register More... | |

| #define | RTC_CR_UPDTIM (0x1u << 0) |

| (RTC_CR) Update Request Time Register More... | |

| #define | RTC_IDR_ACKDIS (0x1u << 0) |

| (RTC_IDR) Acknowledge Update Interrupt Disable More... | |

| #define | RTC_IDR_ALRDIS (0x1u << 1) |

| (RTC_IDR) Alarm Interrupt Disable More... | |

| #define | RTC_IDR_CALDIS (0x1u << 4) |

| (RTC_IDR) Calendar Event Interrupt Disable More... | |

| #define | RTC_IDR_SECDIS (0x1u << 2) |

| (RTC_IDR) Second Event Interrupt Disable More... | |

| #define | RTC_IDR_TDERRDIS (0x1u << 5) |

| (RTC_IDR) Time and/or Date Error Interrupt Disable More... | |

| #define | RTC_IDR_TIMDIS (0x1u << 3) |

| (RTC_IDR) Time Event Interrupt Disable More... | |

| #define | RTC_IER_ACKEN (0x1u << 0) |

| (RTC_IER) Acknowledge Update Interrupt Enable More... | |

| #define | RTC_IER_ALREN (0x1u << 1) |

| (RTC_IER) Alarm Interrupt Enable More... | |

| #define | RTC_IER_CALEN (0x1u << 4) |

| (RTC_IER) Calendar Event Interrupt Enable More... | |

| #define | RTC_IER_SECEN (0x1u << 2) |

| (RTC_IER) Second Event Interrupt Enable More... | |

| #define | RTC_IER_TDERREN (0x1u << 5) |

| (RTC_IER) Time and/or Date Error Interrupt Enable More... | |

| #define | RTC_IER_TIMEN (0x1u << 3) |

| (RTC_IER) Time Event Interrupt Enable More... | |

| #define | RTC_IMR_ACK (0x1u << 0) |

| (RTC_IMR) Acknowledge Update Interrupt Mask More... | |

| #define | RTC_IMR_ALR (0x1u << 1) |

| (RTC_IMR) Alarm Interrupt Mask More... | |

| #define | RTC_IMR_CAL (0x1u << 4) |

| (RTC_IMR) Calendar Event Interrupt Mask More... | |

| #define | RTC_IMR_SEC (0x1u << 2) |

| (RTC_IMR) Second Event Interrupt Mask More... | |

| #define | RTC_IMR_TDERR (0x1u << 5) |

| (RTC_IMR) Time and/or Date Error Mask More... | |

| #define | RTC_IMR_TIM (0x1u << 3) |

| (RTC_IMR) Time Event Interrupt Mask More... | |

| #define | RTC_MR_CORRECTION(value) ((RTC_MR_CORRECTION_Msk & ((value) << RTC_MR_CORRECTION_Pos))) |

| #define | RTC_MR_CORRECTION_Msk (0x7fu << RTC_MR_CORRECTION_Pos) |

| (RTC_MR) Slow Clock Correction More... | |

| #define | RTC_MR_CORRECTION_Pos 8 |

| #define | RTC_MR_HIGHPPM (0x1u << 15) |

| (RTC_MR) HIGH PPM Correction More... | |

| #define | RTC_MR_HRMOD (0x1u << 0) |

| (RTC_MR) 12-/24-hour Mode More... | |

| #define | RTC_MR_NEGPPM (0x1u << 4) |

| (RTC_MR) NEGative PPM Correction More... | |

| #define | RTC_MR_OUT0(value) ((RTC_MR_OUT0_Msk & ((value) << RTC_MR_OUT0_Pos))) |

| #define | RTC_MR_OUT0_ALARM_FLAG (0x6u << 16) |

| (RTC_MR) Output is a copy of the alarm flag More... | |

| #define | RTC_MR_OUT0_ALARM_TOGGLE (0x5u << 16) |

| (RTC_MR) Output toggles when alarm flag rises More... | |

| #define | RTC_MR_OUT0_FREQ1HZ (0x1u << 16) |

| (RTC_MR) 1 Hz square wave More... | |

| #define | RTC_MR_OUT0_FREQ32HZ (0x2u << 16) |

| (RTC_MR) 32 Hz square wave More... | |

| #define | RTC_MR_OUT0_FREQ512HZ (0x4u << 16) |

| (RTC_MR) 512 Hz square wave More... | |

| #define | RTC_MR_OUT0_FREQ64HZ (0x3u << 16) |

| (RTC_MR) 64 Hz square wave More... | |

| #define | RTC_MR_OUT0_Msk (0x7u << RTC_MR_OUT0_Pos) |

| (RTC_MR) RTCOUT0 OutputSource Selection More... | |

| #define | RTC_MR_OUT0_NO_WAVE (0x0u << 16) |

| (RTC_MR) No waveform, stuck at '0' More... | |

| #define | RTC_MR_OUT0_Pos 16 |

| #define | RTC_MR_OUT0_PROG_PULSE (0x7u << 16) |

| (RTC_MR) Duty cycle programmable pulse More... | |

| #define | RTC_MR_OUT1(value) ((RTC_MR_OUT1_Msk & ((value) << RTC_MR_OUT1_Pos))) |

| #define | RTC_MR_OUT1_ALARM_FLAG (0x6u << 20) |

| (RTC_MR) Output is a copy of the alarm flag More... | |

| #define | RTC_MR_OUT1_ALARM_TOGGLE (0x5u << 20) |

| (RTC_MR) Output toggles when alarm flag rises More... | |

| #define | RTC_MR_OUT1_FREQ1HZ (0x1u << 20) |

| (RTC_MR) 1 Hz square wave More... | |

| #define | RTC_MR_OUT1_FREQ32HZ (0x2u << 20) |

| (RTC_MR) 32 Hz square wave More... | |

| #define | RTC_MR_OUT1_FREQ512HZ (0x4u << 20) |

| (RTC_MR) 512 Hz square wave More... | |

| #define | RTC_MR_OUT1_FREQ64HZ (0x3u << 20) |

| (RTC_MR) 64 Hz square wave More... | |

| #define | RTC_MR_OUT1_Msk (0x7u << RTC_MR_OUT1_Pos) |

| (RTC_MR) RTCOUT1 Output Source Selection More... | |

| #define | RTC_MR_OUT1_NO_WAVE (0x0u << 20) |

| (RTC_MR) No waveform, stuck at '0' More... | |

| #define | RTC_MR_OUT1_Pos 20 |

| #define | RTC_MR_OUT1_PROG_PULSE (0x7u << 20) |

| (RTC_MR) Duty cycle programmable pulse More... | |

| #define | RTC_MR_PERSIAN (0x1u << 1) |

| (RTC_MR) PERSIAN Calendar More... | |

| #define | RTC_MR_THIGH(value) ((RTC_MR_THIGH_Msk & ((value) << RTC_MR_THIGH_Pos))) |

| #define | RTC_MR_THIGH_H_122US (0x5u << 24) |

| (RTC_MR) 122 us More... | |

| #define | RTC_MR_THIGH_H_15US (0x7u << 24) |

| (RTC_MR) 15.2 us More... | |

| #define | RTC_MR_THIGH_H_16MS (0x1u << 24) |

| (RTC_MR) 15.6 ms More... | |

| #define | RTC_MR_THIGH_H_30US (0x6u << 24) |

| (RTC_MR) 30.5 us More... | |

| #define | RTC_MR_THIGH_H_31MS (0x0u << 24) |

| (RTC_MR) 31.2 ms More... | |

| #define | RTC_MR_THIGH_H_488US (0x4u << 24) |

| (RTC_MR) 488 us More... | |

| #define | RTC_MR_THIGH_H_4MS (0x2u << 24) |

| (RTC_MR) 3.91 ms More... | |

| #define | RTC_MR_THIGH_H_976US (0x3u << 24) |

| (RTC_MR) 976 us More... | |

| #define | RTC_MR_THIGH_Msk (0x7u << RTC_MR_THIGH_Pos) |

| (RTC_MR) High Duration of the Output Pulse More... | |

| #define | RTC_MR_THIGH_Pos 24 |

| #define | RTC_MR_TPERIOD(value) ((RTC_MR_TPERIOD_Msk & ((value) << RTC_MR_TPERIOD_Pos))) |

| #define | RTC_MR_TPERIOD_Msk (0x3u << RTC_MR_TPERIOD_Pos) |

| (RTC_MR) Period of the Output Pulse More... | |

| #define | RTC_MR_TPERIOD_P_125MS (0x3u << 28) |

| (RTC_MR) 125 ms More... | |

| #define | RTC_MR_TPERIOD_P_1S (0x0u << 28) |

| (RTC_MR) 1 second More... | |

| #define | RTC_MR_TPERIOD_P_250MS (0x2u << 28) |

| (RTC_MR) 250 ms More... | |

| #define | RTC_MR_TPERIOD_P_500MS (0x1u << 28) |

| (RTC_MR) 500 ms More... | |

| #define | RTC_MR_TPERIOD_Pos 28 |

| #define | RTC_SCCR_ACKCLR (0x1u << 0) |

| (RTC_SCCR) Acknowledge Clear More... | |

| #define | RTC_SCCR_ALRCLR (0x1u << 1) |

| (RTC_SCCR) Alarm Clear More... | |

| #define | RTC_SCCR_CALCLR (0x1u << 4) |

| (RTC_SCCR) Calendar Clear More... | |

| #define | RTC_SCCR_SECCLR (0x1u << 2) |

| (RTC_SCCR) Second Clear More... | |

| #define | RTC_SCCR_TDERRCLR (0x1u << 5) |

| (RTC_SCCR) Time and/or Date Free Running Error Clear More... | |

| #define | RTC_SCCR_TIMCLR (0x1u << 3) |

| (RTC_SCCR) Time Clear More... | |

| #define | RTC_SR_ACKUPD (0x1u << 0) |

| (RTC_SR) Acknowledge for Update More... | |

| #define | RTC_SR_ACKUPD_FREERUN (0x0u << 0) |

| (RTC_SR) Time and calendar registers cannot be updated. More... | |

| #define | RTC_SR_ACKUPD_UPDATE (0x1u << 0) |

| (RTC_SR) Time and calendar registers can be updated. More... | |

| #define | RTC_SR_ALARM (0x1u << 1) |

| (RTC_SR) Alarm Flag More... | |

| #define | RTC_SR_ALARM_ALARMEVENT (0x1u << 1) |

| (RTC_SR) An alarm matching condition has occurred. More... | |

| #define | RTC_SR_ALARM_NO_ALARMEVENT (0x0u << 1) |

| (RTC_SR) No alarm matching condition occurred. More... | |

| #define | RTC_SR_CALEV (0x1u << 4) |

| (RTC_SR) Calendar Event More... | |

| #define | RTC_SR_CALEV_CALEVENT (0x1u << 4) |

| (RTC_SR) At least one calendar event has occurred since the last clear. More... | |

| #define | RTC_SR_CALEV_NO_CALEVENT (0x0u << 4) |

| (RTC_SR) No calendar event has occurred since the last clear. More... | |

| #define | RTC_SR_SEC (0x1u << 2) |

| (RTC_SR) Second Event More... | |

| #define | RTC_SR_SEC_NO_SECEVENT (0x0u << 2) |

| (RTC_SR) No second event has occurred since the last clear. More... | |

| #define | RTC_SR_SEC_SECEVENT (0x1u << 2) |

| (RTC_SR) At least one second event has occurred since the last clear. More... | |

| #define | RTC_SR_TDERR (0x1u << 5) |

| (RTC_SR) Time and/or Date Free Running Error More... | |

| #define | RTC_SR_TDERR_CORRECT (0x0u << 5) |

| (RTC_SR) The internal free running counters are carrying valid values since the last read of the Status Register (RTC_SR). More... | |

| #define | RTC_SR_TDERR_ERR_TIMEDATE (0x1u << 5) |

| (RTC_SR) The internal free running counters have been corrupted (invalid date or time, non-BCD values) since the last read and/or they are still invalid. More... | |

| #define | RTC_SR_TIMEV (0x1u << 3) |

| (RTC_SR) Time Event More... | |

| #define | RTC_SR_TIMEV_NO_TIMEVENT (0x0u << 3) |

| (RTC_SR) No time event has occurred since the last clear. More... | |

| #define | RTC_SR_TIMEV_TIMEVENT (0x1u << 3) |

| (RTC_SR) At least one time event has occurred since the last clear. More... | |

| #define | RTC_TIMALR_AMPM (0x1u << 22) |

| (RTC_TIMALR) AM/PM Indicator More... | |

| #define | RTC_TIMALR_HOUR(value) ((RTC_TIMALR_HOUR_Msk & ((value) << RTC_TIMALR_HOUR_Pos))) |

| #define | RTC_TIMALR_HOUR_Msk (0x3fu << RTC_TIMALR_HOUR_Pos) |

| (RTC_TIMALR) Hour Alarm More... | |

| #define | RTC_TIMALR_HOUR_Pos 16 |

| #define | RTC_TIMALR_HOUREN (0x1u << 23) |

| (RTC_TIMALR) Hour Alarm Enable More... | |

| #define | RTC_TIMALR_MIN(value) ((RTC_TIMALR_MIN_Msk & ((value) << RTC_TIMALR_MIN_Pos))) |

| #define | RTC_TIMALR_MIN_Msk (0x7fu << RTC_TIMALR_MIN_Pos) |

| (RTC_TIMALR) Minute Alarm More... | |

| #define | RTC_TIMALR_MIN_Pos 8 |

| #define | RTC_TIMALR_MINEN (0x1u << 15) |

| (RTC_TIMALR) Minute Alarm Enable More... | |

| #define | RTC_TIMALR_SEC(value) ((RTC_TIMALR_SEC_Msk & ((value) << RTC_TIMALR_SEC_Pos))) |

| #define | RTC_TIMALR_SEC_Msk (0x7fu << RTC_TIMALR_SEC_Pos) |

| (RTC_TIMALR) Second Alarm More... | |

| #define | RTC_TIMALR_SEC_Pos 0 |

| #define | RTC_TIMALR_SECEN (0x1u << 7) |

| (RTC_TIMALR) Second Alarm Enable More... | |

| #define | RTC_TIMR_AMPM (0x1u << 22) |

| (RTC_TIMR) Ante Meridiem Post Meridiem Indicator More... | |

| #define | RTC_TIMR_HOUR(value) ((RTC_TIMR_HOUR_Msk & ((value) << RTC_TIMR_HOUR_Pos))) |

| #define | RTC_TIMR_HOUR_Msk (0x3fu << RTC_TIMR_HOUR_Pos) |

| (RTC_TIMR) Current Hour More... | |

| #define | RTC_TIMR_HOUR_Pos 16 |

| #define | RTC_TIMR_MIN(value) ((RTC_TIMR_MIN_Msk & ((value) << RTC_TIMR_MIN_Pos))) |

| #define | RTC_TIMR_MIN_Msk (0x7fu << RTC_TIMR_MIN_Pos) |

| (RTC_TIMR) Current Minute More... | |

| #define | RTC_TIMR_MIN_Pos 8 |

| #define | RTC_TIMR_SEC(value) ((RTC_TIMR_SEC_Msk & ((value) << RTC_TIMR_SEC_Pos))) |

| #define | RTC_TIMR_SEC_Msk (0x7fu << RTC_TIMR_SEC_Pos) |

| (RTC_TIMR) Current Second More... | |

| #define | RTC_TIMR_SEC_Pos 0 |

| #define | RTC_VER_NVCAL (0x1u << 1) |

| (RTC_VER) Non-valid Calendar More... | |

| #define | RTC_VER_NVCALALR (0x1u << 3) |

| (RTC_VER) Non-valid Calendar Alarm More... | |

| #define | RTC_VER_NVTIM (0x1u << 0) |

| (RTC_VER) Non-valid Time More... | |

| #define | RTC_VER_NVTIMALR (0x1u << 2) |

| (RTC_VER) Non-valid Time Alarm More... | |

| #define | RTC_VERSION_MFN_Msk (0x7u << RTC_VERSION_MFN_Pos) |

| (RTC_VERSION) Metal Fix Number More... | |

| #define | RTC_VERSION_MFN_Pos 16 |

| #define | RTC_VERSION_VERSION_Msk (0xfffu << RTC_VERSION_VERSION_Pos) |

| (RTC_VERSION) Version of the Hardware Module More... | |

| #define | RTC_VERSION_VERSION_Pos 0 |

| #define | RTC_WPMR_WPEN (0x1u << 0) |

| (RTC_WPMR) Write Protection Enable More... | |

| #define | RTC_WPMR_WPKEY(value) ((RTC_WPMR_WPKEY_Msk & ((value) << RTC_WPMR_WPKEY_Pos))) |

| #define | RTC_WPMR_WPKEY_Msk (0xffffffu << RTC_WPMR_WPKEY_Pos) |

| (RTC_WPMR) Write Protection Key More... | |

| #define | RTC_WPMR_WPKEY_PASSWD (0x525443u << 8) |

| (RTC_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | RTC_WPMR_WPKEY_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/rtc.h.