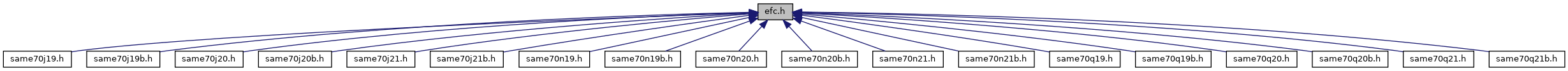

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Efc |

| Efc hardware registers. More... | |

Macros | |

| #define | EEFC_FCR_FARG(value) ((EEFC_FCR_FARG_Msk & ((value) << EEFC_FCR_FARG_Pos))) |

| #define | EEFC_FCR_FARG_Msk (0xffffu << EEFC_FCR_FARG_Pos) |

| (EEFC_FCR) Flash Command Argument More... | |

| #define | EEFC_FCR_FARG_Pos 8 |

| #define | EEFC_FCR_FCMD(value) ((EEFC_FCR_FCMD_Msk & ((value) << EEFC_FCR_FCMD_Pos))) |

| #define | EEFC_FCR_FCMD_CGPB (0xCu << 0) |

| (EEFC_FCR) Clear GPNVM bit More... | |

| #define | EEFC_FCR_FCMD_CLB (0x9u << 0) |

| (EEFC_FCR) Clear lock bit More... | |

| #define | EEFC_FCR_FCMD_EA (0x5u << 0) |

| (EEFC_FCR) Erase all More... | |

| #define | EEFC_FCR_FCMD_EPA (0x7u << 0) |

| (EEFC_FCR) Erase pages More... | |

| #define | EEFC_FCR_FCMD_ES (0x11u << 0) |

| (EEFC_FCR) Erase sector More... | |

| #define | EEFC_FCR_FCMD_EUS (0x13u << 0) |

| (EEFC_FCR) Erase user signature More... | |

| #define | EEFC_FCR_FCMD_EWP (0x3u << 0) |

| (EEFC_FCR) Erase page and write page More... | |

| #define | EEFC_FCR_FCMD_EWPL (0x4u << 0) |

| (EEFC_FCR) Erase page and write page then lock More... | |

| #define | EEFC_FCR_FCMD_GCALB (0x10u << 0) |

| (EEFC_FCR) Get CALIB bit More... | |

| #define | EEFC_FCR_FCMD_GETD (0x0u << 0) |

| (EEFC_FCR) Get Flash descriptor More... | |

| #define | EEFC_FCR_FCMD_GGPB (0xDu << 0) |

| (EEFC_FCR) Get GPNVM bit More... | |

| #define | EEFC_FCR_FCMD_GLB (0xAu << 0) |

| (EEFC_FCR) Get lock bit More... | |

| #define | EEFC_FCR_FCMD_Msk (0xffu << EEFC_FCR_FCMD_Pos) |

| (EEFC_FCR) Flash Command More... | |

| #define | EEFC_FCR_FCMD_Pos 0 |

| #define | EEFC_FCR_FCMD_SGPB (0xBu << 0) |

| (EEFC_FCR) Set GPNVM bit More... | |

| #define | EEFC_FCR_FCMD_SLB (0x8u << 0) |

| (EEFC_FCR) Set lock bit More... | |

| #define | EEFC_FCR_FCMD_SPUI (0xFu << 0) |

| (EEFC_FCR) Stop read unique identifier More... | |

| #define | EEFC_FCR_FCMD_SPUS (0x15u << 0) |

| (EEFC_FCR) Stop read user signature More... | |

| #define | EEFC_FCR_FCMD_STUI (0xEu << 0) |

| (EEFC_FCR) Start read unique identifier More... | |

| #define | EEFC_FCR_FCMD_STUS (0x14u << 0) |

| (EEFC_FCR) Start read user signature More... | |

| #define | EEFC_FCR_FCMD_WP (0x1u << 0) |

| (EEFC_FCR) Write page More... | |

| #define | EEFC_FCR_FCMD_WPL (0x2u << 0) |

| (EEFC_FCR) Write page and lock More... | |

| #define | EEFC_FCR_FCMD_WUS (0x12u << 0) |

| (EEFC_FCR) Write user signature More... | |

| #define | EEFC_FCR_FKEY(value) ((EEFC_FCR_FKEY_Msk & ((value) << EEFC_FCR_FKEY_Pos))) |

| #define | EEFC_FCR_FKEY_Msk (0xffu << EEFC_FCR_FKEY_Pos) |

| (EEFC_FCR) Flash Writing Protection Key More... | |

| #define | EEFC_FCR_FKEY_PASSWD (0x5Au << 24) |

| (EEFC_FCR) The 0x5A value enables the command defined by the bits of the register. If the field is written with a different value, the write is not performed and no action is started. More... | |

| #define | EEFC_FCR_FKEY_Pos 24 |

| #define | EEFC_FMR_CLOE (0x1u << 26) |

| (EEFC_FMR) Code Loop Optimization Enable More... | |

| #define | EEFC_FMR_FRDY (0x1u << 0) |

| (EEFC_FMR) Flash Ready Interrupt Enable More... | |

| #define | EEFC_FMR_FWS(value) ((EEFC_FMR_FWS_Msk & ((value) << EEFC_FMR_FWS_Pos))) |

| #define | EEFC_FMR_FWS_Msk (0xfu << EEFC_FMR_FWS_Pos) |

| (EEFC_FMR) Flash Wait State More... | |

| #define | EEFC_FMR_FWS_Pos 8 |

| #define | EEFC_FMR_SCOD (0x1u << 16) |

| (EEFC_FMR) Sequential Code Optimization Disable More... | |

| #define | EEFC_FRR_FVALUE_Msk (0xffffffffu << EEFC_FRR_FVALUE_Pos) |

| (EEFC_FRR) Flash Result Value More... | |

| #define | EEFC_FRR_FVALUE_Pos 0 |

| #define | EEFC_FSR_FCMDE (0x1u << 1) |

| (EEFC_FSR) Flash Command Error Status (cleared on read or by writing EEFC_FCR) More... | |

| #define | EEFC_FSR_FLERR (0x1u << 3) |

| (EEFC_FSR) Flash Error Status (cleared when a programming operation starts) More... | |

| #define | EEFC_FSR_FLOCKE (0x1u << 2) |

| (EEFC_FSR) Flash Lock Error Status (cleared on read) More... | |

| #define | EEFC_FSR_FRDY (0x1u << 0) |

| (EEFC_FSR) Flash Ready Status (cleared when Flash is busy) More... | |

| #define | EEFC_FSR_MECCELSB (0x1u << 17) |

| (EEFC_FSR) Multiple ECC Error on LSB Part of the Memory Flash Data Bus (cleared on read) More... | |

| #define | EEFC_FSR_MECCEMSB (0x1u << 19) |

| (EEFC_FSR) Multiple ECC Error on MSB Part of the Memory Flash Data Bus (cleared on read) More... | |

| #define | EEFC_FSR_UECCELSB (0x1u << 16) |

| (EEFC_FSR) Unique ECC Error on LSB Part of the Memory Flash Data Bus (cleared on read) More... | |

| #define | EEFC_FSR_UECCEMSB (0x1u << 18) |

| (EEFC_FSR) Unique ECC Error on MSB Part of the Memory Flash Data Bus (cleared on read) More... | |

| #define | EEFC_VERSION_MFN_Msk (0x7u << EEFC_VERSION_MFN_Pos) |

| (EEFC_VERSION) Metal Fix Number More... | |

| #define | EEFC_VERSION_MFN_Pos 16 |

| #define | EEFC_VERSION_VERSION_Msk (0xfffu << EEFC_VERSION_VERSION_Pos) |

| (EEFC_VERSION) Version of the Hardware Module More... | |

| #define | EEFC_VERSION_VERSION_Pos 0 |

| #define | EEFC_WPMR_WPEN (0x1u << 0) |

| (EEFC_WPMR) Write Protection Enable More... | |

| #define | EEFC_WPMR_WPKEY(value) ((EEFC_WPMR_WPKEY_Msk & ((value) << EEFC_WPMR_WPKEY_Pos))) |

| #define | EEFC_WPMR_WPKEY_Msk (0xffffffu << EEFC_WPMR_WPKEY_Pos) |

| (EEFC_WPMR) Write Protection Key More... | |

| #define | EEFC_WPMR_WPKEY_PASSWD (0x454643u << 8) |

| (EEFC_WPMR) Writing any other value in this field aborts the write operation.Always reads as 0. More... | |

| #define | EEFC_WPMR_WPKEY_Pos 8 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file utils/cmsis/same70/include/component/efc.h.