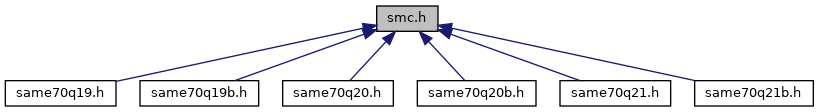

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Smc |

| struct | SmcCs_number |

| SmcCs_number hardware registers. More... | |

Macros | |

| #define | SMC_CYCLE_NRD_CYCLE(value) ((SMC_CYCLE_NRD_CYCLE_Msk & ((value) << SMC_CYCLE_NRD_CYCLE_Pos))) |

| #define | SMC_CYCLE_NRD_CYCLE_Msk (0x1ffu << SMC_CYCLE_NRD_CYCLE_Pos) |

| (SMC_CYCLE) Total Read Cycle Length More... | |

| #define | SMC_CYCLE_NRD_CYCLE_Pos 16 |

| #define | SMC_CYCLE_NWE_CYCLE(value) ((SMC_CYCLE_NWE_CYCLE_Msk & ((value) << SMC_CYCLE_NWE_CYCLE_Pos))) |

| #define | SMC_CYCLE_NWE_CYCLE_Msk (0x1ffu << SMC_CYCLE_NWE_CYCLE_Pos) |

| (SMC_CYCLE) Total Write Cycle Length More... | |

| #define | SMC_CYCLE_NWE_CYCLE_Pos 0 |

| #define | SMC_KEY1_KEY1(value) ((SMC_KEY1_KEY1_Msk & ((value) << SMC_KEY1_KEY1_Pos))) |

| #define | SMC_KEY1_KEY1_Msk (0xffffffffu << SMC_KEY1_KEY1_Pos) |

| (SMC_KEY1) Off-Chip Memory Scrambling (OCMS) Key Part 1 More... | |

| #define | SMC_KEY1_KEY1_Pos 0 |

| #define | SMC_KEY2_KEY2(value) ((SMC_KEY2_KEY2_Msk & ((value) << SMC_KEY2_KEY2_Pos))) |

| #define | SMC_KEY2_KEY2_Msk (0xffffffffu << SMC_KEY2_KEY2_Pos) |

| (SMC_KEY2) Off-Chip Memory Scrambling (OCMS) Key Part 2 More... | |

| #define | SMC_KEY2_KEY2_Pos 0 |

| #define | SMC_MODE_BAT (0x1u << 8) |

| (SMC_MODE) Byte Access Type More... | |

| #define | SMC_MODE_BAT_BYTE_SELECT (0x0u << 8) |

| (SMC_MODE) Byte select access type:- Write operation is controlled using NCS, NWE, NBS0, NBS1.- Read operation is controlled using NCS, NRD, NBS0, NBS1. More... | |

| #define | SMC_MODE_BAT_BYTE_WRITE (0x1u << 8) |

| (SMC_MODE) Byte write access type:- Write operation is controlled using NCS, NWR0, NWR1.- Read operation is controlled using NCS and NRD. More... | |

| #define | SMC_MODE_DBW (0x1u << 12) |

| (SMC_MODE) Data Bus Width More... | |

| #define | SMC_MODE_DBW_16_BIT (0x1u << 12) |

| (SMC_MODE) 16-bit Data Bus More... | |

| #define | SMC_MODE_DBW_8_BIT (0x0u << 12) |

| (SMC_MODE) 8-bit Data Bus More... | |

| #define | SMC_MODE_EXNW_MODE(value) ((SMC_MODE_EXNW_MODE_Msk & ((value) << SMC_MODE_EXNW_MODE_Pos))) |

| #define | SMC_MODE_EXNW_MODE_DISABLED (0x0u << 4) |

| (SMC_MODE) Disabled-The NWAIT input signal is ignored on the corresponding chip select. More... | |

| #define | SMC_MODE_EXNW_MODE_FROZEN (0x2u << 4) |

| (SMC_MODE) Frozen Mode-If asserted, the NWAIT signal freezes the current read or write cycle. After deassertion, the read/write cycle is resumed from the point where it was stopped. More... | |

| #define | SMC_MODE_EXNW_MODE_Msk (0x3u << SMC_MODE_EXNW_MODE_Pos) |

| (SMC_MODE) NWAIT Mode More... | |

| #define | SMC_MODE_EXNW_MODE_Pos 4 |

| #define | SMC_MODE_EXNW_MODE_READY (0x3u << 4) |

| (SMC_MODE) Ready Mode-The NWAIT signal indicates the availability of the external device at the end of the pulse of the controlling read or write signal, to complete the access. If high, the access normally completes. If low, the access is extended until NWAIT returns high. More... | |

| #define | SMC_MODE_PMEN (0x1u << 24) |

| (SMC_MODE) Page Mode Enabled More... | |

| #define | SMC_MODE_PS(value) ((SMC_MODE_PS_Msk & ((value) << SMC_MODE_PS_Pos))) |

| #define | SMC_MODE_PS_16_BYTE (0x2u << 28) |

| (SMC_MODE) 16-byte page More... | |

| #define | SMC_MODE_PS_32_BYTE (0x3u << 28) |

| (SMC_MODE) 32-byte page More... | |

| #define | SMC_MODE_PS_4_BYTE (0x0u << 28) |

| (SMC_MODE) 4-byte page More... | |

| #define | SMC_MODE_PS_8_BYTE (0x1u << 28) |

| (SMC_MODE) 8-byte page More... | |

| #define | SMC_MODE_PS_Msk (0x3u << SMC_MODE_PS_Pos) |

| (SMC_MODE) Page Size More... | |

| #define | SMC_MODE_PS_Pos 28 |

| #define | SMC_MODE_READ_MODE (0x1u << 0) |

| (SMC_MODE) Read Mode More... | |

| #define | SMC_MODE_TDF_CYCLES(value) ((SMC_MODE_TDF_CYCLES_Msk & ((value) << SMC_MODE_TDF_CYCLES_Pos))) |

| #define | SMC_MODE_TDF_CYCLES_Msk (0xfu << SMC_MODE_TDF_CYCLES_Pos) |

| (SMC_MODE) Data Float Time More... | |

| #define | SMC_MODE_TDF_CYCLES_Pos 16 |

| #define | SMC_MODE_TDF_MODE (0x1u << 20) |

| (SMC_MODE) TDF Optimization More... | |

| #define | SMC_MODE_WRITE_MODE (0x1u << 1) |

| (SMC_MODE) Write Mode More... | |

| #define | SMC_OCMS_CS0SE (0x1u << 8) |

| (SMC_OCMS) Chip Select (x = 0 to 3) Scrambling Enable More... | |

| #define | SMC_OCMS_CS1SE (0x1u << 9) |

| (SMC_OCMS) Chip Select (x = 0 to 3) Scrambling Enable More... | |

| #define | SMC_OCMS_CS2SE (0x1u << 10) |

| (SMC_OCMS) Chip Select (x = 0 to 3) Scrambling Enable More... | |

| #define | SMC_OCMS_CS3SE (0x1u << 11) |

| (SMC_OCMS) Chip Select (x = 0 to 3) Scrambling Enable More... | |

| #define | SMC_OCMS_SMSE (0x1u << 0) |

| (SMC_OCMS) Static Memory Controller Scrambling Enable More... | |

| #define | SMC_PULSE_NCS_RD_PULSE(value) ((SMC_PULSE_NCS_RD_PULSE_Msk & ((value) << SMC_PULSE_NCS_RD_PULSE_Pos))) |

| #define | SMC_PULSE_NCS_RD_PULSE_Msk (0x7fu << SMC_PULSE_NCS_RD_PULSE_Pos) |

| (SMC_PULSE) NCS Pulse Length in READ Access More... | |

| #define | SMC_PULSE_NCS_RD_PULSE_Pos 24 |

| #define | SMC_PULSE_NCS_WR_PULSE(value) ((SMC_PULSE_NCS_WR_PULSE_Msk & ((value) << SMC_PULSE_NCS_WR_PULSE_Pos))) |

| #define | SMC_PULSE_NCS_WR_PULSE_Msk (0x7fu << SMC_PULSE_NCS_WR_PULSE_Pos) |

| (SMC_PULSE) NCS Pulse Length in WRITE Access More... | |

| #define | SMC_PULSE_NCS_WR_PULSE_Pos 8 |

| #define | SMC_PULSE_NRD_PULSE(value) ((SMC_PULSE_NRD_PULSE_Msk & ((value) << SMC_PULSE_NRD_PULSE_Pos))) |

| #define | SMC_PULSE_NRD_PULSE_Msk (0x7fu << SMC_PULSE_NRD_PULSE_Pos) |

| (SMC_PULSE) NRD Pulse Length More... | |

| #define | SMC_PULSE_NRD_PULSE_Pos 16 |

| #define | SMC_PULSE_NWE_PULSE(value) ((SMC_PULSE_NWE_PULSE_Msk & ((value) << SMC_PULSE_NWE_PULSE_Pos))) |

| #define | SMC_PULSE_NWE_PULSE_Msk (0x7fu << SMC_PULSE_NWE_PULSE_Pos) |

| (SMC_PULSE) NWE Pulse Length More... | |

| #define | SMC_PULSE_NWE_PULSE_Pos 0 |

| #define | SMC_SETUP_NCS_RD_SETUP(value) ((SMC_SETUP_NCS_RD_SETUP_Msk & ((value) << SMC_SETUP_NCS_RD_SETUP_Pos))) |

| #define | SMC_SETUP_NCS_RD_SETUP_Msk (0x3fu << SMC_SETUP_NCS_RD_SETUP_Pos) |

| (SMC_SETUP) NCS Setup Length in READ Access More... | |

| #define | SMC_SETUP_NCS_RD_SETUP_Pos 24 |

| #define | SMC_SETUP_NCS_WR_SETUP(value) ((SMC_SETUP_NCS_WR_SETUP_Msk & ((value) << SMC_SETUP_NCS_WR_SETUP_Pos))) |

| #define | SMC_SETUP_NCS_WR_SETUP_Msk (0x3fu << SMC_SETUP_NCS_WR_SETUP_Pos) |

| (SMC_SETUP) NCS Setup Length in WRITE Access More... | |

| #define | SMC_SETUP_NCS_WR_SETUP_Pos 8 |

| #define | SMC_SETUP_NRD_SETUP(value) ((SMC_SETUP_NRD_SETUP_Msk & ((value) << SMC_SETUP_NRD_SETUP_Pos))) |

| #define | SMC_SETUP_NRD_SETUP_Msk (0x3fu << SMC_SETUP_NRD_SETUP_Pos) |

| (SMC_SETUP) NRD Setup Length More... | |

| #define | SMC_SETUP_NRD_SETUP_Pos 16 |

| #define | SMC_SETUP_NWE_SETUP(value) ((SMC_SETUP_NWE_SETUP_Msk & ((value) << SMC_SETUP_NWE_SETUP_Pos))) |

| #define | SMC_SETUP_NWE_SETUP_Msk (0x3fu << SMC_SETUP_NWE_SETUP_Pos) |

| (SMC_SETUP) NWE Setup Length More... | |

| #define | SMC_SETUP_NWE_SETUP_Pos 0 |

| #define | SMC_VERSION_MFN_Msk (0x7u << SMC_VERSION_MFN_Pos) |

| (SMC_VERSION) Metal Fix Number More... | |

| #define | SMC_VERSION_MFN_Pos 16 |

| #define | SMC_VERSION_VERSION_Msk (0xfffu << SMC_VERSION_VERSION_Pos) |

| (SMC_VERSION) Hardware Module Version More... | |

| #define | SMC_VERSION_VERSION_Pos 0 |

| #define | SMC_WPMR_WPEN (0x1u << 0) |

| (SMC_WPMR) Write Protect Enable More... | |

| #define | SMC_WPMR_WPKEY(value) ((SMC_WPMR_WPKEY_Msk & ((value) << SMC_WPMR_WPKEY_Pos))) |

| #define | SMC_WPMR_WPKEY_Msk (0xffffffu << SMC_WPMR_WPKEY_Pos) |

| (SMC_WPMR) Write Protection Key More... | |

| #define | SMC_WPMR_WPKEY_PASSWD (0x534D43u << 8) |

| (SMC_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0. More... | |

| #define | SMC_WPMR_WPKEY_Pos 8 |

| #define | SMC_WPSR_WPVS (0x1u << 0) |

| (SMC_WPSR) Write Protection Violation Status More... | |

| #define | SMC_WPSR_WPVSRC_Msk (0xffffu << SMC_WPSR_WPVSRC_Pos) |

| (SMC_WPSR) Write Protection Violation Source More... | |

| #define | SMC_WPSR_WPVSRC_Pos 8 |

| #define | SMCCS_NUMBER_NUMBER 4 |

| Smc hardware registers. More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/smc.h.