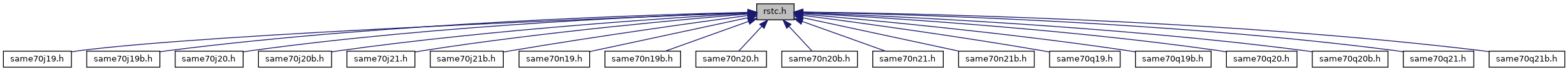

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Rstc |

| Rstc hardware registers. More... | |

Macros | |

| #define | RSTC_CR_EXTRST (0x1u << 3) |

| (RSTC_CR) External Reset More... | |

| #define | RSTC_CR_KEY(value) ((RSTC_CR_KEY_Msk & ((value) << RSTC_CR_KEY_Pos))) |

| #define | RSTC_CR_KEY_Msk (0xffu << RSTC_CR_KEY_Pos) |

| (RSTC_CR) System Reset Key More... | |

| #define | RSTC_CR_KEY_PASSWD (0xA5u << 24) |

| (RSTC_CR) Writing any other value in this field aborts the write operation. More... | |

| #define | RSTC_CR_KEY_Pos 24 |

| #define | RSTC_CR_PROCRST (0x1u << 0) |

| (RSTC_CR) Processor Reset More... | |

| #define | RSTC_MR_ERSTL(value) ((RSTC_MR_ERSTL_Msk & ((value) << RSTC_MR_ERSTL_Pos))) |

| #define | RSTC_MR_ERSTL_Msk (0xfu << RSTC_MR_ERSTL_Pos) |

| (RSTC_MR) External Reset Length More... | |

| #define | RSTC_MR_ERSTL_Pos 8 |

| #define | RSTC_MR_KEY(value) ((RSTC_MR_KEY_Msk & ((value) << RSTC_MR_KEY_Pos))) |

| #define | RSTC_MR_KEY_Msk (0xffu << RSTC_MR_KEY_Pos) |

| (RSTC_MR) Write Access Password More... | |

| #define | RSTC_MR_KEY_PASSWD (0xA5u << 24) |

| (RSTC_MR) Writing any other value in this field aborts the write operation.Always reads as 0. More... | |

| #define | RSTC_MR_KEY_Pos 24 |

| #define | RSTC_MR_URSTEN (0x1u << 0) |

| (RSTC_MR) User Reset Enable More... | |

| #define | RSTC_MR_URSTIEN (0x1u << 4) |

| (RSTC_MR) User Reset Interrupt Enable More... | |

| #define | RSTC_SR_NRSTL (0x1u << 16) |

| (RSTC_SR) NRST Pin Level More... | |

| #define | RSTC_SR_RSTTYP_BACKUP_RST (0x1u << 8) |

| (RSTC_SR) Return from Backup Mode More... | |

| #define | RSTC_SR_RSTTYP_GENERAL_RST (0x0u << 8) |

| (RSTC_SR) First power-up reset More... | |

| #define | RSTC_SR_RSTTYP_Msk (0x7u << RSTC_SR_RSTTYP_Pos) |

| (RSTC_SR) Reset Type More... | |

| #define | RSTC_SR_RSTTYP_Pos 8 |

| #define | RSTC_SR_RSTTYP_SOFT_RST (0x3u << 8) |

| (RSTC_SR) Processor reset required by the software More... | |

| #define | RSTC_SR_RSTTYP_USER_RST (0x4u << 8) |

| (RSTC_SR) NRST pin detected low More... | |

| #define | RSTC_SR_RSTTYP_WDT_RST (0x2u << 8) |

| (RSTC_SR) Watchdog fault occurred More... | |

| #define | RSTC_SR_SRCMP (0x1u << 17) |

| (RSTC_SR) Software Reset Command in Progress More... | |

| #define | RSTC_SR_URSTS (0x1u << 0) |

| (RSTC_SR) User Reset Status More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/rstc.h.