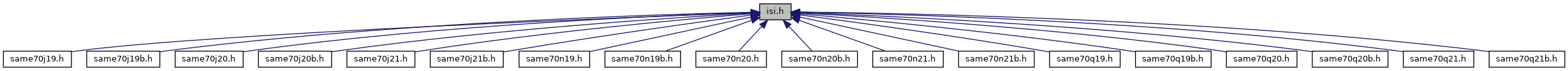

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Isi |

| Isi hardware registers. More... | |

Macros | |

| #define | ISI_CFG1_CRC_SYNC (0x1u << 7) |

| (ISI_CFG1) Embedded Synchronization Correction More... | |

| #define | ISI_CFG1_DISCR (0x1u << 11) |

| (ISI_CFG1) Disable Codec Request More... | |

| #define | ISI_CFG1_EMB_SYNC (0x1u << 6) |

| (ISI_CFG1) Embedded Synchronization More... | |

| #define | ISI_CFG1_FRATE(value) ((ISI_CFG1_FRATE_Msk & ((value) << ISI_CFG1_FRATE_Pos))) |

| #define | ISI_CFG1_FRATE_Msk (0x7u << ISI_CFG1_FRATE_Pos) |

| (ISI_CFG1) Frame Rate [0..7] More... | |

| #define | ISI_CFG1_FRATE_Pos 8 |

| #define | ISI_CFG1_FULL (0x1u << 12) |

| (ISI_CFG1) Full Mode is Allowed More... | |

| #define | ISI_CFG1_GRAYLE (0x1u << 5) |

| (ISI_CFG1) Grayscale Little Endian More... | |

| #define | ISI_CFG1_HSYNC_POL (0x1u << 2) |

| (ISI_CFG1) Horizontal Synchronization Polarity More... | |

| #define | ISI_CFG1_PIXCLK_POL (0x1u << 4) |

| (ISI_CFG1) Pixel Clock Polarity More... | |

| #define | ISI_CFG1_SFD(value) ((ISI_CFG1_SFD_Msk & ((value) << ISI_CFG1_SFD_Pos))) |

| #define | ISI_CFG1_SFD_Msk (0xffu << ISI_CFG1_SFD_Pos) |

| (ISI_CFG1) Start of Frame Delay More... | |

| #define | ISI_CFG1_SFD_Pos 24 |

| #define | ISI_CFG1_SLD(value) ((ISI_CFG1_SLD_Msk & ((value) << ISI_CFG1_SLD_Pos))) |

| #define | ISI_CFG1_SLD_Msk (0xffu << ISI_CFG1_SLD_Pos) |

| (ISI_CFG1) Start of Line Delay More... | |

| #define | ISI_CFG1_SLD_Pos 16 |

| #define | ISI_CFG1_THMASK(value) ((ISI_CFG1_THMASK_Msk & ((value) << ISI_CFG1_THMASK_Pos))) |

| #define | ISI_CFG1_THMASK_BEATS_16 (0x2u << 13) |

| (ISI_CFG1) 4, 8 and 16 beats AHB burst allowed More... | |

| #define | ISI_CFG1_THMASK_BEATS_4 (0x0u << 13) |

| (ISI_CFG1) Only 4 beats AHB burst allowed More... | |

| #define | ISI_CFG1_THMASK_BEATS_8 (0x1u << 13) |

| (ISI_CFG1) Only 4 and 8 beats AHB burst allowed More... | |

| #define | ISI_CFG1_THMASK_Msk (0x3u << ISI_CFG1_THMASK_Pos) |

| (ISI_CFG1) Threshold Mask More... | |

| #define | ISI_CFG1_THMASK_Pos 13 |

| #define | ISI_CFG1_VSYNC_POL (0x1u << 3) |

| (ISI_CFG1) Vertical Synchronization Polarity More... | |

| #define | ISI_CFG2_COL_SPACE (0x1u << 15) |

| (ISI_CFG2) Color Space for the Image Data More... | |

| #define | ISI_CFG2_GRAYSCALE (0x1u << 13) |

| (ISI_CFG2) Grayscale Mode Format Enable More... | |

| #define | ISI_CFG2_GS_MODE (0x1u << 11) |

| (ISI_CFG2) Grayscale Pixel Format Mode More... | |

| #define | ISI_CFG2_IM_HSIZE(value) ((ISI_CFG2_IM_HSIZE_Msk & ((value) << ISI_CFG2_IM_HSIZE_Pos))) |

| #define | ISI_CFG2_IM_HSIZE_Msk (0x7ffu << ISI_CFG2_IM_HSIZE_Pos) |

| (ISI_CFG2) Horizontal Size of the Image Sensor [0..2047] More... | |

| #define | ISI_CFG2_IM_HSIZE_Pos 16 |

| #define | ISI_CFG2_IM_VSIZE(value) ((ISI_CFG2_IM_VSIZE_Msk & ((value) << ISI_CFG2_IM_VSIZE_Pos))) |

| #define | ISI_CFG2_IM_VSIZE_Msk (0x7ffu << ISI_CFG2_IM_VSIZE_Pos) |

| (ISI_CFG2) Vertical Size of the Image Sensor [0..2047] More... | |

| #define | ISI_CFG2_IM_VSIZE_Pos 0 |

| #define | ISI_CFG2_RGB_CFG(value) ((ISI_CFG2_RGB_CFG_Msk & ((value) << ISI_CFG2_RGB_CFG_Pos))) |

| #define | ISI_CFG2_RGB_CFG_DEFAULT (0x0u << 30) |

| (ISI_CFG2) Byte 0 R/G(MSB)Byte 1 G(LSB)/BByte 2 R/G(MSB)Byte 3 G(LSB)/B More... | |

| #define | ISI_CFG2_RGB_CFG_MODE1 (0x1u << 30) |

| (ISI_CFG2) Byte 0 B/G(MSB)Byte 1 G(LSB)/RByte 2 B/G(MSB)Byte 3 G(LSB)/R More... | |

| #define | ISI_CFG2_RGB_CFG_MODE2 (0x2u << 30) |

| (ISI_CFG2) Byte 0 G(LSB)/RByte 1 B/G(MSB)Byte 2 G(LSB)/RByte 3 B/G(MSB) More... | |

| #define | ISI_CFG2_RGB_CFG_MODE3 (0x3u << 30) |

| (ISI_CFG2) Byte 0 G(LSB)/BByte 1 R/G(MSB)Byte 2 G(LSB)/BByte 3 R/G(MSB) More... | |

| #define | ISI_CFG2_RGB_CFG_Msk (0x3u << ISI_CFG2_RGB_CFG_Pos) |

| (ISI_CFG2) RGB Pixel Mapping Configuration More... | |

| #define | ISI_CFG2_RGB_CFG_Pos 30 |

| #define | ISI_CFG2_RGB_MODE (0x1u << 12) |

| (ISI_CFG2) RGB Input Mode More... | |

| #define | ISI_CFG2_RGB_SWAP (0x1u << 14) |

| (ISI_CFG2) RGB Format Swap Mode More... | |

| #define | ISI_CFG2_YCC_SWAP(value) ((ISI_CFG2_YCC_SWAP_Msk & ((value) << ISI_CFG2_YCC_SWAP_Pos))) |

| #define | ISI_CFG2_YCC_SWAP_DEFAULT (0x0u << 28) |

| (ISI_CFG2) Byte 0 Cb(i)Byte 1 Y(i)Byte 2 Cr(i)Byte 3 Y(i+1) More... | |

| #define | ISI_CFG2_YCC_SWAP_MODE1 (0x1u << 28) |

| (ISI_CFG2) Byte 0 Cr(i)Byte 1 Y(i)Byte 2 Cb(i)Byte 3 Y(i+1) More... | |

| #define | ISI_CFG2_YCC_SWAP_MODE2 (0x2u << 28) |

| (ISI_CFG2) Byte 0 Y(i)Byte 1 Cb(i)Byte 2 Y(i+1)Byte 3 Cr(i) More... | |

| #define | ISI_CFG2_YCC_SWAP_MODE3 (0x3u << 28) |

| (ISI_CFG2) Byte 0 Y(i)Byte 1 Cr(i)Byte 2 Y(i+1)Byte 3 Cb(i) More... | |

| #define | ISI_CFG2_YCC_SWAP_Msk (0x3u << ISI_CFG2_YCC_SWAP_Pos) |

| (ISI_CFG2) YCrCb Format Swap Mode More... | |

| #define | ISI_CFG2_YCC_SWAP_Pos 28 |

| #define | ISI_CR_ISI_CDC (0x1u << 8) |

| (ISI_CR) ISI Codec Request More... | |

| #define | ISI_CR_ISI_DIS (0x1u << 1) |

| (ISI_CR) ISI Module Disable Request More... | |

| #define | ISI_CR_ISI_EN (0x1u << 0) |

| (ISI_CR) ISI Module Enable Request More... | |

| #define | ISI_CR_ISI_SRST (0x1u << 2) |

| (ISI_CR) ISI Software Reset Request More... | |

| #define | ISI_DMA_C_ADDR_C_ADDR(value) ((ISI_DMA_C_ADDR_C_ADDR_Msk & ((value) << ISI_DMA_C_ADDR_C_ADDR_Pos))) |

| #define | ISI_DMA_C_ADDR_C_ADDR_Msk (0x3fffffffu << ISI_DMA_C_ADDR_C_ADDR_Pos) |

| (ISI_DMA_C_ADDR) Codec Image Base Address More... | |

| #define | ISI_DMA_C_ADDR_C_ADDR_Pos 2 |

| #define | ISI_DMA_C_CTRL_C_DONE (0x1u << 3) |

| (ISI_DMA_C_CTRL) Codec Transfer Done More... | |

| #define | ISI_DMA_C_CTRL_C_FETCH (0x1u << 0) |

| (ISI_DMA_C_CTRL) Descriptor Fetch Control Bit More... | |

| #define | ISI_DMA_C_CTRL_C_IEN (0x1u << 2) |

| (ISI_DMA_C_CTRL) Transfer Done Flag Control More... | |

| #define | ISI_DMA_C_CTRL_C_WB (0x1u << 1) |

| (ISI_DMA_C_CTRL) Descriptor Writeback Control Bit More... | |

| #define | ISI_DMA_C_DSCR_C_DSCR(value) ((ISI_DMA_C_DSCR_C_DSCR_Msk & ((value) << ISI_DMA_C_DSCR_C_DSCR_Pos))) |

| #define | ISI_DMA_C_DSCR_C_DSCR_Msk (0x3fffffffu << ISI_DMA_C_DSCR_C_DSCR_Pos) |

| (ISI_DMA_C_DSCR) Codec Descriptor Base Address More... | |

| #define | ISI_DMA_C_DSCR_C_DSCR_Pos 2 |

| #define | ISI_DMA_CHDR_C_CH_DIS (0x1u << 1) |

| (ISI_DMA_CHDR) Codec Channel Disable Request More... | |

| #define | ISI_DMA_CHDR_P_CH_DIS (0x1u << 0) |

| (ISI_DMA_CHDR) Preview Channel Disable Request More... | |

| #define | ISI_DMA_CHER_C_CH_EN (0x1u << 1) |

| (ISI_DMA_CHER) Codec Channel Enable More... | |

| #define | ISI_DMA_CHER_P_CH_EN (0x1u << 0) |

| (ISI_DMA_CHER) Preview Channel Enable More... | |

| #define | ISI_DMA_CHSR_C_CH_S (0x1u << 1) |

| (ISI_DMA_CHSR) Code DMA Channel Status More... | |

| #define | ISI_DMA_CHSR_P_CH_S (0x1u << 0) |

| (ISI_DMA_CHSR) Preview DMA Channel Status More... | |

| #define | ISI_DMA_P_ADDR_P_ADDR(value) ((ISI_DMA_P_ADDR_P_ADDR_Msk & ((value) << ISI_DMA_P_ADDR_P_ADDR_Pos))) |

| #define | ISI_DMA_P_ADDR_P_ADDR_Msk (0x3fffffffu << ISI_DMA_P_ADDR_P_ADDR_Pos) |

| (ISI_DMA_P_ADDR) Preview Image Base Address More... | |

| #define | ISI_DMA_P_ADDR_P_ADDR_Pos 2 |

| #define | ISI_DMA_P_CTRL_P_DONE (0x1u << 3) |

| (ISI_DMA_P_CTRL) Preview Transfer Done More... | |

| #define | ISI_DMA_P_CTRL_P_FETCH (0x1u << 0) |

| (ISI_DMA_P_CTRL) Descriptor Fetch Control Bit More... | |

| #define | ISI_DMA_P_CTRL_P_IEN (0x1u << 2) |

| (ISI_DMA_P_CTRL) Transfer Done Flag Control More... | |

| #define | ISI_DMA_P_CTRL_P_WB (0x1u << 1) |

| (ISI_DMA_P_CTRL) Descriptor Writeback Control Bit More... | |

| #define | ISI_DMA_P_DSCR_P_DSCR(value) ((ISI_DMA_P_DSCR_P_DSCR_Msk & ((value) << ISI_DMA_P_DSCR_P_DSCR_Pos))) |

| #define | ISI_DMA_P_DSCR_P_DSCR_Msk (0x3fffffffu << ISI_DMA_P_DSCR_P_DSCR_Pos) |

| (ISI_DMA_P_DSCR) Preview Descriptor Base Address More... | |

| #define | ISI_DMA_P_DSCR_P_DSCR_Pos 2 |

| #define | ISI_IDR_C_OVR (0x1u << 25) |

| (ISI_IDR) Codec Datapath Overflow Interrupt Disable More... | |

| #define | ISI_IDR_CRC_ERR (0x1u << 26) |

| (ISI_IDR) Embedded Synchronization CRC Error Interrupt Disable More... | |

| #define | ISI_IDR_CXFR_DONE (0x1u << 17) |

| (ISI_IDR) Codec DMA Transfer Done Interrupt Disable More... | |

| #define | ISI_IDR_DIS_DONE (0x1u << 1) |

| (ISI_IDR) Disable Done Interrupt Disable More... | |

| #define | ISI_IDR_FR_OVR (0x1u << 27) |

| (ISI_IDR) Frame Rate Overflow Interrupt Disable More... | |

| #define | ISI_IDR_P_OVR (0x1u << 24) |

| (ISI_IDR) Preview Datapath Overflow Interrupt Disable More... | |

| #define | ISI_IDR_PXFR_DONE (0x1u << 16) |

| (ISI_IDR) Preview DMA Transfer Done Interrupt Disable More... | |

| #define | ISI_IDR_SRST (0x1u << 2) |

| (ISI_IDR) Software Reset Interrupt Disable More... | |

| #define | ISI_IDR_VSYNC (0x1u << 10) |

| (ISI_IDR) Vertical Synchronization Interrupt Disable More... | |

| #define | ISI_IER_C_OVR (0x1u << 25) |

| (ISI_IER) Codec Datapath Overflow Interrupt Enable More... | |

| #define | ISI_IER_CRC_ERR (0x1u << 26) |

| (ISI_IER) Embedded Synchronization CRC Error Interrupt Enable More... | |

| #define | ISI_IER_CXFR_DONE (0x1u << 17) |

| (ISI_IER) Codec DMA Transfer Done Interrupt Enable More... | |

| #define | ISI_IER_DIS_DONE (0x1u << 1) |

| (ISI_IER) Disable Done Interrupt Enable More... | |

| #define | ISI_IER_FR_OVR (0x1u << 27) |

| (ISI_IER) Frame Rate Overflow Interrupt Enable More... | |

| #define | ISI_IER_P_OVR (0x1u << 24) |

| (ISI_IER) Preview Datapath Overflow Interrupt Enable More... | |

| #define | ISI_IER_PXFR_DONE (0x1u << 16) |

| (ISI_IER) Preview DMA Transfer Done Interrupt Enable More... | |

| #define | ISI_IER_SRST (0x1u << 2) |

| (ISI_IER) Software Reset Interrupt Enable More... | |

| #define | ISI_IER_VSYNC (0x1u << 10) |

| (ISI_IER) Vertical Synchronization Interrupt Enable More... | |

| #define | ISI_IMR_C_OVR (0x1u << 25) |

| (ISI_IMR) Codec FIFO Overflow More... | |

| #define | ISI_IMR_CRC_ERR (0x1u << 26) |

| (ISI_IMR) CRC Synchronization Error More... | |

| #define | ISI_IMR_CXFR_DONE (0x1u << 17) |

| (ISI_IMR) Codec DMA Transfer Completed More... | |

| #define | ISI_IMR_DIS_DONE (0x1u << 1) |

| (ISI_IMR) Module Disable Operation Completed More... | |

| #define | ISI_IMR_FR_OVR (0x1u << 27) |

| (ISI_IMR) Frame Rate Overrun More... | |

| #define | ISI_IMR_P_OVR (0x1u << 24) |

| (ISI_IMR) Preview FIFO Overflow More... | |

| #define | ISI_IMR_PXFR_DONE (0x1u << 16) |

| (ISI_IMR) Preview DMA Transfer Completed More... | |

| #define | ISI_IMR_SRST (0x1u << 2) |

| (ISI_IMR) Software Reset Completed More... | |

| #define | ISI_IMR_VSYNC (0x1u << 10) |

| (ISI_IMR) Vertical Synchronization More... | |

| #define | ISI_PDECF_DEC_FACTOR(value) ((ISI_PDECF_DEC_FACTOR_Msk & ((value) << ISI_PDECF_DEC_FACTOR_Pos))) |

| #define | ISI_PDECF_DEC_FACTOR_Msk (0xffu << ISI_PDECF_DEC_FACTOR_Pos) |

| (ISI_PDECF) Decimation Factor More... | |

| #define | ISI_PDECF_DEC_FACTOR_Pos 0 |

| #define | ISI_PSIZE_PREV_HSIZE(value) ((ISI_PSIZE_PREV_HSIZE_Msk & ((value) << ISI_PSIZE_PREV_HSIZE_Pos))) |

| #define | ISI_PSIZE_PREV_HSIZE_Msk (0x3ffu << ISI_PSIZE_PREV_HSIZE_Pos) |

| (ISI_PSIZE) Horizontal Size for the Preview Path More... | |

| #define | ISI_PSIZE_PREV_HSIZE_Pos 16 |

| #define | ISI_PSIZE_PREV_VSIZE(value) ((ISI_PSIZE_PREV_VSIZE_Msk & ((value) << ISI_PSIZE_PREV_VSIZE_Pos))) |

| #define | ISI_PSIZE_PREV_VSIZE_Msk (0x3ffu << ISI_PSIZE_PREV_VSIZE_Pos) |

| (ISI_PSIZE) Vertical Size for the Preview Path More... | |

| #define | ISI_PSIZE_PREV_VSIZE_Pos 0 |

| #define | ISI_R2Y_SET0_C0(value) ((ISI_R2Y_SET0_C0_Msk & ((value) << ISI_R2Y_SET0_C0_Pos))) |

| #define | ISI_R2Y_SET0_C0_Msk (0x7fu << ISI_R2Y_SET0_C0_Pos) |

| (ISI_R2Y_SET0) Color Space Conversion Matrix Coefficient C0 More... | |

| #define | ISI_R2Y_SET0_C0_Pos 0 |

| #define | ISI_R2Y_SET0_C1(value) ((ISI_R2Y_SET0_C1_Msk & ((value) << ISI_R2Y_SET0_C1_Pos))) |

| #define | ISI_R2Y_SET0_C1_Msk (0x7fu << ISI_R2Y_SET0_C1_Pos) |

| (ISI_R2Y_SET0) Color Space Conversion Matrix Coefficient C1 More... | |

| #define | ISI_R2Y_SET0_C1_Pos 8 |

| #define | ISI_R2Y_SET0_C2(value) ((ISI_R2Y_SET0_C2_Msk & ((value) << ISI_R2Y_SET0_C2_Pos))) |

| #define | ISI_R2Y_SET0_C2_Msk (0x7fu << ISI_R2Y_SET0_C2_Pos) |

| (ISI_R2Y_SET0) Color Space Conversion Matrix Coefficient C2 More... | |

| #define | ISI_R2Y_SET0_C2_Pos 16 |

| #define | ISI_R2Y_SET0_Roff (0x1u << 24) |

| (ISI_R2Y_SET0) Color Space Conversion Red Component Offset More... | |

| #define | ISI_R2Y_SET1_C3(value) ((ISI_R2Y_SET1_C3_Msk & ((value) << ISI_R2Y_SET1_C3_Pos))) |

| #define | ISI_R2Y_SET1_C3_Msk (0x7fu << ISI_R2Y_SET1_C3_Pos) |

| (ISI_R2Y_SET1) Color Space Conversion Matrix Coefficient C3 More... | |

| #define | ISI_R2Y_SET1_C3_Pos 0 |

| #define | ISI_R2Y_SET1_C4(value) ((ISI_R2Y_SET1_C4_Msk & ((value) << ISI_R2Y_SET1_C4_Pos))) |

| #define | ISI_R2Y_SET1_C4_Msk (0x7fu << ISI_R2Y_SET1_C4_Pos) |

| (ISI_R2Y_SET1) Color Space Conversion Matrix Coefficient C4 More... | |

| #define | ISI_R2Y_SET1_C4_Pos 8 |

| #define | ISI_R2Y_SET1_C5(value) ((ISI_R2Y_SET1_C5_Msk & ((value) << ISI_R2Y_SET1_C5_Pos))) |

| #define | ISI_R2Y_SET1_C5_Msk (0x7fu << ISI_R2Y_SET1_C5_Pos) |

| (ISI_R2Y_SET1) Color Space Conversion Matrix Coefficient C5 More... | |

| #define | ISI_R2Y_SET1_C5_Pos 16 |

| #define | ISI_R2Y_SET1_Goff (0x1u << 24) |

| (ISI_R2Y_SET1) Color Space Conversion Green Component Offset More... | |

| #define | ISI_R2Y_SET2_Boff (0x1u << 24) |

| (ISI_R2Y_SET2) Color Space Conversion Blue Component Offset More... | |

| #define | ISI_R2Y_SET2_C6(value) ((ISI_R2Y_SET2_C6_Msk & ((value) << ISI_R2Y_SET2_C6_Pos))) |

| #define | ISI_R2Y_SET2_C6_Msk (0x7fu << ISI_R2Y_SET2_C6_Pos) |

| (ISI_R2Y_SET2) Color Space Conversion Matrix Coefficient C6 More... | |

| #define | ISI_R2Y_SET2_C6_Pos 0 |

| #define | ISI_R2Y_SET2_C7(value) ((ISI_R2Y_SET2_C7_Msk & ((value) << ISI_R2Y_SET2_C7_Pos))) |

| #define | ISI_R2Y_SET2_C7_Msk (0x7fu << ISI_R2Y_SET2_C7_Pos) |

| (ISI_R2Y_SET2) Color Space Conversion Matrix Coefficient C7 More... | |

| #define | ISI_R2Y_SET2_C7_Pos 8 |

| #define | ISI_R2Y_SET2_C8(value) ((ISI_R2Y_SET2_C8_Msk & ((value) << ISI_R2Y_SET2_C8_Pos))) |

| #define | ISI_R2Y_SET2_C8_Msk (0x7fu << ISI_R2Y_SET2_C8_Pos) |

| (ISI_R2Y_SET2) Color Space Conversion Matrix Coefficient C8 More... | |

| #define | ISI_R2Y_SET2_C8_Pos 16 |

| #define | ISI_SR_C_OVR (0x1u << 25) |

| (ISI_SR) Codec Datapath Overflow (cleared on read) More... | |

| #define | ISI_SR_CDC_PND (0x1u << 8) |

| (ISI_SR) Pending Codec Request More... | |

| #define | ISI_SR_CRC_ERR (0x1u << 26) |

| (ISI_SR) CRC Synchronization Error (cleared on read) More... | |

| #define | ISI_SR_CXFR_DONE (0x1u << 17) |

| (ISI_SR) Codec DMA Transfer has Terminated (cleared on read) More... | |

| #define | ISI_SR_DIS_DONE (0x1u << 1) |

| (ISI_SR) Module Disable Request has Terminated (cleared on read) More... | |

| #define | ISI_SR_ENABLE (0x1u << 0) |

| (ISI_SR) Module Enable More... | |

| #define | ISI_SR_FR_OVR (0x1u << 27) |

| (ISI_SR) Frame Rate Overrun (cleared on read) More... | |

| #define | ISI_SR_P_OVR (0x1u << 24) |

| (ISI_SR) Preview Datapath Overflow (cleared on read) More... | |

| #define | ISI_SR_PXFR_DONE (0x1u << 16) |

| (ISI_SR) Preview DMA Transfer has Terminated (cleared on read) More... | |

| #define | ISI_SR_SIP (0x1u << 19) |

| (ISI_SR) Synchronization in Progress More... | |

| #define | ISI_SR_SRST (0x1u << 2) |

| (ISI_SR) Module Software Reset Request has Terminated (cleared on read) More... | |

| #define | ISI_SR_VSYNC (0x1u << 10) |

| (ISI_SR) Vertical Synchronization (cleared on read) More... | |

| #define | ISI_VERSION_MFN_Msk (0x7u << ISI_VERSION_MFN_Pos) |

| (ISI_VERSION) Metal Fix Number More... | |

| #define | ISI_VERSION_MFN_Pos 16 |

| #define | ISI_VERSION_VERSION_Msk (0xfffu << ISI_VERSION_VERSION_Pos) |

| (ISI_VERSION) Version of the Hardware Module More... | |

| #define | ISI_VERSION_VERSION_Pos 0 |

| #define | ISI_WPMR_WPEN (0x1u << 0) |

| (ISI_WPMR) Write Protection Enable More... | |

| #define | ISI_WPMR_WPKEY(value) ((ISI_WPMR_WPKEY_Msk & ((value) << ISI_WPMR_WPKEY_Pos))) |

| #define | ISI_WPMR_WPKEY_Msk (0xffffffu << ISI_WPMR_WPKEY_Pos) |

| (ISI_WPMR) Write Protection Key Password More... | |

| #define | ISI_WPMR_WPKEY_PASSWD (0x495349u << 8) |

| (ISI_WPMR) Writing any other value in this field aborts the write operation of the WPEN bit.Always reads as 0. More... | |

| #define | ISI_WPMR_WPKEY_Pos 8 |

| #define | ISI_WPSR_WPVS (0x1u << 0) |

| (ISI_WPSR) Write Protection Violation Status More... | |

| #define | ISI_WPSR_WPVSRC_Msk (0xffffu << ISI_WPSR_WPVSRC_Pos) |

| (ISI_WPSR) Write Protection Violation Source More... | |

| #define | ISI_WPSR_WPVSRC_Pos 8 |

| #define | ISI_Y2R_SET0_C0(value) ((ISI_Y2R_SET0_C0_Msk & ((value) << ISI_Y2R_SET0_C0_Pos))) |

| #define | ISI_Y2R_SET0_C0_Msk (0xffu << ISI_Y2R_SET0_C0_Pos) |

| (ISI_Y2R_SET0) Color Space Conversion Matrix Coefficient C0 More... | |

| #define | ISI_Y2R_SET0_C0_Pos 0 |

| #define | ISI_Y2R_SET0_C1(value) ((ISI_Y2R_SET0_C1_Msk & ((value) << ISI_Y2R_SET0_C1_Pos))) |

| #define | ISI_Y2R_SET0_C1_Msk (0xffu << ISI_Y2R_SET0_C1_Pos) |

| (ISI_Y2R_SET0) Color Space Conversion Matrix Coefficient C1 More... | |

| #define | ISI_Y2R_SET0_C1_Pos 8 |

| #define | ISI_Y2R_SET0_C2(value) ((ISI_Y2R_SET0_C2_Msk & ((value) << ISI_Y2R_SET0_C2_Pos))) |

| #define | ISI_Y2R_SET0_C2_Msk (0xffu << ISI_Y2R_SET0_C2_Pos) |

| (ISI_Y2R_SET0) Color Space Conversion Matrix Coefficient C2 More... | |

| #define | ISI_Y2R_SET0_C2_Pos 16 |

| #define | ISI_Y2R_SET0_C3(value) ((ISI_Y2R_SET0_C3_Msk & ((value) << ISI_Y2R_SET0_C3_Pos))) |

| #define | ISI_Y2R_SET0_C3_Msk (0xffu << ISI_Y2R_SET0_C3_Pos) |

| (ISI_Y2R_SET0) Color Space Conversion Matrix Coefficient C3 More... | |

| #define | ISI_Y2R_SET0_C3_Pos 24 |

| #define | ISI_Y2R_SET1_C4(value) ((ISI_Y2R_SET1_C4_Msk & ((value) << ISI_Y2R_SET1_C4_Pos))) |

| #define | ISI_Y2R_SET1_C4_Msk (0x1ffu << ISI_Y2R_SET1_C4_Pos) |

| (ISI_Y2R_SET1) Color Space Conversion Matrix Coefficient C4 More... | |

| #define | ISI_Y2R_SET1_C4_Pos 0 |

| #define | ISI_Y2R_SET1_Cboff (0x1u << 14) |

| (ISI_Y2R_SET1) Color Space Conversion Blue Chrominance Default Offset More... | |

| #define | ISI_Y2R_SET1_Croff (0x1u << 13) |

| (ISI_Y2R_SET1) Color Space Conversion Red Chrominance Default Offset More... | |

| #define | ISI_Y2R_SET1_Yoff (0x1u << 12) |

| (ISI_Y2R_SET1) Color Space Conversion Luminance Default Offset More... | |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/isi.h.