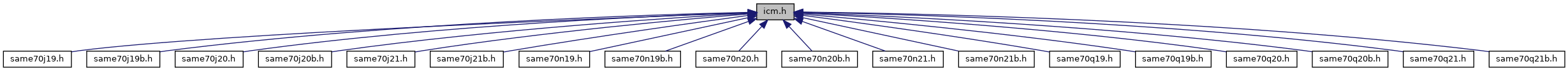

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Icm |

| Icm hardware registers. More... | |

Macros | |

| #define | ICM_ADDRSIZE_ADDRSIZE_Msk (0xffffu << ICM_ADDRSIZE_ADDRSIZE_Pos) |

| (ICM_ADDRSIZE) Peripheral Bus Address Area Size More... | |

| #define | ICM_ADDRSIZE_ADDRSIZE_Pos 0 |

| #define | ICM_CFG_ASCD (0x1u << 8) |

| (ICM_CFG) Automatic Switch To Compare Digest More... | |

| #define | ICM_CFG_BBC(value) ((ICM_CFG_BBC_Msk & ((value) << ICM_CFG_BBC_Pos))) |

| #define | ICM_CFG_BBC_Msk (0xfu << ICM_CFG_BBC_Pos) |

| (ICM_CFG) Bus Burden Control More... | |

| #define | ICM_CFG_BBC_Pos 4 |

| #define | ICM_CFG_DAPROT(value) ((ICM_CFG_DAPROT_Msk & ((value) << ICM_CFG_DAPROT_Pos))) |

| #define | ICM_CFG_DAPROT_Msk (0x3fu << ICM_CFG_DAPROT_Pos) |

| (ICM_CFG) Region Descriptor Area Protection More... | |

| #define | ICM_CFG_DAPROT_Pos 24 |

| #define | ICM_CFG_DUALBUFF (0x1u << 9) |

| (ICM_CFG) Dual Input Buffer More... | |

| #define | ICM_CFG_EOMDIS (0x1u << 1) |

| (ICM_CFG) End of Monitoring Disable More... | |

| #define | ICM_CFG_HAPROT(value) ((ICM_CFG_HAPROT_Msk & ((value) << ICM_CFG_HAPROT_Pos))) |

| #define | ICM_CFG_HAPROT_Msk (0x3fu << ICM_CFG_HAPROT_Pos) |

| (ICM_CFG) Region Hash Area Protection More... | |

| #define | ICM_CFG_HAPROT_Pos 16 |

| #define | ICM_CFG_SLBDIS (0x1u << 2) |

| (ICM_CFG) Secondary List Branching Disable More... | |

| #define | ICM_CFG_UALGO(value) ((ICM_CFG_UALGO_Msk & ((value) << ICM_CFG_UALGO_Pos))) |

| #define | ICM_CFG_UALGO_Msk (0x7u << ICM_CFG_UALGO_Pos) |

| (ICM_CFG) User SHA Algorithm More... | |

| #define | ICM_CFG_UALGO_Pos 13 |

| #define | ICM_CFG_UALGO_SHA1 (0x0u << 13) |

| (ICM_CFG) SHA1 algorithm processed More... | |

| #define | ICM_CFG_UALGO_SHA224 (0x4u << 13) |

| (ICM_CFG) SHA224 algorithm processed More... | |

| #define | ICM_CFG_UALGO_SHA256 (0x1u << 13) |

| (ICM_CFG) SHA256 algorithm processed More... | |

| #define | ICM_CFG_UIHASH (0x1u << 12) |

| (ICM_CFG) User Initial Hash Value More... | |

| #define | ICM_CFG_WBDIS (0x1u << 0) |

| (ICM_CFG) Write Back Disable More... | |

| #define | ICM_CTRL_DISABLE (0x1u << 1) |

| (ICM_CTRL) ICM Disable Register More... | |

| #define | ICM_CTRL_ENABLE (0x1u << 0) |

| (ICM_CTRL) ICM Enable More... | |

| #define | ICM_CTRL_REHASH(value) ((ICM_CTRL_REHASH_Msk & ((value) << ICM_CTRL_REHASH_Pos))) |

| #define | ICM_CTRL_REHASH_Msk (0xfu << ICM_CTRL_REHASH_Pos) |

| (ICM_CTRL) Recompute Internal Hash More... | |

| #define | ICM_CTRL_REHASH_Pos 4 |

| #define | ICM_CTRL_RMDIS(value) ((ICM_CTRL_RMDIS_Msk & ((value) << ICM_CTRL_RMDIS_Pos))) |

| #define | ICM_CTRL_RMDIS_Msk (0xfu << ICM_CTRL_RMDIS_Pos) |

| (ICM_CTRL) Region Monitoring Disable More... | |

| #define | ICM_CTRL_RMDIS_Pos 8 |

| #define | ICM_CTRL_RMEN(value) ((ICM_CTRL_RMEN_Msk & ((value) << ICM_CTRL_RMEN_Pos))) |

| #define | ICM_CTRL_RMEN_Msk (0xfu << ICM_CTRL_RMEN_Pos) |

| (ICM_CTRL) Region Monitoring Enable More... | |

| #define | ICM_CTRL_RMEN_Pos 12 |

| #define | ICM_CTRL_SWRST (0x1u << 2) |

| (ICM_CTRL) Software Reset More... | |

| #define | ICM_DSCR_DASA(value) ((ICM_DSCR_DASA_Msk & ((value) << ICM_DSCR_DASA_Pos))) |

| #define | ICM_DSCR_DASA_Msk (0x3ffffffu << ICM_DSCR_DASA_Pos) |

| (ICM_DSCR) Descriptor Area Start Address More... | |

| #define | ICM_DSCR_DASA_Pos 6 |

| #define | ICM_FEATURES_BTYP (0x1u << 8) |

| (ICM_FEATURES) Bridge Type More... | |

| #define | ICM_FEATURES_CFGALGO (0x1u << 0) |

| (ICM_FEATURES) Configurable Algorithms More... | |

| #define | ICM_FEATURES_CFGPP (0x1u << 2) |

| (ICM_FEATURES) Configurable Processing Period More... | |

| #define | ICM_FEATURES_EF (0x1u << 6) |

| (ICM_FEATURES) Embedded LFSR More... | |

| #define | ICM_FEATURES_HDPP (0x1u << 3) |

| (ICM_FEATURES) Hardcoded Processing Period More... | |

| #define | ICM_FEATURES_HSHA1 (0x1u << 16) |

| (ICM_FEATURES) SHA1 Hardcoded Mode More... | |

| #define | ICM_FEATURES_HSHA224 (0x1u << 17) |

| (ICM_FEATURES) SHA224 Hardcoded Mode More... | |

| #define | ICM_FEATURES_HSHA256 (0x1u << 18) |

| (ICM_FEATURES) SHA256 Hardcoded Mode More... | |

| #define | ICM_FEATURES_HSHA384 (0x1u << 19) |

| (ICM_FEATURES) SHA384 Hardcoded Mode More... | |

| #define | ICM_FEATURES_HSHA512 (0x1u << 20) |

| (ICM_FEATURES) SHA512 Hardcoded Mode More... | |

| #define | ICM_FEATURES_NAIS (0x1u << 5) |

| (ICM_FEATURES) No Access to Intermediate State More... | |

| #define | ICM_FEATURES_PDC (0x1u << 4) |

| (ICM_FEATURES) Peripheral DMA Logic More... | |

| #define | ICM_FEATURES_PDCOFF0C (0x1u << 9) |

| (ICM_FEATURES) PDC Offset is 0x0C More... | |

| #define | ICM_FEATURES_RFU (0x1u << 1) |

| (ICM_FEATURES) Reserved for Future Use More... | |

| #define | ICM_FEATURES_SI (0x1u << 7) |

| (ICM_FEATURES) Scan Intrusion More... | |

| #define | ICM_HASH_HASA(value) ((ICM_HASH_HASA_Msk & ((value) << ICM_HASH_HASA_Pos))) |

| #define | ICM_HASH_HASA_Msk (0x1ffffffu << ICM_HASH_HASA_Pos) |

| (ICM_HASH) Hash Area Start Address More... | |

| #define | ICM_HASH_HASA_Pos 7 |

| #define | ICM_IDR_RBE(value) ((ICM_IDR_RBE_Msk & ((value) << ICM_IDR_RBE_Pos))) |

| #define | ICM_IDR_RBE_Msk (0xfu << ICM_IDR_RBE_Pos) |

| (ICM_IDR) Region Bus Error Interrupt Disable More... | |

| #define | ICM_IDR_RBE_Pos 8 |

| #define | ICM_IDR_RDM(value) ((ICM_IDR_RDM_Msk & ((value) << ICM_IDR_RDM_Pos))) |

| #define | ICM_IDR_RDM_Msk (0xfu << ICM_IDR_RDM_Pos) |

| (ICM_IDR) Region Digest Mismatch Interrupt Disable More... | |

| #define | ICM_IDR_RDM_Pos 4 |

| #define | ICM_IDR_REC(value) ((ICM_IDR_REC_Msk & ((value) << ICM_IDR_REC_Pos))) |

| #define | ICM_IDR_REC_Msk (0xfu << ICM_IDR_REC_Pos) |

| (ICM_IDR) Region End bit Condition detected Interrupt Disable More... | |

| #define | ICM_IDR_REC_Pos 16 |

| #define | ICM_IDR_RHC(value) ((ICM_IDR_RHC_Msk & ((value) << ICM_IDR_RHC_Pos))) |

| #define | ICM_IDR_RHC_Msk (0xfu << ICM_IDR_RHC_Pos) |

| (ICM_IDR) Region Hash Completed Interrupt Disable More... | |

| #define | ICM_IDR_RHC_Pos 0 |

| #define | ICM_IDR_RSU(value) ((ICM_IDR_RSU_Msk & ((value) << ICM_IDR_RSU_Pos))) |

| #define | ICM_IDR_RSU_Msk (0xfu << ICM_IDR_RSU_Pos) |

| (ICM_IDR) Region Status Updated Interrupt Disable More... | |

| #define | ICM_IDR_RSU_Pos 20 |

| #define | ICM_IDR_RWC(value) ((ICM_IDR_RWC_Msk & ((value) << ICM_IDR_RWC_Pos))) |

| #define | ICM_IDR_RWC_Msk (0xfu << ICM_IDR_RWC_Pos) |

| (ICM_IDR) Region Wrap Condition Detected Interrupt Disable More... | |

| #define | ICM_IDR_RWC_Pos 12 |

| #define | ICM_IDR_URAD (0x1u << 24) |

| (ICM_IDR) Undefined Register Access Detection Interrupt Disable More... | |

| #define | ICM_IER_RBE(value) ((ICM_IER_RBE_Msk & ((value) << ICM_IER_RBE_Pos))) |

| #define | ICM_IER_RBE_Msk (0xfu << ICM_IER_RBE_Pos) |

| (ICM_IER) Region Bus Error Interrupt Enable More... | |

| #define | ICM_IER_RBE_Pos 8 |

| #define | ICM_IER_RDM(value) ((ICM_IER_RDM_Msk & ((value) << ICM_IER_RDM_Pos))) |

| #define | ICM_IER_RDM_Msk (0xfu << ICM_IER_RDM_Pos) |

| (ICM_IER) Region Digest Mismatch Interrupt Enable More... | |

| #define | ICM_IER_RDM_Pos 4 |

| #define | ICM_IER_REC(value) ((ICM_IER_REC_Msk & ((value) << ICM_IER_REC_Pos))) |

| #define | ICM_IER_REC_Msk (0xfu << ICM_IER_REC_Pos) |

| (ICM_IER) Region End bit Condition Detected Interrupt Enable More... | |

| #define | ICM_IER_REC_Pos 16 |

| #define | ICM_IER_RHC(value) ((ICM_IER_RHC_Msk & ((value) << ICM_IER_RHC_Pos))) |

| #define | ICM_IER_RHC_Msk (0xfu << ICM_IER_RHC_Pos) |

| (ICM_IER) Region Hash Completed Interrupt Enable More... | |

| #define | ICM_IER_RHC_Pos 0 |

| #define | ICM_IER_RSU(value) ((ICM_IER_RSU_Msk & ((value) << ICM_IER_RSU_Pos))) |

| #define | ICM_IER_RSU_Msk (0xfu << ICM_IER_RSU_Pos) |

| (ICM_IER) Region Status Updated Interrupt Disable More... | |

| #define | ICM_IER_RSU_Pos 20 |

| #define | ICM_IER_RWC(value) ((ICM_IER_RWC_Msk & ((value) << ICM_IER_RWC_Pos))) |

| #define | ICM_IER_RWC_Msk (0xfu << ICM_IER_RWC_Pos) |

| (ICM_IER) Region Wrap Condition detected Interrupt Enable More... | |

| #define | ICM_IER_RWC_Pos 12 |

| #define | ICM_IER_URAD (0x1u << 24) |

| (ICM_IER) Undefined Register Access Detection Interrupt Enable More... | |

| #define | ICM_IMR_RBE_Msk (0xfu << ICM_IMR_RBE_Pos) |

| (ICM_IMR) Region Bus Error Interrupt Mask More... | |

| #define | ICM_IMR_RBE_Pos 8 |

| #define | ICM_IMR_RDM_Msk (0xfu << ICM_IMR_RDM_Pos) |

| (ICM_IMR) Region Digest Mismatch Interrupt Mask More... | |

| #define | ICM_IMR_RDM_Pos 4 |

| #define | ICM_IMR_REC_Msk (0xfu << ICM_IMR_REC_Pos) |

| (ICM_IMR) Region End bit Condition Detected Interrupt Mask More... | |

| #define | ICM_IMR_REC_Pos 16 |

| #define | ICM_IMR_RHC_Msk (0xfu << ICM_IMR_RHC_Pos) |

| (ICM_IMR) Region Hash Completed Interrupt Mask More... | |

| #define | ICM_IMR_RHC_Pos 0 |

| #define | ICM_IMR_RSU_Msk (0xfu << ICM_IMR_RSU_Pos) |

| (ICM_IMR) Region Status Updated Interrupt Mask More... | |

| #define | ICM_IMR_RSU_Pos 20 |

| #define | ICM_IMR_RWC_Msk (0xfu << ICM_IMR_RWC_Pos) |

| (ICM_IMR) Region Wrap Condition Detected Interrupt Mask More... | |

| #define | ICM_IMR_RWC_Pos 12 |

| #define | ICM_IMR_URAD (0x1u << 24) |

| (ICM_IMR) Undefined Register Access Detection Interrupt Mask More... | |

| #define | ICM_IPNAME_IPNAME_Msk (0xffffffffu << ICM_IPNAME_IPNAME_Pos) |

| (ICM_IPNAME[2]) IP Name in ASCII Format More... | |

| #define | ICM_IPNAME_IPNAME_Pos 0 |

| #define | ICM_ISR_RBE_Msk (0xfu << ICM_ISR_RBE_Pos) |

| (ICM_ISR) Region Bus Error More... | |

| #define | ICM_ISR_RBE_Pos 8 |

| #define | ICM_ISR_RDM_Msk (0xfu << ICM_ISR_RDM_Pos) |

| (ICM_ISR) Region Digest Mismatch More... | |

| #define | ICM_ISR_RDM_Pos 4 |

| #define | ICM_ISR_REC_Msk (0xfu << ICM_ISR_REC_Pos) |

| (ICM_ISR) Region End bit Condition Detected More... | |

| #define | ICM_ISR_REC_Pos 16 |

| #define | ICM_ISR_RHC_Msk (0xfu << ICM_ISR_RHC_Pos) |

| (ICM_ISR) Region Hash Completed More... | |

| #define | ICM_ISR_RHC_Pos 0 |

| #define | ICM_ISR_RSU_Msk (0xfu << ICM_ISR_RSU_Pos) |

| (ICM_ISR) Region Status Updated Detected More... | |

| #define | ICM_ISR_RSU_Pos 20 |

| #define | ICM_ISR_RWC_Msk (0xfu << ICM_ISR_RWC_Pos) |

| (ICM_ISR) Region Wrap Condition Detected More... | |

| #define | ICM_ISR_RWC_Pos 12 |

| #define | ICM_ISR_URAD (0x1u << 24) |

| (ICM_ISR) Undefined Register Access Detection Status More... | |

| #define | ICM_SR_ENABLE (0x1u << 0) |

| (ICM_SR) ICM Controller Enable Register More... | |

| #define | ICM_SR_RAWRMDIS(value) ((ICM_SR_RAWRMDIS_Msk & ((value) << ICM_SR_RAWRMDIS_Pos))) |

| #define | ICM_SR_RAWRMDIS_Msk (0xfu << ICM_SR_RAWRMDIS_Pos) |

| (ICM_SR) RAW Region Monitoring Disabled Status More... | |

| #define | ICM_SR_RAWRMDIS_Pos 8 |

| #define | ICM_SR_RMDIS(value) ((ICM_SR_RMDIS_Msk & ((value) << ICM_SR_RMDIS_Pos))) |

| #define | ICM_SR_RMDIS_Msk (0xfu << ICM_SR_RMDIS_Pos) |

| (ICM_SR) Region Monitoring Disabled Status More... | |

| #define | ICM_SR_RMDIS_Pos 12 |

| #define | ICM_UASR_URAT_ICM_CFG_MODIFIED (0x1u << 0) |

| (ICM_UASR) ICM_CFG modified during active monitoring. More... | |

| #define | ICM_UASR_URAT_ICM_DSCR_MODIFIED (0x2u << 0) |

| (ICM_UASR) ICM_DSCR modified during active monitoring. More... | |

| #define | ICM_UASR_URAT_ICM_HASH_MODIFIED (0x3u << 0) |

| (ICM_UASR) ICM_HASH modified during active monitoring More... | |

| #define | ICM_UASR_URAT_Msk (0x7u << ICM_UASR_URAT_Pos) |

| (ICM_UASR) Undefined Register Access Trace More... | |

| #define | ICM_UASR_URAT_Pos 0 |

| #define | ICM_UASR_URAT_READ_ACCESS (0x4u << 0) |

| (ICM_UASR) Write-only register read access More... | |

| #define | ICM_UASR_URAT_UNSPEC_STRUCT_MEMBER (0x0u << 0) |

| (ICM_UASR) Unspecified structure member set to one detected when the descriptor is loaded. More... | |

| #define | ICM_UIHVAL_VAL(value) ((ICM_UIHVAL_VAL_Msk & ((value) << ICM_UIHVAL_VAL_Pos))) |

| #define | ICM_UIHVAL_VAL_Msk (0xffffffffu << ICM_UIHVAL_VAL_Pos) |

| (ICM_UIHVAL[8]) Initial Hash Value More... | |

| #define | ICM_UIHVAL_VAL_Pos 0 |

| #define | ICM_VERSION_MFN_Msk (0x7u << ICM_VERSION_MFN_Pos) |

| (ICM_VERSION) Metal Fix Number More... | |

| #define | ICM_VERSION_MFN_Pos 16 |

| #define | ICM_VERSION_VERSION_Msk (0xfffu << ICM_VERSION_VERSION_Pos) |

| (ICM_VERSION) Version of the Hardware Module More... | |

| #define | ICM_VERSION_VERSION_Pos 0 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/icm.h.