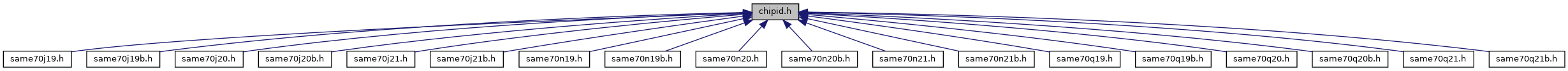

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | Chipid |

| Chipid hardware registers. More... | |

Macros | |

| #define | CHIPID_CIDR_ARCH_Msk (0xffu << CHIPID_CIDR_ARCH_Pos) |

| (CHIPID_CIDR) Architecture Identifier More... | |

| #define | CHIPID_CIDR_ARCH_Pos 20 |

| #define | CHIPID_CIDR_ARCH_SAME70 (0x10u << 20) |

| (CHIPID_CIDR) SAM E70 More... | |

| #define | CHIPID_CIDR_ARCH_SAMS70 (0x11u << 20) |

| (CHIPID_CIDR) SAM S70 More... | |

| #define | CHIPID_CIDR_ARCH_SAMV70 (0x13u << 20) |

| (CHIPID_CIDR) SAM V70 More... | |

| #define | CHIPID_CIDR_ARCH_SAMV71 (0x12u << 20) |

| (CHIPID_CIDR) SAM V71 More... | |

| #define | CHIPID_CIDR_EPROC_ARM7TDMI (0x2u << 5) |

| (CHIPID_CIDR) ARM7TDMI More... | |

| #define | CHIPID_CIDR_EPROC_ARM920T (0x4u << 5) |

| (CHIPID_CIDR) ARM920T More... | |

| #define | CHIPID_CIDR_EPROC_ARM926EJS (0x5u << 5) |

| (CHIPID_CIDR) ARM926EJS More... | |

| #define | CHIPID_CIDR_EPROC_ARM946ES (0x1u << 5) |

| (CHIPID_CIDR) ARM946ES More... | |

| #define | CHIPID_CIDR_EPROC_CA5 (0x6u << 5) |

| (CHIPID_CIDR) Cortex-A5 More... | |

| #define | CHIPID_CIDR_EPROC_CM3 (0x3u << 5) |

| (CHIPID_CIDR) Cortex-M3 More... | |

| #define | CHIPID_CIDR_EPROC_CM4 (0x7u << 5) |

| (CHIPID_CIDR) Cortex-M4 More... | |

| #define | CHIPID_CIDR_EPROC_Msk (0x7u << CHIPID_CIDR_EPROC_Pos) |

| (CHIPID_CIDR) Embedded Processor More... | |

| #define | CHIPID_CIDR_EPROC_Pos 5 |

| #define | CHIPID_CIDR_EPROC_SAMx7 (0x0u << 5) |

| (CHIPID_CIDR) Cortex-M7 More... | |

| #define | CHIPID_CIDR_EXT (0x1u << 31) |

| (CHIPID_CIDR) Extension Flag More... | |

| #define | CHIPID_CIDR_NVPSIZ2_1024K (0xCu << 12) |

| (CHIPID_CIDR) 1024 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_128K (0x7u << 12) |

| (CHIPID_CIDR) 128 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_16K (0x2u << 12) |

| (CHIPID_CIDR) 16 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_2048K (0xEu << 12) |

| (CHIPID_CIDR) 2048 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_256K (0x9u << 12) |

| (CHIPID_CIDR) 256 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_32K (0x3u << 12) |

| (CHIPID_CIDR) 32 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_512K (0xAu << 12) |

| (CHIPID_CIDR) 512 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_64K (0x5u << 12) |

| (CHIPID_CIDR) 64 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_8K (0x1u << 12) |

| (CHIPID_CIDR) 8 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ2_Msk (0xfu << CHIPID_CIDR_NVPSIZ2_Pos) |

| (CHIPID_CIDR) Second Nonvolatile Program Memory Size More... | |

| #define | CHIPID_CIDR_NVPSIZ2_NONE (0x0u << 12) |

| (CHIPID_CIDR) None More... | |

| #define | CHIPID_CIDR_NVPSIZ2_Pos 12 |

| #define | CHIPID_CIDR_NVPSIZ_1024K (0xCu << 8) |

| (CHIPID_CIDR) 1024 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_128K (0x7u << 8) |

| (CHIPID_CIDR) 128 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_160K (0x8u << 8) |

| (CHIPID_CIDR) 160 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_16K (0x2u << 8) |

| (CHIPID_CIDR) 16 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_2048K (0xEu << 8) |

| (CHIPID_CIDR) 2048 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_256K (0x9u << 8) |

| (CHIPID_CIDR) 256 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_32K (0x3u << 8) |

| (CHIPID_CIDR) 32 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_512K (0xAu << 8) |

| (CHIPID_CIDR) 512 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_64K (0x5u << 8) |

| (CHIPID_CIDR) 64 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_8K (0x1u << 8) |

| (CHIPID_CIDR) 8 Kbytes More... | |

| #define | CHIPID_CIDR_NVPSIZ_Msk (0xfu << CHIPID_CIDR_NVPSIZ_Pos) |

| (CHIPID_CIDR) Nonvolatile Program Memory Size More... | |

| #define | CHIPID_CIDR_NVPSIZ_NONE (0x0u << 8) |

| (CHIPID_CIDR) None More... | |

| #define | CHIPID_CIDR_NVPSIZ_Pos 8 |

| #define | CHIPID_CIDR_NVPTYP_FLASH (0x2u << 28) |

| (CHIPID_CIDR) Embedded Flash Memory More... | |

| #define | CHIPID_CIDR_NVPTYP_Msk (0x7u << CHIPID_CIDR_NVPTYP_Pos) |

| (CHIPID_CIDR) Nonvolatile Program Memory Type More... | |

| #define | CHIPID_CIDR_NVPTYP_Pos 28 |

| #define | CHIPID_CIDR_NVPTYP_ROM (0x0u << 28) |

| (CHIPID_CIDR) ROM More... | |

| #define | CHIPID_CIDR_NVPTYP_ROM_FLASH (0x3u << 28) |

| (CHIPID_CIDR) ROM and Embedded Flash Memory- NVPSIZ is ROM size- NVPSIZ2 is Flash size More... | |

| #define | CHIPID_CIDR_NVPTYP_ROMLESS (0x1u << 28) |

| (CHIPID_CIDR) ROMless or on-chip Flash More... | |

| #define | CHIPID_CIDR_NVPTYP_SRAM (0x4u << 28) |

| (CHIPID_CIDR) SRAM emulating ROM More... | |

| #define | CHIPID_CIDR_SRAMSIZ_128K (0xCu << 16) |

| (CHIPID_CIDR) 128 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_160K (0x7u << 16) |

| (CHIPID_CIDR) 160 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_16K (0x9u << 16) |

| (CHIPID_CIDR) 16 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_192K (0x1u << 16) |

| (CHIPID_CIDR) 192 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_24K (0x4u << 16) |

| (CHIPID_CIDR) 24 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_256K (0xDu << 16) |

| (CHIPID_CIDR) 256 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_32K (0xAu << 16) |

| (CHIPID_CIDR) 32 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_384K (0x2u << 16) |

| (CHIPID_CIDR) 384 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_48K (0x0u << 16) |

| (CHIPID_CIDR) 48 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_4K (0x5u << 16) |

| (CHIPID_CIDR) 4 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_512K (0xFu << 16) |

| (CHIPID_CIDR) 512 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_64K (0xBu << 16) |

| (CHIPID_CIDR) 64 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_6K (0x3u << 16) |

| (CHIPID_CIDR) 6 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_80K (0x6u << 16) |

| (CHIPID_CIDR) 80 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_8K (0x8u << 16) |

| (CHIPID_CIDR) 8 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_96K (0xEu << 16) |

| (CHIPID_CIDR) 96 Kbytes More... | |

| #define | CHIPID_CIDR_SRAMSIZ_Msk (0xfu << CHIPID_CIDR_SRAMSIZ_Pos) |

| (CHIPID_CIDR) Internal SRAM Size More... | |

| #define | CHIPID_CIDR_SRAMSIZ_Pos 16 |

| #define | CHIPID_CIDR_VERSION_Msk (0x1fu << CHIPID_CIDR_VERSION_Pos) |

| (CHIPID_CIDR) Version of the Device More... | |

| #define | CHIPID_CIDR_VERSION_Pos 0 |

| #define | CHIPID_EXID_EXID_Msk (0xffffffffu << CHIPID_EXID_EXID_Pos) |

| (CHIPID_EXID) Chip ID Extension More... | |

| #define | CHIPID_EXID_EXID_Pos 0 |

Detailed Description

Copyright (c) 2015-2018 Microchip Technology Inc. and its subsidiaries.

Definition in file component/chipid.h.