This file provides firmware functions to manage the following functionalities of the Independent watchdog (IWDG) peripheral: More...

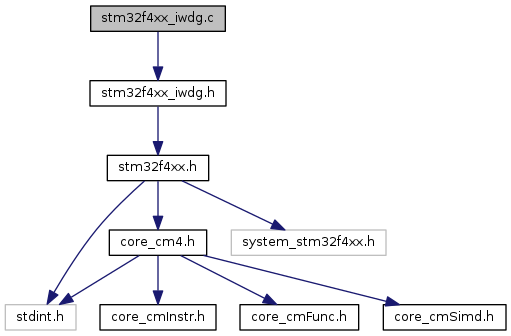

#include "stm32f4xx_iwdg.h"

Go to the source code of this file.

Macros | |

| #define | KR_KEY_ENABLE ((uint16_t)0xCCCC) |

| #define | KR_KEY_RELOAD ((uint16_t)0xAAAA) |

Functions | |

| void | IWDG_Enable (void) |

| Enables IWDG (write access to IWDG_PR and IWDG_RLR registers disabled). More... | |

| FlagStatus | IWDG_GetFlagStatus (uint16_t IWDG_FLAG) |

| Checks whether the specified IWDG flag is set or not. More... | |

| void | IWDG_ReloadCounter (void) |

| Reloads IWDG counter with value defined in the reload register (write access to IWDG_PR and IWDG_RLR registers disabled). More... | |

| void | IWDG_SetPrescaler (uint8_t IWDG_Prescaler) |

| Sets IWDG Prescaler value. More... | |

| void | IWDG_SetReload (uint16_t Reload) |

| Sets IWDG Reload value. More... | |

| void | IWDG_WriteAccessCmd (uint16_t IWDG_WriteAccess) |

| Enables or disables write access to IWDG_PR and IWDG_RLR registers. More... | |

Detailed Description

This file provides firmware functions to manage the following functionalities of the Independent watchdog (IWDG) peripheral:

- Version

- V1.1.0

- Date

- 11-January-2013

- Prescaler and Counter configuration

- IWDG activation

- Flag management

===============================================================================

##### IWDG features #####

===============================================================================

[..]

The IWDG can be started by either software or hardware (configurable

through option byte).

The IWDG is clocked by its own dedicated low-speed clock (LSI) and

thus stays active even if the main clock fails.

Once the IWDG is started, the LSI is forced ON and cannot be disabled

(LSI cannot be disabled too), and the counter starts counting down from

the reset value of 0xFFF. When it reaches the end of count value (0x000)

a system reset is generated.

The IWDG counter should be reloaded at regular intervals to prevent

an MCU reset.

The IWDG is implemented in the VDD voltage domain that is still functional

in STOP and STANDBY mode (IWDG reset can wake-up from STANDBY).

IWDGRST flag in RCC_CSR register can be used to inform when a IWDG

reset occurs.

Min-max timeout value @32KHz (LSI): ~125us / ~32.7s

The IWDG timeout may vary due to LSI frequency dispersion. STM32F4xx

devices provide the capability to measure the LSI frequency (LSI clock

connected internally to TIM5 CH4 input capture). The measured value

can be used to have an IWDG timeout with an acceptable accuracy.

For more information, please refer to the STM32F4xx Reference manual

##### How to use this driver #####

===============================================================================

[..]

(#) Enable write access to IWDG_PR and IWDG_RLR registers using

IWDG_WriteAccessCmd(IWDG_WriteAccess_Enable) function

(#) Configure the IWDG prescaler using IWDG_SetPrescaler() function

(#) Configure the IWDG counter value using IWDG_SetReload() function.

This value will be loaded in the IWDG counter each time the counter

is reloaded, then the IWDG will start counting down from this value.

(#) Start the IWDG using IWDG_Enable() function, when the IWDG is used

in software mode (no need to enable the LSI, it will be enabled

by hardware)

(#) Then the application program must reload the IWDG counter at regular

intervals during normal operation to prevent an MCU reset, using

IWDG_ReloadCounter() function. - Attention

© COPYRIGHT 2013 STMicroelectronics

Licensed under MCD-ST Liberty SW License Agreement V2, (the "License"); You may not use this file except in compliance with the License. You may obtain a copy of the License at:

http://www.st.com/software_license_agreement_liberty_v2

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Definition in file stm32f4xx_iwdg.c.