CMSIS Cortex-M3 Device Peripheral Access Layer Header File. This file contains all the peripheral register's definitions, bits definitions and memory mapping for STM32F10x Connectivity line, High density, High density value line, Medium density, Medium density Value line, Low density, Low density Value line and XL-density devices. More...

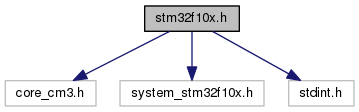

#include "core_cm3.h"#include "system_stm32f10x.h"#include <stdint.h>

Go to the source code of this file.

Classes | |

| struct | ADC_TypeDef |

| Analog to Digital Converter. More... | |

| struct | AFIO_TypeDef |

| Alternate Function I/O. More... | |

| struct | BKP_TypeDef |

| Backup Registers. More... | |

| struct | CAN_FIFOMailBox_TypeDef |

| Controller Area Network FIFOMailBox. More... | |

| struct | CAN_FilterRegister_TypeDef |

| Controller Area Network FilterRegister. More... | |

| struct | CAN_TxMailBox_TypeDef |

| Controller Area Network TxMailBox. More... | |

| struct | CAN_TypeDef |

| Controller Area Network. More... | |

| struct | CEC_TypeDef |

| Consumer Electronics Control (CEC) More... | |

| struct | CRC_TypeDef |

| CRC calculation unit. More... | |

| struct | DAC_TypeDef |

| Digital to Analog Converter. More... | |

| struct | DBGMCU_TypeDef |

| Debug MCU. More... | |

| struct | DMA_Channel_TypeDef |

| DMA Controller. More... | |

| struct | DMA_TypeDef |

| struct | ETH_TypeDef |

| Ethernet MAC. More... | |

| struct | EXTI_TypeDef |

| External Interrupt/Event Controller. More... | |

| struct | FLASH_TypeDef |

| FLASH Registers. More... | |

| struct | FSMC_Bank1_TypeDef |

| Flexible Static Memory Controller. More... | |

| struct | FSMC_Bank1E_TypeDef |

| Flexible Static Memory Controller Bank1E. More... | |

| struct | FSMC_Bank2_TypeDef |

| Flexible Static Memory Controller Bank2. More... | |

| struct | FSMC_Bank3_TypeDef |

| Flexible Static Memory Controller Bank3. More... | |

| struct | FSMC_Bank4_TypeDef |

| Flexible Static Memory Controller Bank4. More... | |

| struct | GPIO_TypeDef |

| General Purpose I/O. More... | |

| struct | I2C_TypeDef |

| Inter Integrated Circuit Interface. More... | |

| struct | IWDG_TypeDef |

| Independent WATCHDOG. More... | |

| struct | OB_TypeDef |

| Option Bytes Registers. More... | |

| struct | PWR_TypeDef |

| Power Control. More... | |

| struct | RCC_TypeDef |

| Reset and Clock Control. More... | |

| struct | RTC_TypeDef |

| Real-Time Clock. More... | |

| struct | SDIO_TypeDef |

| SD host Interface. More... | |

| struct | SPI_TypeDef |

| Serial Peripheral Interface. More... | |

| struct | TIM_TypeDef |

| TIM. More... | |

| struct | USART_TypeDef |

| Universal Synchronous Asynchronous Receiver Transmitter. More... | |

| struct | WWDG_TypeDef |

| Window WATCHDOG. More... | |

Defines | |

| #define | __MPU_PRESENT 0 |

| Configuration of the Cortex-M3 Processor and Core Peripherals. | |

| #define | __NVIC_PRIO_BITS 4 |

| #define | __STM32F10X_STDPERIPH_VERSION |

| #define | __STM32F10X_STDPERIPH_VERSION_MAIN (0x03) |

| STM32F10x Standard Peripheral Library version number. | |

| #define | __STM32F10X_STDPERIPH_VERSION_RC (0x00) |

| #define | __STM32F10X_STDPERIPH_VERSION_SUB1 (0x05) |

| #define | __STM32F10X_STDPERIPH_VERSION_SUB2 (0x00) |

| #define | __Vendor_SysTickConfig 0 |

| #define | ADC1 ((ADC_TypeDef *) ADC1_BASE) |

| #define | ADC1_BASE (APB2PERIPH_BASE + 0x2400) |

| #define | ADC2 ((ADC_TypeDef *) ADC2_BASE) |

| #define | ADC2_BASE (APB2PERIPH_BASE + 0x2800) |

| #define | ADC3 ((ADC_TypeDef *) ADC3_BASE) |

| #define | ADC3_BASE (APB2PERIPH_BASE + 0x3C00) |

| #define | ADC_CR1_AWDCH ((uint32_t)0x0000001F) |

| #define | ADC_CR1_AWDCH_0 ((uint32_t)0x00000001) |

| #define | ADC_CR1_AWDCH_1 ((uint32_t)0x00000002) |

| #define | ADC_CR1_AWDCH_2 ((uint32_t)0x00000004) |

| #define | ADC_CR1_AWDCH_3 ((uint32_t)0x00000008) |

| #define | ADC_CR1_AWDCH_4 ((uint32_t)0x00000010) |

| #define | ADC_CR1_AWDEN ((uint32_t)0x00800000) |

| #define | ADC_CR1_AWDIE ((uint32_t)0x00000040) |

| #define | ADC_CR1_AWDSGL ((uint32_t)0x00000200) |

| #define | ADC_CR1_DISCEN ((uint32_t)0x00000800) |

| #define | ADC_CR1_DISCNUM ((uint32_t)0x0000E000) |

| #define | ADC_CR1_DISCNUM_0 ((uint32_t)0x00002000) |

| #define | ADC_CR1_DISCNUM_1 ((uint32_t)0x00004000) |

| #define | ADC_CR1_DISCNUM_2 ((uint32_t)0x00008000) |

| #define | ADC_CR1_DUALMOD ((uint32_t)0x000F0000) |

| #define | ADC_CR1_DUALMOD_0 ((uint32_t)0x00010000) |

| #define | ADC_CR1_DUALMOD_1 ((uint32_t)0x00020000) |

| #define | ADC_CR1_DUALMOD_2 ((uint32_t)0x00040000) |

| #define | ADC_CR1_DUALMOD_3 ((uint32_t)0x00080000) |

| #define | ADC_CR1_EOCIE ((uint32_t)0x00000020) |

| #define | ADC_CR1_JAUTO ((uint32_t)0x00000400) |

| #define | ADC_CR1_JAWDEN ((uint32_t)0x00400000) |

| #define | ADC_CR1_JDISCEN ((uint32_t)0x00001000) |

| #define | ADC_CR1_JEOCIE ((uint32_t)0x00000080) |

| #define | ADC_CR1_SCAN ((uint32_t)0x00000100) |

| #define | ADC_CR2_ADON ((uint32_t)0x00000001) |

| #define | ADC_CR2_ALIGN ((uint32_t)0x00000800) |

| #define | ADC_CR2_CAL ((uint32_t)0x00000004) |

| #define | ADC_CR2_CONT ((uint32_t)0x00000002) |

| #define | ADC_CR2_DMA ((uint32_t)0x00000100) |

| #define | ADC_CR2_EXTSEL ((uint32_t)0x000E0000) |

| #define | ADC_CR2_EXTSEL_0 ((uint32_t)0x00020000) |

| #define | ADC_CR2_EXTSEL_1 ((uint32_t)0x00040000) |

| #define | ADC_CR2_EXTSEL_2 ((uint32_t)0x00080000) |

| #define | ADC_CR2_EXTTRIG ((uint32_t)0x00100000) |

| #define | ADC_CR2_JEXTSEL ((uint32_t)0x00007000) |

| #define | ADC_CR2_JEXTSEL_0 ((uint32_t)0x00001000) |

| #define | ADC_CR2_JEXTSEL_1 ((uint32_t)0x00002000) |

| #define | ADC_CR2_JEXTSEL_2 ((uint32_t)0x00004000) |

| #define | ADC_CR2_JEXTTRIG ((uint32_t)0x00008000) |

| #define | ADC_CR2_JSWSTART ((uint32_t)0x00200000) |

| #define | ADC_CR2_RSTCAL ((uint32_t)0x00000008) |

| #define | ADC_CR2_SWSTART ((uint32_t)0x00400000) |

| #define | ADC_CR2_TSVREFE ((uint32_t)0x00800000) |

| #define | ADC_DR_ADC2DATA ((uint32_t)0xFFFF0000) |

| #define | ADC_DR_DATA ((uint32_t)0x0000FFFF) |

| #define | ADC_HTR_HT ((uint16_t)0x0FFF) |

| #define | ADC_JDR1_JDATA ((uint16_t)0xFFFF) |

| #define | ADC_JDR2_JDATA ((uint16_t)0xFFFF) |

| #define | ADC_JDR3_JDATA ((uint16_t)0xFFFF) |

| #define | ADC_JDR4_JDATA ((uint16_t)0xFFFF) |

| #define | ADC_JOFR1_JOFFSET1 ((uint16_t)0x0FFF) |

| #define | ADC_JOFR2_JOFFSET2 ((uint16_t)0x0FFF) |

| #define | ADC_JOFR3_JOFFSET3 ((uint16_t)0x0FFF) |

| #define | ADC_JOFR4_JOFFSET4 ((uint16_t)0x0FFF) |

| #define | ADC_JSQR_JL ((uint32_t)0x00300000) |

| #define | ADC_JSQR_JL_0 ((uint32_t)0x00100000) |

| #define | ADC_JSQR_JL_1 ((uint32_t)0x00200000) |

| #define | ADC_JSQR_JSQ1 ((uint32_t)0x0000001F) |

| #define | ADC_JSQR_JSQ1_0 ((uint32_t)0x00000001) |

| #define | ADC_JSQR_JSQ1_1 ((uint32_t)0x00000002) |

| #define | ADC_JSQR_JSQ1_2 ((uint32_t)0x00000004) |

| #define | ADC_JSQR_JSQ1_3 ((uint32_t)0x00000008) |

| #define | ADC_JSQR_JSQ1_4 ((uint32_t)0x00000010) |

| #define | ADC_JSQR_JSQ2 ((uint32_t)0x000003E0) |

| #define | ADC_JSQR_JSQ2_0 ((uint32_t)0x00000020) |

| #define | ADC_JSQR_JSQ2_1 ((uint32_t)0x00000040) |

| #define | ADC_JSQR_JSQ2_2 ((uint32_t)0x00000080) |

| #define | ADC_JSQR_JSQ2_3 ((uint32_t)0x00000100) |

| #define | ADC_JSQR_JSQ2_4 ((uint32_t)0x00000200) |

| #define | ADC_JSQR_JSQ3 ((uint32_t)0x00007C00) |

| #define | ADC_JSQR_JSQ3_0 ((uint32_t)0x00000400) |

| #define | ADC_JSQR_JSQ3_1 ((uint32_t)0x00000800) |

| #define | ADC_JSQR_JSQ3_2 ((uint32_t)0x00001000) |

| #define | ADC_JSQR_JSQ3_3 ((uint32_t)0x00002000) |

| #define | ADC_JSQR_JSQ3_4 ((uint32_t)0x00004000) |

| #define | ADC_JSQR_JSQ4 ((uint32_t)0x000F8000) |

| #define | ADC_JSQR_JSQ4_0 ((uint32_t)0x00008000) |

| #define | ADC_JSQR_JSQ4_1 ((uint32_t)0x00010000) |

| #define | ADC_JSQR_JSQ4_2 ((uint32_t)0x00020000) |

| #define | ADC_JSQR_JSQ4_3 ((uint32_t)0x00040000) |

| #define | ADC_JSQR_JSQ4_4 ((uint32_t)0x00080000) |

| #define | ADC_LTR_LT ((uint16_t)0x0FFF) |

| #define | ADC_SMPR1_SMP10 ((uint32_t)0x00000007) |

| #define | ADC_SMPR1_SMP10_0 ((uint32_t)0x00000001) |

| #define | ADC_SMPR1_SMP10_1 ((uint32_t)0x00000002) |

| #define | ADC_SMPR1_SMP10_2 ((uint32_t)0x00000004) |

| #define | ADC_SMPR1_SMP11 ((uint32_t)0x00000038) |

| #define | ADC_SMPR1_SMP11_0 ((uint32_t)0x00000008) |

| #define | ADC_SMPR1_SMP11_1 ((uint32_t)0x00000010) |

| #define | ADC_SMPR1_SMP11_2 ((uint32_t)0x00000020) |

| #define | ADC_SMPR1_SMP12 ((uint32_t)0x000001C0) |

| #define | ADC_SMPR1_SMP12_0 ((uint32_t)0x00000040) |

| #define | ADC_SMPR1_SMP12_1 ((uint32_t)0x00000080) |

| #define | ADC_SMPR1_SMP12_2 ((uint32_t)0x00000100) |

| #define | ADC_SMPR1_SMP13 ((uint32_t)0x00000E00) |

| #define | ADC_SMPR1_SMP13_0 ((uint32_t)0x00000200) |

| #define | ADC_SMPR1_SMP13_1 ((uint32_t)0x00000400) |

| #define | ADC_SMPR1_SMP13_2 ((uint32_t)0x00000800) |

| #define | ADC_SMPR1_SMP14 ((uint32_t)0x00007000) |

| #define | ADC_SMPR1_SMP14_0 ((uint32_t)0x00001000) |

| #define | ADC_SMPR1_SMP14_1 ((uint32_t)0x00002000) |

| #define | ADC_SMPR1_SMP14_2 ((uint32_t)0x00004000) |

| #define | ADC_SMPR1_SMP15 ((uint32_t)0x00038000) |

| #define | ADC_SMPR1_SMP15_0 ((uint32_t)0x00008000) |

| #define | ADC_SMPR1_SMP15_1 ((uint32_t)0x00010000) |

| #define | ADC_SMPR1_SMP15_2 ((uint32_t)0x00020000) |

| #define | ADC_SMPR1_SMP16 ((uint32_t)0x001C0000) |

| #define | ADC_SMPR1_SMP16_0 ((uint32_t)0x00040000) |

| #define | ADC_SMPR1_SMP16_1 ((uint32_t)0x00080000) |

| #define | ADC_SMPR1_SMP16_2 ((uint32_t)0x00100000) |

| #define | ADC_SMPR1_SMP17 ((uint32_t)0x00E00000) |

| #define | ADC_SMPR1_SMP17_0 ((uint32_t)0x00200000) |

| #define | ADC_SMPR1_SMP17_1 ((uint32_t)0x00400000) |

| #define | ADC_SMPR1_SMP17_2 ((uint32_t)0x00800000) |

| #define | ADC_SMPR2_SMP0 ((uint32_t)0x00000007) |

| #define | ADC_SMPR2_SMP0_0 ((uint32_t)0x00000001) |

| #define | ADC_SMPR2_SMP0_1 ((uint32_t)0x00000002) |

| #define | ADC_SMPR2_SMP0_2 ((uint32_t)0x00000004) |

| #define | ADC_SMPR2_SMP1 ((uint32_t)0x00000038) |

| #define | ADC_SMPR2_SMP1_0 ((uint32_t)0x00000008) |

| #define | ADC_SMPR2_SMP1_1 ((uint32_t)0x00000010) |

| #define | ADC_SMPR2_SMP1_2 ((uint32_t)0x00000020) |

| #define | ADC_SMPR2_SMP2 ((uint32_t)0x000001C0) |

| #define | ADC_SMPR2_SMP2_0 ((uint32_t)0x00000040) |

| #define | ADC_SMPR2_SMP2_1 ((uint32_t)0x00000080) |

| #define | ADC_SMPR2_SMP2_2 ((uint32_t)0x00000100) |

| #define | ADC_SMPR2_SMP3 ((uint32_t)0x00000E00) |

| #define | ADC_SMPR2_SMP3_0 ((uint32_t)0x00000200) |

| #define | ADC_SMPR2_SMP3_1 ((uint32_t)0x00000400) |

| #define | ADC_SMPR2_SMP3_2 ((uint32_t)0x00000800) |

| #define | ADC_SMPR2_SMP4 ((uint32_t)0x00007000) |

| #define | ADC_SMPR2_SMP4_0 ((uint32_t)0x00001000) |

| #define | ADC_SMPR2_SMP4_1 ((uint32_t)0x00002000) |

| #define | ADC_SMPR2_SMP4_2 ((uint32_t)0x00004000) |

| #define | ADC_SMPR2_SMP5 ((uint32_t)0x00038000) |

| #define | ADC_SMPR2_SMP5_0 ((uint32_t)0x00008000) |

| #define | ADC_SMPR2_SMP5_1 ((uint32_t)0x00010000) |

| #define | ADC_SMPR2_SMP5_2 ((uint32_t)0x00020000) |

| #define | ADC_SMPR2_SMP6 ((uint32_t)0x001C0000) |

| #define | ADC_SMPR2_SMP6_0 ((uint32_t)0x00040000) |

| #define | ADC_SMPR2_SMP6_1 ((uint32_t)0x00080000) |

| #define | ADC_SMPR2_SMP6_2 ((uint32_t)0x00100000) |

| #define | ADC_SMPR2_SMP7 ((uint32_t)0x00E00000) |

| #define | ADC_SMPR2_SMP7_0 ((uint32_t)0x00200000) |

| #define | ADC_SMPR2_SMP7_1 ((uint32_t)0x00400000) |

| #define | ADC_SMPR2_SMP7_2 ((uint32_t)0x00800000) |

| #define | ADC_SMPR2_SMP8 ((uint32_t)0x07000000) |

| #define | ADC_SMPR2_SMP8_0 ((uint32_t)0x01000000) |

| #define | ADC_SMPR2_SMP8_1 ((uint32_t)0x02000000) |

| #define | ADC_SMPR2_SMP8_2 ((uint32_t)0x04000000) |

| #define | ADC_SMPR2_SMP9 ((uint32_t)0x38000000) |

| #define | ADC_SMPR2_SMP9_0 ((uint32_t)0x08000000) |

| #define | ADC_SMPR2_SMP9_1 ((uint32_t)0x10000000) |

| #define | ADC_SMPR2_SMP9_2 ((uint32_t)0x20000000) |

| #define | ADC_SQR1_L ((uint32_t)0x00F00000) |

| #define | ADC_SQR1_L_0 ((uint32_t)0x00100000) |

| #define | ADC_SQR1_L_1 ((uint32_t)0x00200000) |

| #define | ADC_SQR1_L_2 ((uint32_t)0x00400000) |

| #define | ADC_SQR1_L_3 ((uint32_t)0x00800000) |

| #define | ADC_SQR1_SQ13 ((uint32_t)0x0000001F) |

| #define | ADC_SQR1_SQ13_0 ((uint32_t)0x00000001) |

| #define | ADC_SQR1_SQ13_1 ((uint32_t)0x00000002) |

| #define | ADC_SQR1_SQ13_2 ((uint32_t)0x00000004) |

| #define | ADC_SQR1_SQ13_3 ((uint32_t)0x00000008) |

| #define | ADC_SQR1_SQ13_4 ((uint32_t)0x00000010) |

| #define | ADC_SQR1_SQ14 ((uint32_t)0x000003E0) |

| #define | ADC_SQR1_SQ14_0 ((uint32_t)0x00000020) |

| #define | ADC_SQR1_SQ14_1 ((uint32_t)0x00000040) |

| #define | ADC_SQR1_SQ14_2 ((uint32_t)0x00000080) |

| #define | ADC_SQR1_SQ14_3 ((uint32_t)0x00000100) |

| #define | ADC_SQR1_SQ14_4 ((uint32_t)0x00000200) |

| #define | ADC_SQR1_SQ15 ((uint32_t)0x00007C00) |

| #define | ADC_SQR1_SQ15_0 ((uint32_t)0x00000400) |

| #define | ADC_SQR1_SQ15_1 ((uint32_t)0x00000800) |

| #define | ADC_SQR1_SQ15_2 ((uint32_t)0x00001000) |

| #define | ADC_SQR1_SQ15_3 ((uint32_t)0x00002000) |

| #define | ADC_SQR1_SQ15_4 ((uint32_t)0x00004000) |

| #define | ADC_SQR1_SQ16 ((uint32_t)0x000F8000) |

| #define | ADC_SQR1_SQ16_0 ((uint32_t)0x00008000) |

| #define | ADC_SQR1_SQ16_1 ((uint32_t)0x00010000) |

| #define | ADC_SQR1_SQ16_2 ((uint32_t)0x00020000) |

| #define | ADC_SQR1_SQ16_3 ((uint32_t)0x00040000) |

| #define | ADC_SQR1_SQ16_4 ((uint32_t)0x00080000) |

| #define | ADC_SQR2_SQ10 ((uint32_t)0x000F8000) |

| #define | ADC_SQR2_SQ10_0 ((uint32_t)0x00008000) |

| #define | ADC_SQR2_SQ10_1 ((uint32_t)0x00010000) |

| #define | ADC_SQR2_SQ10_2 ((uint32_t)0x00020000) |

| #define | ADC_SQR2_SQ10_3 ((uint32_t)0x00040000) |

| #define | ADC_SQR2_SQ10_4 ((uint32_t)0x00080000) |

| #define | ADC_SQR2_SQ11 ((uint32_t)0x01F00000) |

| #define | ADC_SQR2_SQ11_0 ((uint32_t)0x00100000) |

| #define | ADC_SQR2_SQ11_1 ((uint32_t)0x00200000) |

| #define | ADC_SQR2_SQ11_2 ((uint32_t)0x00400000) |

| #define | ADC_SQR2_SQ11_3 ((uint32_t)0x00800000) |

| #define | ADC_SQR2_SQ11_4 ((uint32_t)0x01000000) |

| #define | ADC_SQR2_SQ12 ((uint32_t)0x3E000000) |

| #define | ADC_SQR2_SQ12_0 ((uint32_t)0x02000000) |

| #define | ADC_SQR2_SQ12_1 ((uint32_t)0x04000000) |

| #define | ADC_SQR2_SQ12_2 ((uint32_t)0x08000000) |

| #define | ADC_SQR2_SQ12_3 ((uint32_t)0x10000000) |

| #define | ADC_SQR2_SQ12_4 ((uint32_t)0x20000000) |

| #define | ADC_SQR2_SQ7 ((uint32_t)0x0000001F) |

| #define | ADC_SQR2_SQ7_0 ((uint32_t)0x00000001) |

| #define | ADC_SQR2_SQ7_1 ((uint32_t)0x00000002) |

| #define | ADC_SQR2_SQ7_2 ((uint32_t)0x00000004) |

| #define | ADC_SQR2_SQ7_3 ((uint32_t)0x00000008) |

| #define | ADC_SQR2_SQ7_4 ((uint32_t)0x00000010) |

| #define | ADC_SQR2_SQ8 ((uint32_t)0x000003E0) |

| #define | ADC_SQR2_SQ8_0 ((uint32_t)0x00000020) |

| #define | ADC_SQR2_SQ8_1 ((uint32_t)0x00000040) |

| #define | ADC_SQR2_SQ8_2 ((uint32_t)0x00000080) |

| #define | ADC_SQR2_SQ8_3 ((uint32_t)0x00000100) |

| #define | ADC_SQR2_SQ8_4 ((uint32_t)0x00000200) |

| #define | ADC_SQR2_SQ9 ((uint32_t)0x00007C00) |

| #define | ADC_SQR2_SQ9_0 ((uint32_t)0x00000400) |

| #define | ADC_SQR2_SQ9_1 ((uint32_t)0x00000800) |

| #define | ADC_SQR2_SQ9_2 ((uint32_t)0x00001000) |

| #define | ADC_SQR2_SQ9_3 ((uint32_t)0x00002000) |

| #define | ADC_SQR2_SQ9_4 ((uint32_t)0x00004000) |

| #define | ADC_SQR3_SQ1 ((uint32_t)0x0000001F) |

| #define | ADC_SQR3_SQ1_0 ((uint32_t)0x00000001) |

| #define | ADC_SQR3_SQ1_1 ((uint32_t)0x00000002) |

| #define | ADC_SQR3_SQ1_2 ((uint32_t)0x00000004) |

| #define | ADC_SQR3_SQ1_3 ((uint32_t)0x00000008) |

| #define | ADC_SQR3_SQ1_4 ((uint32_t)0x00000010) |

| #define | ADC_SQR3_SQ2 ((uint32_t)0x000003E0) |

| #define | ADC_SQR3_SQ2_0 ((uint32_t)0x00000020) |

| #define | ADC_SQR3_SQ2_1 ((uint32_t)0x00000040) |

| #define | ADC_SQR3_SQ2_2 ((uint32_t)0x00000080) |

| #define | ADC_SQR3_SQ2_3 ((uint32_t)0x00000100) |

| #define | ADC_SQR3_SQ2_4 ((uint32_t)0x00000200) |

| #define | ADC_SQR3_SQ3 ((uint32_t)0x00007C00) |

| #define | ADC_SQR3_SQ3_0 ((uint32_t)0x00000400) |

| #define | ADC_SQR3_SQ3_1 ((uint32_t)0x00000800) |

| #define | ADC_SQR3_SQ3_2 ((uint32_t)0x00001000) |

| #define | ADC_SQR3_SQ3_3 ((uint32_t)0x00002000) |

| #define | ADC_SQR3_SQ3_4 ((uint32_t)0x00004000) |

| #define | ADC_SQR3_SQ4 ((uint32_t)0x000F8000) |

| #define | ADC_SQR3_SQ4_0 ((uint32_t)0x00008000) |

| #define | ADC_SQR3_SQ4_1 ((uint32_t)0x00010000) |

| #define | ADC_SQR3_SQ4_2 ((uint32_t)0x00020000) |

| #define | ADC_SQR3_SQ4_3 ((uint32_t)0x00040000) |

| #define | ADC_SQR3_SQ4_4 ((uint32_t)0x00080000) |

| #define | ADC_SQR3_SQ5 ((uint32_t)0x01F00000) |

| #define | ADC_SQR3_SQ5_0 ((uint32_t)0x00100000) |

| #define | ADC_SQR3_SQ5_1 ((uint32_t)0x00200000) |

| #define | ADC_SQR3_SQ5_2 ((uint32_t)0x00400000) |

| #define | ADC_SQR3_SQ5_3 ((uint32_t)0x00800000) |

| #define | ADC_SQR3_SQ5_4 ((uint32_t)0x01000000) |

| #define | ADC_SQR3_SQ6 ((uint32_t)0x3E000000) |

| #define | ADC_SQR3_SQ6_0 ((uint32_t)0x02000000) |

| #define | ADC_SQR3_SQ6_1 ((uint32_t)0x04000000) |

| #define | ADC_SQR3_SQ6_2 ((uint32_t)0x08000000) |

| #define | ADC_SQR3_SQ6_3 ((uint32_t)0x10000000) |

| #define | ADC_SQR3_SQ6_4 ((uint32_t)0x20000000) |

| #define | ADC_SR_AWD ((uint8_t)0x01) |

| #define | ADC_SR_EOC ((uint8_t)0x02) |

| #define | ADC_SR_JEOC ((uint8_t)0x04) |

| #define | ADC_SR_JSTRT ((uint8_t)0x08) |

| #define | ADC_SR_STRT ((uint8_t)0x10) |

| #define | AFIO ((AFIO_TypeDef *) AFIO_BASE) |

| #define | AFIO_BASE (APB2PERIPH_BASE + 0x0000) |

| #define | AFIO_EVCR_EVOE ((uint8_t)0x80) |

| #define | AFIO_EVCR_PIN ((uint8_t)0x0F) |

| #define | AFIO_EVCR_PIN_0 ((uint8_t)0x01) |

| #define | AFIO_EVCR_PIN_1 ((uint8_t)0x02) |

| #define | AFIO_EVCR_PIN_2 ((uint8_t)0x04) |

| #define | AFIO_EVCR_PIN_3 ((uint8_t)0x08) |

| #define | AFIO_EVCR_PIN_PX0 ((uint8_t)0x00) |

| #define | AFIO_EVCR_PIN_PX1 ((uint8_t)0x01) |

| #define | AFIO_EVCR_PIN_PX10 ((uint8_t)0x0A) |

| #define | AFIO_EVCR_PIN_PX11 ((uint8_t)0x0B) |

| #define | AFIO_EVCR_PIN_PX12 ((uint8_t)0x0C) |

| #define | AFIO_EVCR_PIN_PX13 ((uint8_t)0x0D) |

| #define | AFIO_EVCR_PIN_PX14 ((uint8_t)0x0E) |

| #define | AFIO_EVCR_PIN_PX15 ((uint8_t)0x0F) |

| #define | AFIO_EVCR_PIN_PX2 ((uint8_t)0x02) |

| #define | AFIO_EVCR_PIN_PX3 ((uint8_t)0x03) |

| #define | AFIO_EVCR_PIN_PX4 ((uint8_t)0x04) |

| #define | AFIO_EVCR_PIN_PX5 ((uint8_t)0x05) |

| #define | AFIO_EVCR_PIN_PX6 ((uint8_t)0x06) |

| #define | AFIO_EVCR_PIN_PX7 ((uint8_t)0x07) |

| #define | AFIO_EVCR_PIN_PX8 ((uint8_t)0x08) |

| #define | AFIO_EVCR_PIN_PX9 ((uint8_t)0x09) |

| #define | AFIO_EVCR_PORT ((uint8_t)0x70) |

| #define | AFIO_EVCR_PORT_0 ((uint8_t)0x10) |

| #define | AFIO_EVCR_PORT_1 ((uint8_t)0x20) |

| #define | AFIO_EVCR_PORT_2 ((uint8_t)0x40) |

| #define | AFIO_EVCR_PORT_PA ((uint8_t)0x00) |

| #define | AFIO_EVCR_PORT_PB ((uint8_t)0x10) |

| #define | AFIO_EVCR_PORT_PC ((uint8_t)0x20) |

| #define | AFIO_EVCR_PORT_PD ((uint8_t)0x30) |

| #define | AFIO_EVCR_PORT_PE ((uint8_t)0x40) |

| #define | AFIO_EXTICR1_EXTI0 ((uint16_t)0x000F) |

| #define | AFIO_EXTICR1_EXTI0_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR1_EXTI0_PB ((uint16_t)0x0001) |

| #define | AFIO_EXTICR1_EXTI0_PC ((uint16_t)0x0002) |

| #define | AFIO_EXTICR1_EXTI0_PD ((uint16_t)0x0003) |

| #define | AFIO_EXTICR1_EXTI0_PE ((uint16_t)0x0004) |

| #define | AFIO_EXTICR1_EXTI0_PF ((uint16_t)0x0005) |

| #define | AFIO_EXTICR1_EXTI0_PG ((uint16_t)0x0006) |

| #define | AFIO_EXTICR1_EXTI1 ((uint16_t)0x00F0) |

| #define | AFIO_EXTICR1_EXTI1_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR1_EXTI1_PB ((uint16_t)0x0010) |

| #define | AFIO_EXTICR1_EXTI1_PC ((uint16_t)0x0020) |

| #define | AFIO_EXTICR1_EXTI1_PD ((uint16_t)0x0030) |

| #define | AFIO_EXTICR1_EXTI1_PE ((uint16_t)0x0040) |

| #define | AFIO_EXTICR1_EXTI1_PF ((uint16_t)0x0050) |

| #define | AFIO_EXTICR1_EXTI1_PG ((uint16_t)0x0060) |

| #define | AFIO_EXTICR1_EXTI2 ((uint16_t)0x0F00) |

| #define | AFIO_EXTICR1_EXTI2_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR1_EXTI2_PB ((uint16_t)0x0100) |

| #define | AFIO_EXTICR1_EXTI2_PC ((uint16_t)0x0200) |

| #define | AFIO_EXTICR1_EXTI2_PD ((uint16_t)0x0300) |

| #define | AFIO_EXTICR1_EXTI2_PE ((uint16_t)0x0400) |

| #define | AFIO_EXTICR1_EXTI2_PF ((uint16_t)0x0500) |

| #define | AFIO_EXTICR1_EXTI2_PG ((uint16_t)0x0600) |

| #define | AFIO_EXTICR1_EXTI3 ((uint16_t)0xF000) |

| #define | AFIO_EXTICR1_EXTI3_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR1_EXTI3_PB ((uint16_t)0x1000) |

| #define | AFIO_EXTICR1_EXTI3_PC ((uint16_t)0x2000) |

| #define | AFIO_EXTICR1_EXTI3_PD ((uint16_t)0x3000) |

| #define | AFIO_EXTICR1_EXTI3_PE ((uint16_t)0x4000) |

| #define | AFIO_EXTICR1_EXTI3_PF ((uint16_t)0x5000) |

| #define | AFIO_EXTICR1_EXTI3_PG ((uint16_t)0x6000) |

| #define | AFIO_EXTICR2_EXTI4 ((uint16_t)0x000F) |

| #define | AFIO_EXTICR2_EXTI4_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR2_EXTI4_PB ((uint16_t)0x0001) |

| #define | AFIO_EXTICR2_EXTI4_PC ((uint16_t)0x0002) |

| #define | AFIO_EXTICR2_EXTI4_PD ((uint16_t)0x0003) |

| #define | AFIO_EXTICR2_EXTI4_PE ((uint16_t)0x0004) |

| #define | AFIO_EXTICR2_EXTI4_PF ((uint16_t)0x0005) |

| #define | AFIO_EXTICR2_EXTI4_PG ((uint16_t)0x0006) |

| #define | AFIO_EXTICR2_EXTI5 ((uint16_t)0x00F0) |

| #define | AFIO_EXTICR2_EXTI5_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR2_EXTI5_PB ((uint16_t)0x0010) |

| #define | AFIO_EXTICR2_EXTI5_PC ((uint16_t)0x0020) |

| #define | AFIO_EXTICR2_EXTI5_PD ((uint16_t)0x0030) |

| #define | AFIO_EXTICR2_EXTI5_PE ((uint16_t)0x0040) |

| #define | AFIO_EXTICR2_EXTI5_PF ((uint16_t)0x0050) |

| #define | AFIO_EXTICR2_EXTI5_PG ((uint16_t)0x0060) |

| #define | AFIO_EXTICR2_EXTI6 ((uint16_t)0x0F00) |

| #define | AFIO_EXTICR2_EXTI6_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR2_EXTI6_PB ((uint16_t)0x0100) |

| #define | AFIO_EXTICR2_EXTI6_PC ((uint16_t)0x0200) |

| #define | AFIO_EXTICR2_EXTI6_PD ((uint16_t)0x0300) |

| #define | AFIO_EXTICR2_EXTI6_PE ((uint16_t)0x0400) |

| #define | AFIO_EXTICR2_EXTI6_PF ((uint16_t)0x0500) |

| #define | AFIO_EXTICR2_EXTI6_PG ((uint16_t)0x0600) |

| #define | AFIO_EXTICR2_EXTI7 ((uint16_t)0xF000) |

| #define | AFIO_EXTICR2_EXTI7_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR2_EXTI7_PB ((uint16_t)0x1000) |

| #define | AFIO_EXTICR2_EXTI7_PC ((uint16_t)0x2000) |

| #define | AFIO_EXTICR2_EXTI7_PD ((uint16_t)0x3000) |

| #define | AFIO_EXTICR2_EXTI7_PE ((uint16_t)0x4000) |

| #define | AFIO_EXTICR2_EXTI7_PF ((uint16_t)0x5000) |

| #define | AFIO_EXTICR2_EXTI7_PG ((uint16_t)0x6000) |

| #define | AFIO_EXTICR3_EXTI10 ((uint16_t)0x0F00) |

| #define | AFIO_EXTICR3_EXTI10_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR3_EXTI10_PB ((uint16_t)0x0100) |

| #define | AFIO_EXTICR3_EXTI10_PC ((uint16_t)0x0200) |

| #define | AFIO_EXTICR3_EXTI10_PD ((uint16_t)0x0300) |

| #define | AFIO_EXTICR3_EXTI10_PE ((uint16_t)0x0400) |

| #define | AFIO_EXTICR3_EXTI10_PF ((uint16_t)0x0500) |

| #define | AFIO_EXTICR3_EXTI10_PG ((uint16_t)0x0600) |

| #define | AFIO_EXTICR3_EXTI11 ((uint16_t)0xF000) |

| #define | AFIO_EXTICR3_EXTI11_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR3_EXTI11_PB ((uint16_t)0x1000) |

| #define | AFIO_EXTICR3_EXTI11_PC ((uint16_t)0x2000) |

| #define | AFIO_EXTICR3_EXTI11_PD ((uint16_t)0x3000) |

| #define | AFIO_EXTICR3_EXTI11_PE ((uint16_t)0x4000) |

| #define | AFIO_EXTICR3_EXTI11_PF ((uint16_t)0x5000) |

| #define | AFIO_EXTICR3_EXTI11_PG ((uint16_t)0x6000) |

| #define | AFIO_EXTICR3_EXTI8 ((uint16_t)0x000F) |

| #define | AFIO_EXTICR3_EXTI8_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR3_EXTI8_PB ((uint16_t)0x0001) |

| #define | AFIO_EXTICR3_EXTI8_PC ((uint16_t)0x0002) |

| #define | AFIO_EXTICR3_EXTI8_PD ((uint16_t)0x0003) |

| #define | AFIO_EXTICR3_EXTI8_PE ((uint16_t)0x0004) |

| #define | AFIO_EXTICR3_EXTI8_PF ((uint16_t)0x0005) |

| #define | AFIO_EXTICR3_EXTI8_PG ((uint16_t)0x0006) |

| #define | AFIO_EXTICR3_EXTI9 ((uint16_t)0x00F0) |

| #define | AFIO_EXTICR3_EXTI9_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR3_EXTI9_PB ((uint16_t)0x0010) |

| #define | AFIO_EXTICR3_EXTI9_PC ((uint16_t)0x0020) |

| #define | AFIO_EXTICR3_EXTI9_PD ((uint16_t)0x0030) |

| #define | AFIO_EXTICR3_EXTI9_PE ((uint16_t)0x0040) |

| #define | AFIO_EXTICR3_EXTI9_PF ((uint16_t)0x0050) |

| #define | AFIO_EXTICR3_EXTI9_PG ((uint16_t)0x0060) |

| #define | AFIO_EXTICR4_EXTI12 ((uint16_t)0x000F) |

| #define | AFIO_EXTICR4_EXTI12_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR4_EXTI12_PB ((uint16_t)0x0001) |

| #define | AFIO_EXTICR4_EXTI12_PC ((uint16_t)0x0002) |

| #define | AFIO_EXTICR4_EXTI12_PD ((uint16_t)0x0003) |

| #define | AFIO_EXTICR4_EXTI12_PE ((uint16_t)0x0004) |

| #define | AFIO_EXTICR4_EXTI12_PF ((uint16_t)0x0005) |

| #define | AFIO_EXTICR4_EXTI12_PG ((uint16_t)0x0006) |

| #define | AFIO_EXTICR4_EXTI13 ((uint16_t)0x00F0) |

| #define | AFIO_EXTICR4_EXTI13_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR4_EXTI13_PB ((uint16_t)0x0010) |

| #define | AFIO_EXTICR4_EXTI13_PC ((uint16_t)0x0020) |

| #define | AFIO_EXTICR4_EXTI13_PD ((uint16_t)0x0030) |

| #define | AFIO_EXTICR4_EXTI13_PE ((uint16_t)0x0040) |

| #define | AFIO_EXTICR4_EXTI13_PF ((uint16_t)0x0050) |

| #define | AFIO_EXTICR4_EXTI13_PG ((uint16_t)0x0060) |

| #define | AFIO_EXTICR4_EXTI14 ((uint16_t)0x0F00) |

| #define | AFIO_EXTICR4_EXTI14_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR4_EXTI14_PB ((uint16_t)0x0100) |

| #define | AFIO_EXTICR4_EXTI14_PC ((uint16_t)0x0200) |

| #define | AFIO_EXTICR4_EXTI14_PD ((uint16_t)0x0300) |

| #define | AFIO_EXTICR4_EXTI14_PE ((uint16_t)0x0400) |

| #define | AFIO_EXTICR4_EXTI14_PF ((uint16_t)0x0500) |

| #define | AFIO_EXTICR4_EXTI14_PG ((uint16_t)0x0600) |

| #define | AFIO_EXTICR4_EXTI15 ((uint16_t)0xF000) |

| #define | AFIO_EXTICR4_EXTI15_PA ((uint16_t)0x0000) |

| #define | AFIO_EXTICR4_EXTI15_PB ((uint16_t)0x1000) |

| #define | AFIO_EXTICR4_EXTI15_PC ((uint16_t)0x2000) |

| #define | AFIO_EXTICR4_EXTI15_PD ((uint16_t)0x3000) |

| #define | AFIO_EXTICR4_EXTI15_PE ((uint16_t)0x4000) |

| #define | AFIO_EXTICR4_EXTI15_PF ((uint16_t)0x5000) |

| #define | AFIO_EXTICR4_EXTI15_PG ((uint16_t)0x6000) |

| #define | AFIO_MAPR_ADC1_ETRGINJ_REMAP ((uint32_t)0x00020000) |

| #define | AFIO_MAPR_ADC1_ETRGREG_REMAP ((uint32_t)0x00040000) |

| #define | AFIO_MAPR_ADC2_ETRGINJ_REMAP ((uint32_t)0x00080000) |

| #define | AFIO_MAPR_ADC2_ETRGREG_REMAP ((uint32_t)0x00100000) |

| #define | AFIO_MAPR_CAN_REMAP ((uint32_t)0x00006000) |

| #define | AFIO_MAPR_CAN_REMAP_0 ((uint32_t)0x00002000) |

| #define | AFIO_MAPR_CAN_REMAP_1 ((uint32_t)0x00004000) |

| #define | AFIO_MAPR_CAN_REMAP_REMAP1 ((uint32_t)0x00000000) |

| #define | AFIO_MAPR_CAN_REMAP_REMAP2 ((uint32_t)0x00004000) |

| #define | AFIO_MAPR_CAN_REMAP_REMAP3 ((uint32_t)0x00006000) |

| #define | AFIO_MAPR_I2C1_REMAP ((uint32_t)0x00000002) |

| #define | AFIO_MAPR_PD01_REMAP ((uint32_t)0x00008000) |

| #define | AFIO_MAPR_SPI1_REMAP ((uint32_t)0x00000001) |

| #define | AFIO_MAPR_SWJ_CFG ((uint32_t)0x07000000) |

| #define | AFIO_MAPR_SWJ_CFG_0 ((uint32_t)0x01000000) |

| #define | AFIO_MAPR_SWJ_CFG_1 ((uint32_t)0x02000000) |

| #define | AFIO_MAPR_SWJ_CFG_2 ((uint32_t)0x04000000) |

| #define | AFIO_MAPR_SWJ_CFG_DISABLE ((uint32_t)0x04000000) |

| #define | AFIO_MAPR_SWJ_CFG_JTAGDISABLE ((uint32_t)0x02000000) |

| #define | AFIO_MAPR_SWJ_CFG_NOJNTRST ((uint32_t)0x01000000) |

| #define | AFIO_MAPR_SWJ_CFG_RESET ((uint32_t)0x00000000) |

| #define | AFIO_MAPR_TIM1_REMAP ((uint32_t)0x000000C0) |

| #define | AFIO_MAPR_TIM1_REMAP_0 ((uint32_t)0x00000040) |

| #define | AFIO_MAPR_TIM1_REMAP_1 ((uint32_t)0x00000080) |

| #define | AFIO_MAPR_TIM1_REMAP_FULLREMAP ((uint32_t)0x000000C0) |

| #define | AFIO_MAPR_TIM1_REMAP_NOREMAP ((uint32_t)0x00000000) |

| #define | AFIO_MAPR_TIM1_REMAP_PARTIALREMAP ((uint32_t)0x00000040) |

| #define | AFIO_MAPR_TIM2_REMAP ((uint32_t)0x00000300) |

| #define | AFIO_MAPR_TIM2_REMAP_0 ((uint32_t)0x00000100) |

| #define | AFIO_MAPR_TIM2_REMAP_1 ((uint32_t)0x00000200) |

| #define | AFIO_MAPR_TIM2_REMAP_FULLREMAP ((uint32_t)0x00000300) |

| #define | AFIO_MAPR_TIM2_REMAP_NOREMAP ((uint32_t)0x00000000) |

| #define | AFIO_MAPR_TIM2_REMAP_PARTIALREMAP1 ((uint32_t)0x00000100) |

| #define | AFIO_MAPR_TIM2_REMAP_PARTIALREMAP2 ((uint32_t)0x00000200) |

| #define | AFIO_MAPR_TIM3_REMAP ((uint32_t)0x00000C00) |

| #define | AFIO_MAPR_TIM3_REMAP_0 ((uint32_t)0x00000400) |

| #define | AFIO_MAPR_TIM3_REMAP_1 ((uint32_t)0x00000800) |

| #define | AFIO_MAPR_TIM3_REMAP_FULLREMAP ((uint32_t)0x00000C00) |

| #define | AFIO_MAPR_TIM3_REMAP_NOREMAP ((uint32_t)0x00000000) |

| #define | AFIO_MAPR_TIM3_REMAP_PARTIALREMAP ((uint32_t)0x00000800) |

| #define | AFIO_MAPR_TIM4_REMAP ((uint32_t)0x00001000) |

| #define | AFIO_MAPR_TIM5CH4_IREMAP ((uint32_t)0x00010000) |

| #define | AFIO_MAPR_USART1_REMAP ((uint32_t)0x00000004) |

| #define | AFIO_MAPR_USART2_REMAP ((uint32_t)0x00000008) |

| #define | AFIO_MAPR_USART3_REMAP ((uint32_t)0x00000030) |

| #define | AFIO_MAPR_USART3_REMAP_0 ((uint32_t)0x00000010) |

| #define | AFIO_MAPR_USART3_REMAP_1 ((uint32_t)0x00000020) |

| #define | AFIO_MAPR_USART3_REMAP_FULLREMAP ((uint32_t)0x00000030) |

| #define | AFIO_MAPR_USART3_REMAP_NOREMAP ((uint32_t)0x00000000) |

| #define | AFIO_MAPR_USART3_REMAP_PARTIALREMAP ((uint32_t)0x00000010) |

| #define | AHBPERIPH_BASE (PERIPH_BASE + 0x20000) |

| #define | APB1PERIPH_BASE PERIPH_BASE |

| #define | APB2PERIPH_BASE (PERIPH_BASE + 0x10000) |

| #define | BKP ((BKP_TypeDef *) BKP_BASE) |

| #define | BKP_BASE (APB1PERIPH_BASE + 0x6C00) |

| #define | BKP_CR_TPAL ((uint8_t)0x02) |

| #define | BKP_CR_TPE ((uint8_t)0x01) |

| #define | BKP_CSR_CTE ((uint16_t)0x0001) |

| #define | BKP_CSR_CTI ((uint16_t)0x0002) |

| #define | BKP_CSR_TEF ((uint16_t)0x0100) |

| #define | BKP_CSR_TIF ((uint16_t)0x0200) |

| #define | BKP_CSR_TPIE ((uint16_t)0x0004) |

| #define | BKP_DR10_D ((uint16_t)0xFFFF) |

| #define | BKP_DR11_D ((uint16_t)0xFFFF) |

| #define | BKP_DR12_D ((uint16_t)0xFFFF) |

| #define | BKP_DR13_D ((uint16_t)0xFFFF) |

| #define | BKP_DR14_D ((uint16_t)0xFFFF) |

| #define | BKP_DR15_D ((uint16_t)0xFFFF) |

| #define | BKP_DR16_D ((uint16_t)0xFFFF) |

| #define | BKP_DR17_D ((uint16_t)0xFFFF) |

| #define | BKP_DR18_D ((uint16_t)0xFFFF) |

| #define | BKP_DR19_D ((uint16_t)0xFFFF) |

| #define | BKP_DR1_D ((uint16_t)0xFFFF) |

| #define | BKP_DR20_D ((uint16_t)0xFFFF) |

| #define | BKP_DR21_D ((uint16_t)0xFFFF) |

| #define | BKP_DR22_D ((uint16_t)0xFFFF) |

| #define | BKP_DR23_D ((uint16_t)0xFFFF) |

| #define | BKP_DR24_D ((uint16_t)0xFFFF) |

| #define | BKP_DR25_D ((uint16_t)0xFFFF) |

| #define | BKP_DR26_D ((uint16_t)0xFFFF) |

| #define | BKP_DR27_D ((uint16_t)0xFFFF) |

| #define | BKP_DR28_D ((uint16_t)0xFFFF) |

| #define | BKP_DR29_D ((uint16_t)0xFFFF) |

| #define | BKP_DR2_D ((uint16_t)0xFFFF) |

| #define | BKP_DR30_D ((uint16_t)0xFFFF) |

| #define | BKP_DR31_D ((uint16_t)0xFFFF) |

| #define | BKP_DR32_D ((uint16_t)0xFFFF) |

| #define | BKP_DR33_D ((uint16_t)0xFFFF) |

| #define | BKP_DR34_D ((uint16_t)0xFFFF) |

| #define | BKP_DR35_D ((uint16_t)0xFFFF) |

| #define | BKP_DR36_D ((uint16_t)0xFFFF) |

| #define | BKP_DR37_D ((uint16_t)0xFFFF) |

| #define | BKP_DR38_D ((uint16_t)0xFFFF) |

| #define | BKP_DR39_D ((uint16_t)0xFFFF) |

| #define | BKP_DR3_D ((uint16_t)0xFFFF) |

| #define | BKP_DR40_D ((uint16_t)0xFFFF) |

| #define | BKP_DR41_D ((uint16_t)0xFFFF) |

| #define | BKP_DR42_D ((uint16_t)0xFFFF) |

| #define | BKP_DR4_D ((uint16_t)0xFFFF) |

| #define | BKP_DR5_D ((uint16_t)0xFFFF) |

| #define | BKP_DR6_D ((uint16_t)0xFFFF) |

| #define | BKP_DR7_D ((uint16_t)0xFFFF) |

| #define | BKP_DR8_D ((uint16_t)0xFFFF) |

| #define | BKP_DR9_D ((uint16_t)0xFFFF) |

| #define | BKP_RTCCR_ASOE ((uint16_t)0x0100) |

| #define | BKP_RTCCR_ASOS ((uint16_t)0x0200) |

| #define | BKP_RTCCR_CAL ((uint16_t)0x007F) |

| #define | BKP_RTCCR_CCO ((uint16_t)0x0080) |

| #define | CAN1 ((CAN_TypeDef *) CAN1_BASE) |

| #define | CAN1_BASE (APB1PERIPH_BASE + 0x6400) |

| #define | CAN2 ((CAN_TypeDef *) CAN2_BASE) |

| #define | CAN2_BASE (APB1PERIPH_BASE + 0x6800) |

| #define | CAN_BTR_BRP ((uint32_t)0x000003FF) |

| #define | CAN_BTR_LBKM ((uint32_t)0x40000000) |

| #define | CAN_BTR_SILM ((uint32_t)0x80000000) |

| #define | CAN_BTR_SJW ((uint32_t)0x03000000) |

| #define | CAN_BTR_TS1 ((uint32_t)0x000F0000) |

| #define | CAN_BTR_TS2 ((uint32_t)0x00700000) |

| #define | CAN_ESR_BOFF ((uint32_t)0x00000004) |

| #define | CAN_ESR_EPVF ((uint32_t)0x00000002) |

| #define | CAN_ESR_EWGF ((uint32_t)0x00000001) |

| #define | CAN_ESR_LEC ((uint32_t)0x00000070) |

| #define | CAN_ESR_LEC_0 ((uint32_t)0x00000010) |

| #define | CAN_ESR_LEC_1 ((uint32_t)0x00000020) |

| #define | CAN_ESR_LEC_2 ((uint32_t)0x00000040) |

| #define | CAN_ESR_REC ((uint32_t)0xFF000000) |

| #define | CAN_ESR_TEC ((uint32_t)0x00FF0000) |

| #define | CAN_F0R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F0R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F0R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F0R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F0R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F0R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F0R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F0R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F0R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F0R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F0R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F0R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F0R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F0R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F0R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F0R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F0R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F0R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F0R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F0R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F0R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F0R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F0R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F0R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F0R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F0R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F0R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F0R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F0R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F0R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F0R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F0R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F0R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F0R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F0R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F0R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F0R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F0R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F0R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F0R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F0R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F0R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F0R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F0R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F0R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F0R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F0R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F0R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F0R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F0R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F0R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F0R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F0R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F0R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F0R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F0R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F0R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F0R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F0R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F0R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F0R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F0R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F0R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F0R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F10R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F10R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F10R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F10R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F10R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F10R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F10R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F10R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F10R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F10R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F10R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F10R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F10R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F10R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F10R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F10R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F10R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F10R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F10R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F10R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F10R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F10R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F10R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F10R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F10R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F10R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F10R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F10R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F10R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F10R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F10R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F10R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F10R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F10R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F10R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F10R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F10R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F10R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F10R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F10R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F10R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F10R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F10R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F10R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F10R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F10R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F10R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F10R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F10R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F10R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F10R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F10R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F10R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F10R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F10R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F10R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F10R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F10R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F10R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F10R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F10R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F10R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F10R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F10R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F11R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F11R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F11R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F11R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F11R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F11R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F11R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F11R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F11R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F11R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F11R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F11R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F11R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F11R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F11R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F11R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F11R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F11R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F11R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F11R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F11R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F11R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F11R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F11R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F11R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F11R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F11R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F11R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F11R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F11R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F11R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F11R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F11R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F11R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F11R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F11R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F11R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F11R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F11R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F11R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F11R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F11R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F11R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F11R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F11R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F11R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F11R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F11R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F11R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F11R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F11R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F11R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F11R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F11R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F11R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F11R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F11R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F11R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F11R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F11R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F11R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F11R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F11R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F11R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F12R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F12R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F12R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F12R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F12R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F12R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F12R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F12R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F12R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F12R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F12R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F12R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F12R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F12R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F12R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F12R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F12R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F12R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F12R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F12R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F12R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F12R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F12R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F12R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F12R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F12R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F12R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F12R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F12R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F12R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F12R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F12R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F12R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F12R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F12R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F12R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F12R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F12R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F12R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F12R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F12R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F12R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F12R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F12R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F12R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F12R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F12R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F12R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F12R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F12R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F12R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F12R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F12R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F12R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F12R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F12R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F12R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F12R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F12R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F12R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F12R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F12R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F12R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F12R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F13R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F13R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F13R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F13R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F13R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F13R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F13R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F13R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F13R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F13R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F13R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F13R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F13R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F13R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F13R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F13R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F13R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F13R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F13R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F13R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F13R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F13R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F13R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F13R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F13R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F13R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F13R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F13R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F13R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F13R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F13R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F13R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F13R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F13R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F13R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F13R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F13R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F13R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F13R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F13R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F13R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F13R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F13R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F13R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F13R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F13R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F13R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F13R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F13R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F13R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F13R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F13R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F13R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F13R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F13R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F13R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F13R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F13R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F13R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F13R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F13R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F13R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F13R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F13R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F1R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F1R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F1R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F1R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F1R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F1R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F1R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F1R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F1R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F1R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F1R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F1R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F1R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F1R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F1R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F1R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F1R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F1R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F1R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F1R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F1R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F1R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F1R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F1R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F1R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F1R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F1R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F1R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F1R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F1R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F1R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F1R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F1R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F1R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F1R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F1R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F1R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F1R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F1R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F1R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F1R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F1R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F1R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F1R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F1R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F1R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F1R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F1R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F1R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F1R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F1R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F1R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F1R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F1R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F1R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F1R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F1R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F1R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F1R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F1R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F1R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F1R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F1R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F1R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F2R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F2R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F2R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F2R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F2R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F2R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F2R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F2R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F2R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F2R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F2R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F2R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F2R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F2R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F2R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F2R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F2R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F2R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F2R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F2R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F2R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F2R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F2R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F2R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F2R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F2R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F2R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F2R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F2R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F2R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F2R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F2R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F2R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F2R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F2R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F2R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F2R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F2R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F2R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F2R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F2R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F2R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F2R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F2R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F2R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F2R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F2R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F2R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F2R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F2R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F2R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F2R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F2R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F2R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F2R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F2R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F2R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F2R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F2R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F2R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F2R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F2R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F2R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F2R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F3R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F3R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F3R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F3R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F3R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F3R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F3R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F3R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F3R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F3R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F3R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F3R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F3R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F3R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F3R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F3R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F3R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F3R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F3R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F3R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F3R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F3R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F3R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F3R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F3R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F3R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F3R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F3R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F3R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F3R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F3R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F3R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F3R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F3R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F3R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F3R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F3R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F3R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F3R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F3R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F3R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F3R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F3R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F3R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F3R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F3R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F3R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F3R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F3R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F3R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F3R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F3R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F3R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F3R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F3R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F3R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F3R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F3R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F3R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F3R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F3R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F3R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F3R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F3R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F4R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F4R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F4R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F4R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F4R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F4R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F4R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F4R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F4R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F4R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F4R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F4R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F4R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F4R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F4R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F4R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F4R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F4R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F4R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F4R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F4R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F4R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F4R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F4R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F4R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F4R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F4R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F4R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F4R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F4R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F4R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F4R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F4R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F4R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F4R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F4R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F4R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F4R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F4R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F4R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F4R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F4R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F4R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F4R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F4R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F4R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F4R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F4R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F4R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F4R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F4R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F4R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F4R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F4R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F4R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F4R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F4R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F4R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F4R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F4R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F4R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F4R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F4R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F4R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F5R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F5R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F5R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F5R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F5R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F5R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F5R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F5R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F5R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F5R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F5R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F5R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F5R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F5R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F5R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F5R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F5R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F5R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F5R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F5R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F5R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F5R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F5R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F5R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F5R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F5R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F5R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F5R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F5R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F5R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F5R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F5R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F5R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F5R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F5R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F5R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F5R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F5R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F5R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F5R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F5R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F5R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F5R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F5R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F5R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F5R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F5R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F5R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F5R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F5R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F5R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F5R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F5R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F5R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F5R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F5R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F5R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F5R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F5R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F5R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F5R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F5R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F5R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F5R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F6R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F6R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F6R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F6R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F6R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F6R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F6R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F6R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F6R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F6R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F6R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F6R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F6R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F6R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F6R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F6R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F6R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F6R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F6R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F6R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F6R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F6R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F6R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F6R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F6R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F6R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F6R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F6R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F6R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F6R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F6R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F6R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F6R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F6R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F6R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F6R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F6R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F6R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F6R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F6R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F6R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F6R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F6R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F6R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F6R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F6R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F6R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F6R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F6R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F6R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F6R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F6R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F6R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F6R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F6R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F6R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F6R2_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F6R2_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F6R2_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F6R2_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F6R2_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F6R2_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F6R2_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F6R2_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F7R1_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F7R1_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F7R1_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F7R1_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F7R1_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F7R1_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F7R1_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F7R1_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F7R1_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F7R1_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F7R1_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F7R1_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F7R1_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F7R1_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F7R1_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F7R1_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F7R1_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F7R1_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F7R1_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F7R1_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F7R1_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F7R1_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F7R1_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F7R1_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F7R1_FB30 ((uint32_t)0x40000000) |

| #define | CAN_F7R1_FB31 ((uint32_t)0x80000000) |

| #define | CAN_F7R1_FB4 ((uint32_t)0x00000010) |

| #define | CAN_F7R1_FB5 ((uint32_t)0x00000020) |

| #define | CAN_F7R1_FB6 ((uint32_t)0x00000040) |

| #define | CAN_F7R1_FB7 ((uint32_t)0x00000080) |

| #define | CAN_F7R1_FB8 ((uint32_t)0x00000100) |

| #define | CAN_F7R1_FB9 ((uint32_t)0x00000200) |

| #define | CAN_F7R2_FB0 ((uint32_t)0x00000001) |

| #define | CAN_F7R2_FB1 ((uint32_t)0x00000002) |

| #define | CAN_F7R2_FB10 ((uint32_t)0x00000400) |

| #define | CAN_F7R2_FB11 ((uint32_t)0x00000800) |

| #define | CAN_F7R2_FB12 ((uint32_t)0x00001000) |

| #define | CAN_F7R2_FB13 ((uint32_t)0x00002000) |

| #define | CAN_F7R2_FB14 ((uint32_t)0x00004000) |

| #define | CAN_F7R2_FB15 ((uint32_t)0x00008000) |

| #define | CAN_F7R2_FB16 ((uint32_t)0x00010000) |

| #define | CAN_F7R2_FB17 ((uint32_t)0x00020000) |

| #define | CAN_F7R2_FB18 ((uint32_t)0x00040000) |

| #define | CAN_F7R2_FB19 ((uint32_t)0x00080000) |

| #define | CAN_F7R2_FB2 ((uint32_t)0x00000004) |

| #define | CAN_F7R2_FB20 ((uint32_t)0x00100000) |

| #define | CAN_F7R2_FB21 ((uint32_t)0x00200000) |

| #define | CAN_F7R2_FB22 ((uint32_t)0x00400000) |

| #define | CAN_F7R2_FB23 ((uint32_t)0x00800000) |

| #define | CAN_F7R2_FB24 ((uint32_t)0x01000000) |

| #define | CAN_F7R2_FB25 ((uint32_t)0x02000000) |

| #define | CAN_F7R2_FB26 ((uint32_t)0x04000000) |

| #define | CAN_F7R2_FB27 ((uint32_t)0x08000000) |

| #define | CAN_F7R2_FB28 ((uint32_t)0x10000000) |

| #define | CAN_F7R2_FB29 ((uint32_t)0x20000000) |

| #define | CAN_F7R2_FB3 ((uint32_t)0x00000008) |

| #define | CAN_F7R2_FB30 ((uint32_t)0x40000000) |